JESD_SUBCHIP Register Map

www.ti.com

252

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

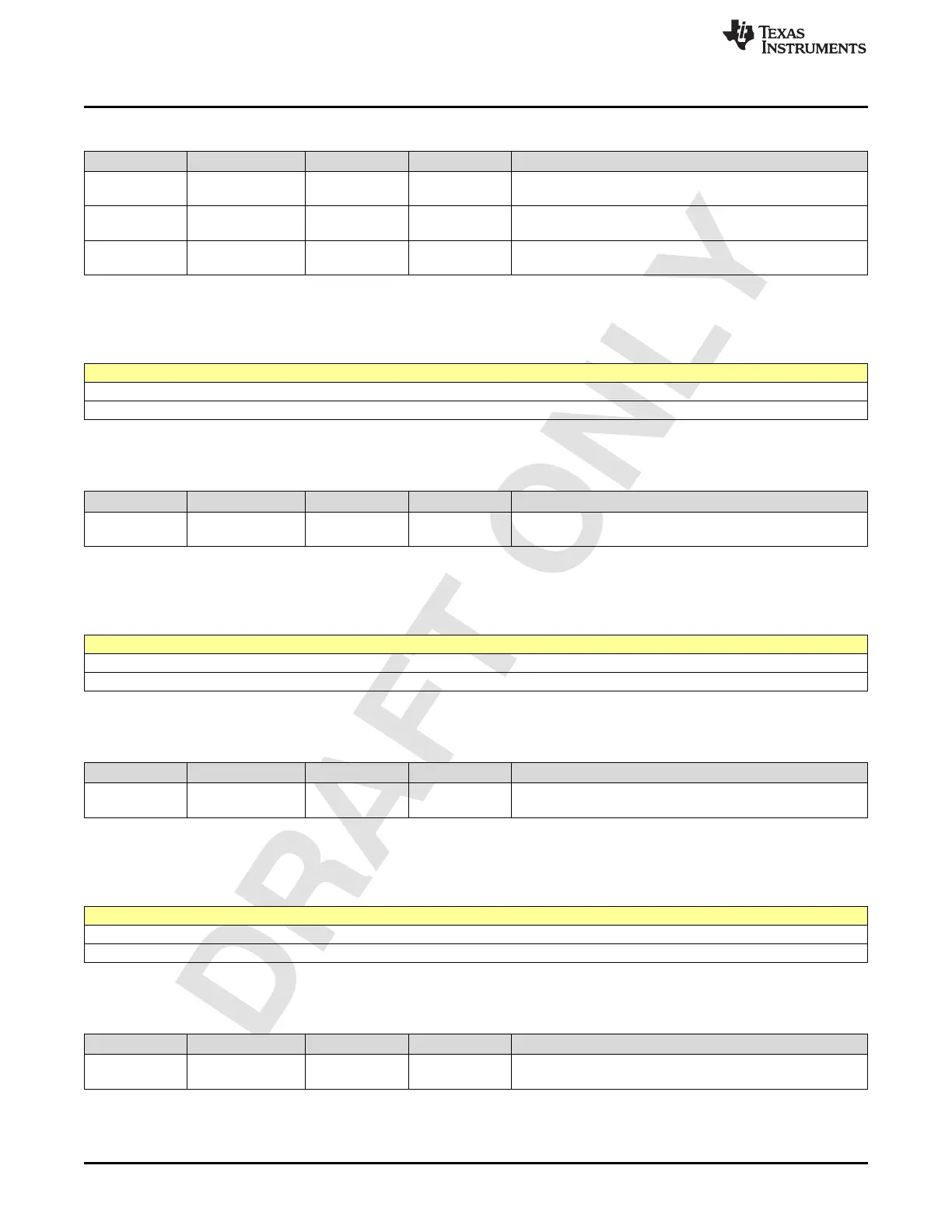

Table 2-220. Register 195 Field Descriptions (continued)

Bit Field Type Reset Description

2-2 DBG_TX_ON_C R 0h

Sig-valid from TDD controller is assigned to this status

register, post synchronizer

1-1 DBG_TX_ON_B R 0h

Sig-valid from TDD controller is assigned to this status

register, post synchronizer

0-0 DBG_TX_ON_A R 0h

Sig-valid from TDD controller is assigned to this status

register, post synchronizer

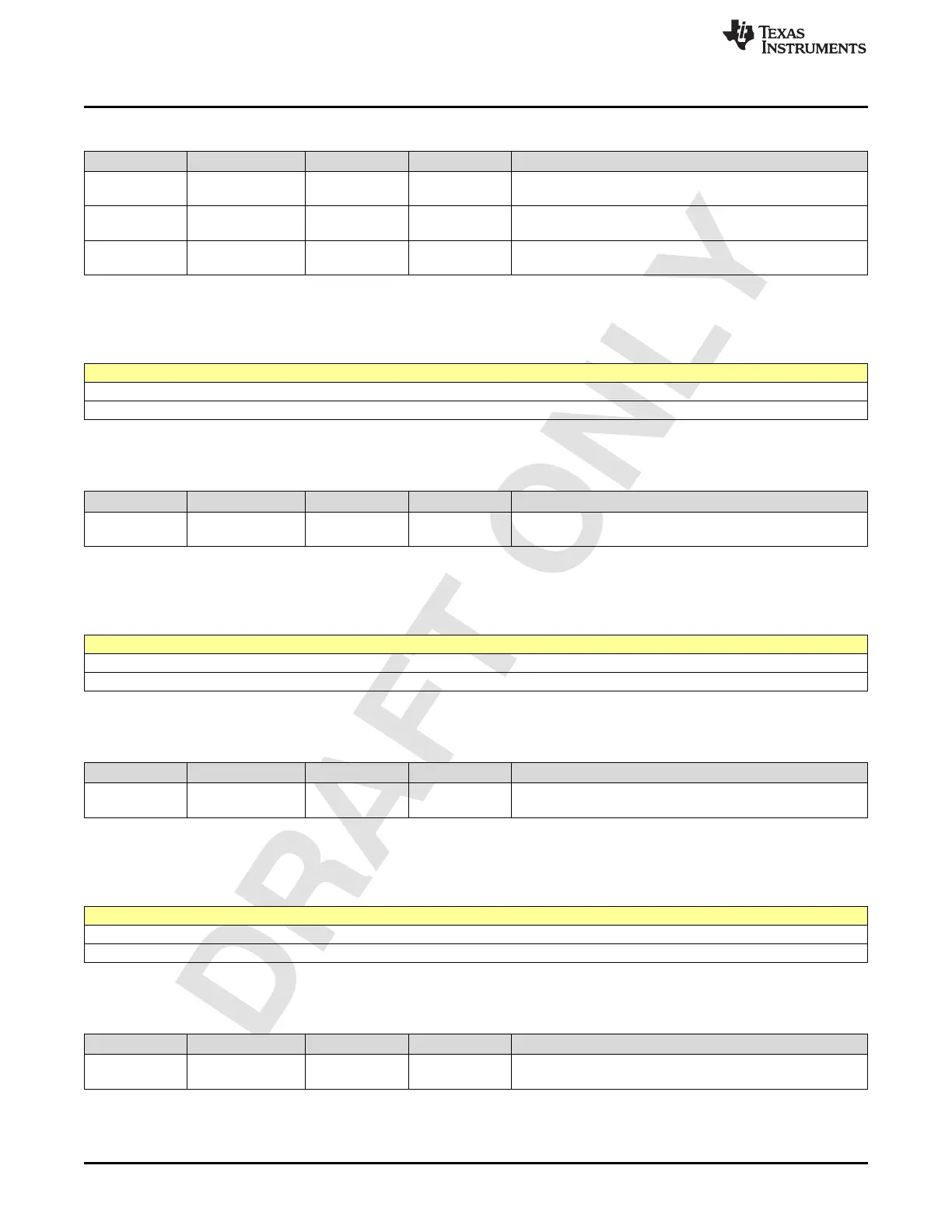

2.3.177 Register 19Ch (offset = 19Ch) [reset = 0h]

Figure 2-218. Register 19Ch

7 6 5 4 3 2 1 0

SPARE_OUT_REG0

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-221. Register 19C Field Descriptions

Bit Field Type Reset Description

7-0

SPARE_OUT_REG

0

R/W 0h spare registers out

2.3.178 Register 19Dh (offset = 19Dh) [reset = 0h]

Figure 2-219. Register 19Dh

7 6 5 4 3 2 1 0

SPARE_OUT_REG1

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-222. Register 19D Field Descriptions

Bit Field Type Reset Description

7-0

SPARE_OUT_REG

1

R/W 0h spare registers out

2.3.179 Register 19Eh (offset = 19Eh) [reset = 0h]

Figure 2-220. Register 19Eh

7 6 5 4 3 2 1 0

SPARE_OUT_REG2

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-223. Register 19E Field Descriptions

Bit Field Type Reset Description

7-0

SPARE_OUT_REG

2

R/W 0h spare registers out

Loading...

Loading...