www.ti.com

SERDES Register Map

469

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-725. Register 4004 Field Descriptions

Bit Field Type Reset Description

7-0

CNTR_TARGET_P

AT[7:0]

R/W 20h

Valid_pattern_cntr_target for error rate target with format

U12.0.

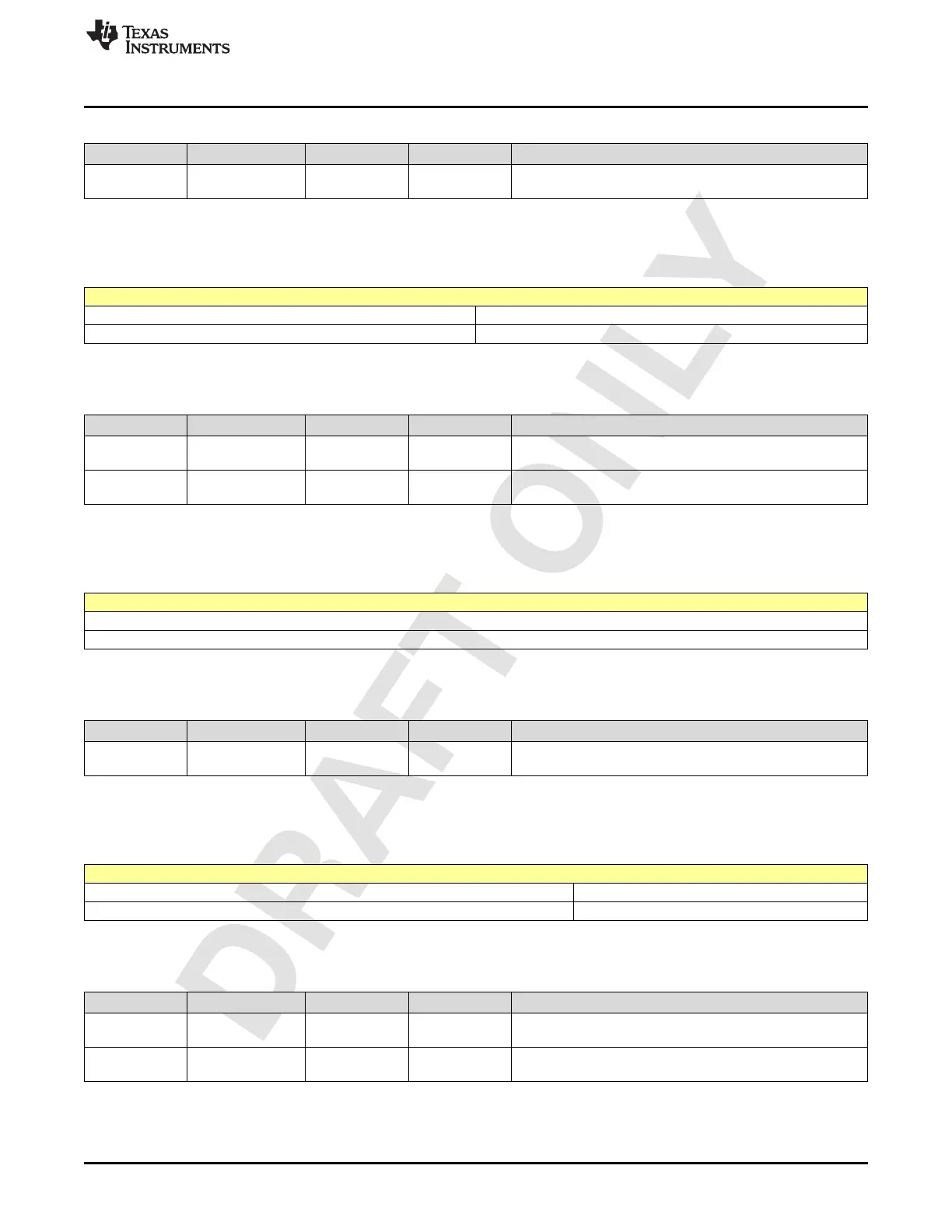

2.6.6 Register 4005h (offset = 4005h) [reset = 60h]

Figure 2-720. Register 4005h

7 6 5 4 3 2 1 0

DAC_SETTLE_TIME CNTR_TARGET_PAT[11:8]

R/W-6h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-726. Register 4005 Field Descriptions

Bit Field Type Reset Description

7-4

DAC_SETTLE_TIM

E

R/W 6h

Controls the DAC settling wait period for internal statistical

monitor. The period equal 2^(m-1) state machine cycles.

3-0

CNTR_TARGET_P

AT[11:8]

R/W 0h

Valid_pattern_cntr_target for error rate target with format

U12.0.

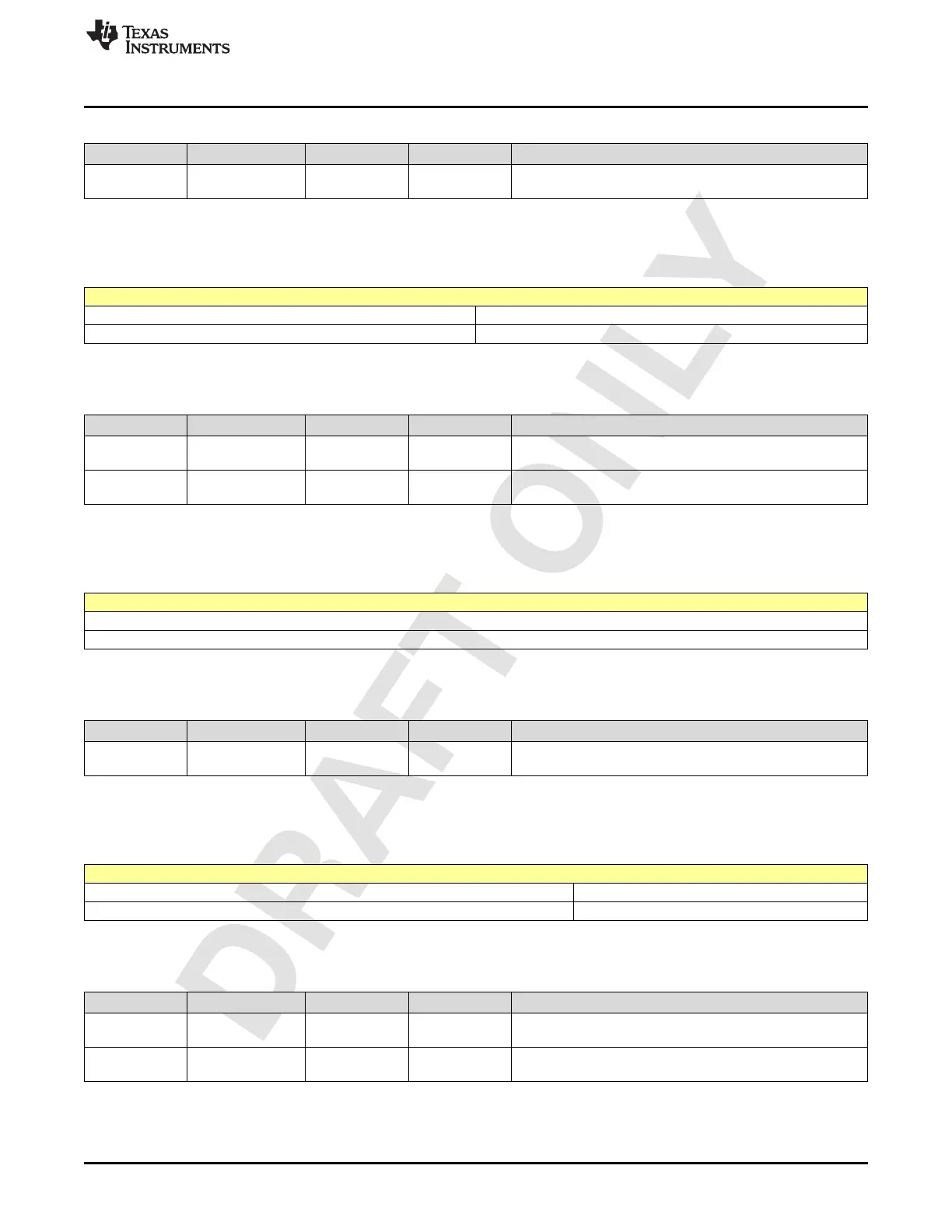

2.6.7 Register 4006h (offset = 4006h) [reset = 66h]

Figure 2-721. Register 4006h

7 6 5 4 3 2 1 0

RX_SD_THRESH_DETECT[7:0]

R/W-66h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-727. Register 4006 Field Descriptions

Bit Field Type Reset Description

7-0

RX_SD_THRESH_

DETECT[7:0]

R/W 66h

Signal detect threshold level of format U11.11. This is an

unsigned number and each bit is equivalent to 0.4mV.

2.6.8 Register 4007h (offset = 4007h) [reset = 7Bh]

Figure 2-722. Register 4007h

7 6 5 4 3 2 1 0

TIMER_COUNT RX_SD_THRESH_DETECT[10:8]

R/W-Fh R/W-3h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-728. Register 4007 Field Descriptions

Bit Field Type Reset Description

7-3 TIMER_COUNT R/W Fh

The timer for initial timing acquisition in the format for 2^(m-1)

state machine cycles.

2-0

RX_SD_THRESH_

DETECT[10:8]

R/W 3h

Signal detect threshold level of format U11.11. This is an

unsigned number and each bit is equivalent to 0.4mV.

Loading...

Loading...