www.ti.com

FB Top Register Map

957

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

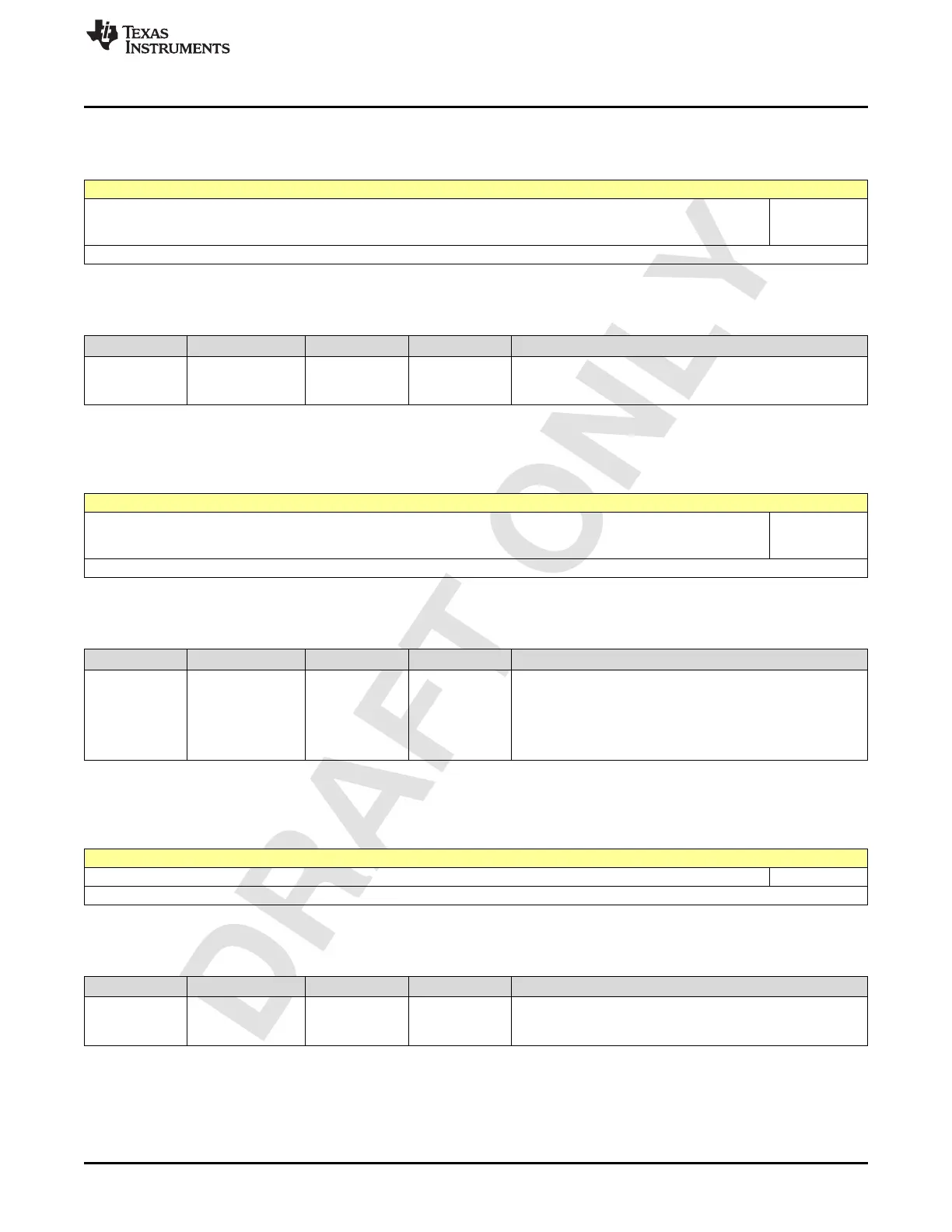

2.14.319 Register 740h (offset = 740h) [reset = 1h]

Figure 2-2202. Register 740h

7 6 5 4 3 2 1 0

FB_DDC_ROO

T_CLOCK_GA

TE

R/W-1h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2216. Register 740 Field Descriptions

Bit Field Type Reset Description

0-0

FB_DDC_ROOT_C

LOCK_GATE

R/W 1h

Gate/ungate the root clock to the FB digital.

0: Ungate

1: Gate

2.14.320 Register 741h (offset = 741h) [reset = 0h]

Figure 2-2203. Register 741h

7 6 5 4 3 2 1 0

FB_DDC_USE

_RX_ROOT_C

LOCK

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2217. Register 741 Field Descriptions

Bit Field Type Reset Description

0-0

FB_DDC_USE_RX

_ROOT_CLOCK

R/W 0h

Use RX digital root clock for FB. Useful when RX and FB ADC

rates are the same. The System Configuration Macros

automatically engage such power savings hooks, and are

hence strongly recommended.

0 : Use clk generated from FB

1 : Use clk coming frm Rx

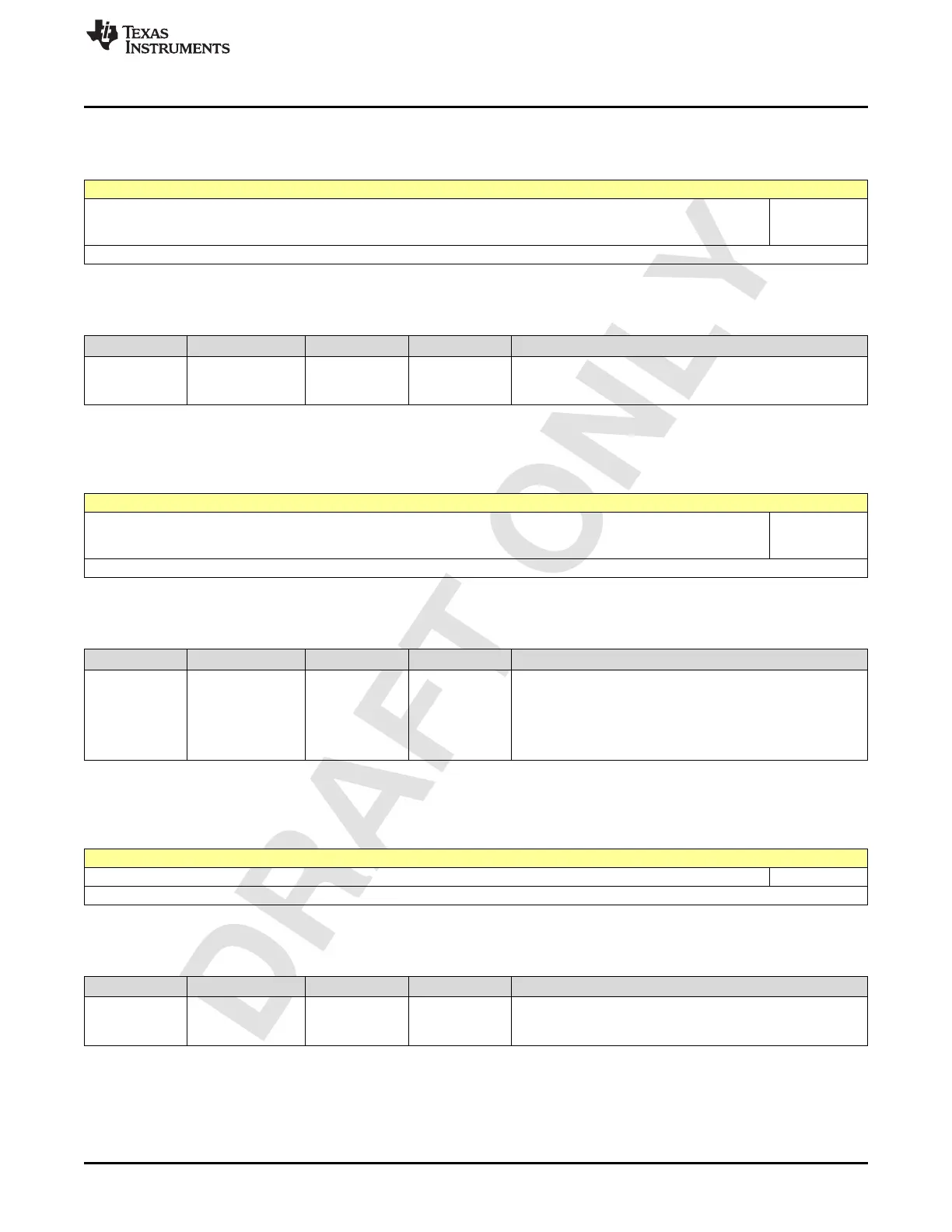

2.14.321 Register 770h (offset = 770h) [reset = 0h]

Figure 2-2204. Register 770h

7 6 5 4 3 2 1 0

FB_DDC_PDN

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2218. Register 770 Field Descriptions

Bit Field Type Reset Description

0-0 FB_DDC_PDN R/W 0h

Power down the complete FB channel

1 : Power Down FB

0 : Enable FB

Loading...

Loading...