www.ti.com

JESD_SUBCHIP Register Map

245

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

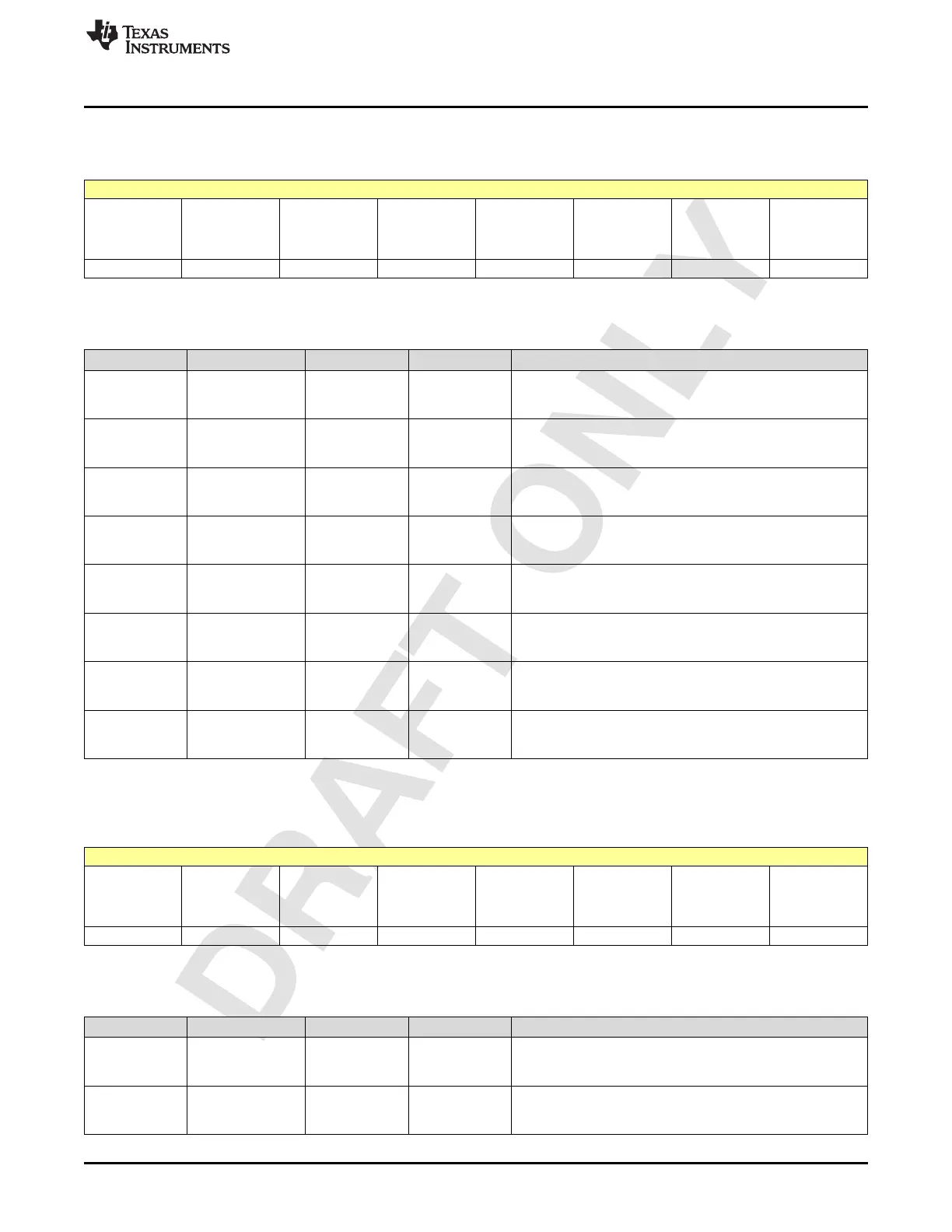

2.3.157 Register 175h (offset = 175h) [reset = 0h]

Figure 2-198. Register 175h

7 6 5 4 3 2 1 0

DBG_RXD_AFI

FO_RD_CLK_T

OGGLE_STICK

Y

DBG_RXD_AFI

FO_WR_CLK_

TOGGLE_STIC

KY

DBG_RXD_AFI

FO_SYS_REF_

RD_STICKY

DBG_RXD_AFI

FO_SYS_REF_

WR_STICKY

DBG_RXC_AFI

FO_RD_CLK_T

OGGLE_STICK

Y

DBG_RXC_AFI

FO_WR_CLK_

TOGGLE_STIC

KY

DBG_RXC_AFI

FO_SYS_REF_

RD_STICKY

DBG_RXC_AFI

FO_SYS_REF_

WR_STICKY

R-0h R-0h R-0h R-0h R-0h R-0h R-0h R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-201. Register 175 Field Descriptions

Bit Field Type Reset Description

7-7

DBG_RXD_AFIFO

_RD_CLK_TOGGL

E_STICKY

R 0h RXD to JESD Async FIFO rd-clk monitor

6-6

DBG_RXD_AFIFO

_WR_CLK_TOGGL

E_STICKY

R 0h RXD to JESD Async FIFO wr-clk monitor

5-5

DBG_RXD_AFIFO

_SYS_REF_RD_S

TICKY

R 0h RXD to JESD Async FIFO rd-sysref monitor

4-4

DBG_RXD_AFIFO

_SYS_REF_WR_S

TICKY

R 0h RXD to JESD Async FIFO wr-sysref monitor

3-3

DBG_RXC_AFIFO

_RD_CLK_TOGGL

E_STICKY

R 0h RXC to JESD Async FIFO rd-clk monitor

2-2

DBG_RXC_AFIFO

_WR_CLK_TOGGL

E_STICKY

R 0h RXC to JESD Async FIFO wr-clk monitor

1-1

DBG_RXC_AFIFO

_SYS_REF_RD_S

TICKY

R 0h RXC to JESD Async FIFO rd-sysref monitor

0-0

DBG_RXC_AFIFO

_SYS_REF_WR_S

TICKY

R 0h RXC to JESD Async FIFO wr-sysref monitor

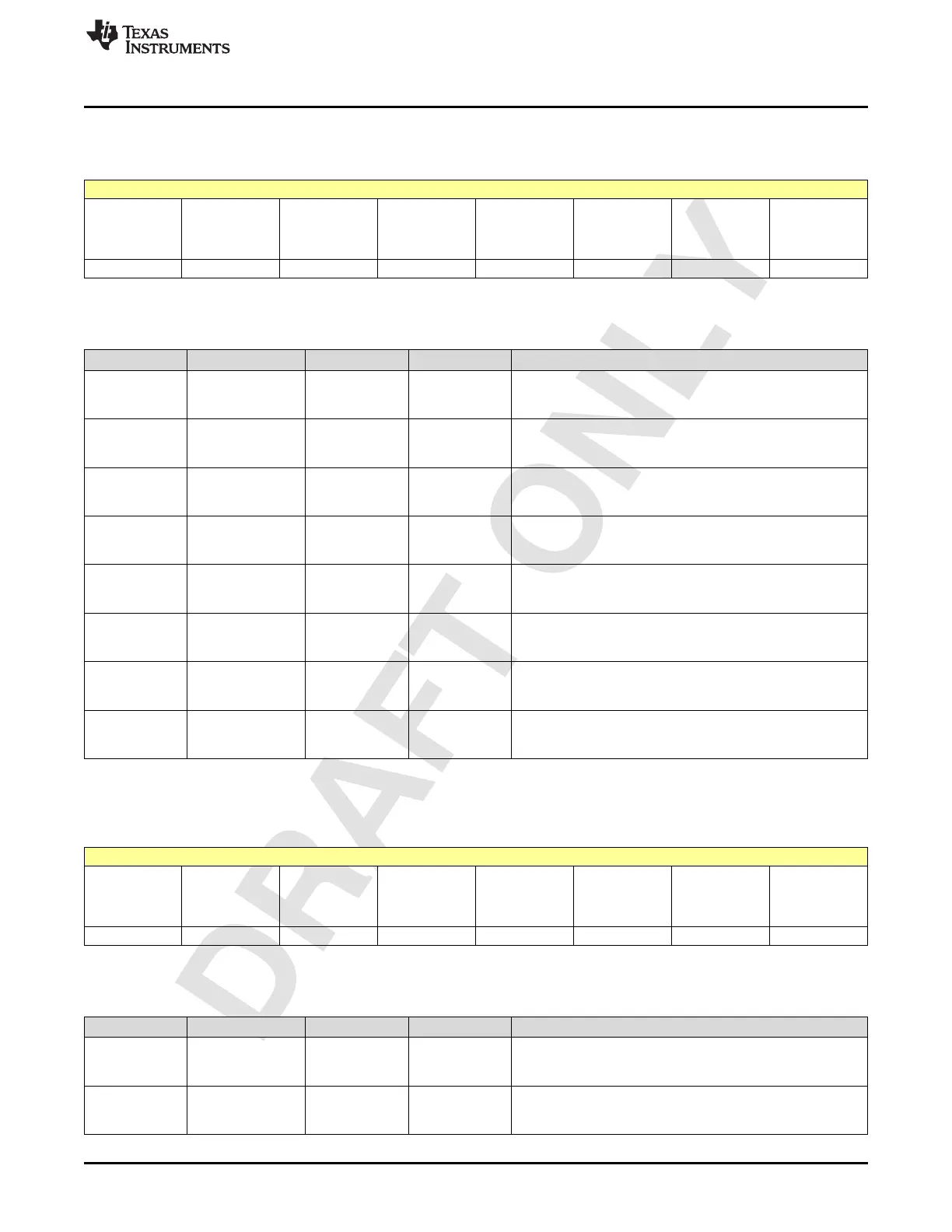

2.3.158 Register 176h (offset = 176h) [reset = 0h]

Figure 2-199. Register 176h

7 6 5 4 3 2 1 0

DBG_FBCD_A

FIFO_RD_CLK

_TOGGLE_STI

CKY

DBG_FBCD_A

FIFO_WR_CLK

_TOGGLE_STI

CKY

DBG_FBCD_A

FIFO_SYS_RE

F_RD_STICKY

DBG_FBCD_A

FIFO_SYS_RE

F_WR_STICKY

DBG_FBAB_A

FIFO_RD_CLK

_TOGGLE_STI

CKY

DBG_FBAB_A

FIFO_WR_CLK

_TOGGLE_STI

CKY

DBG_FBAB_A

FIFO_SYS_RE

F_RD_STICKY

DBG_FBAB_A

FIFO_SYS_RE

F_WR_STICKY

R-0h R-0h R-0h R-0h R-0h R-0h R-0h R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-202. Register 176 Field Descriptions

Bit Field Type Reset Description

7-7

DBG_FBCD_AFIF

O_RD_CLK_TOGG

LE_STICKY

R 0h FBCD to JESD Async FIFO rd-clk monitor

6-6

DBG_FBCD_AFIF

O_WR_CLK_TOG

GLE_STICKY

R 0h FBCD to JESD Async FIFO wr-clk monitor

Loading...

Loading...