JESD_SUBCHIP Register Map

www.ti.com

168

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

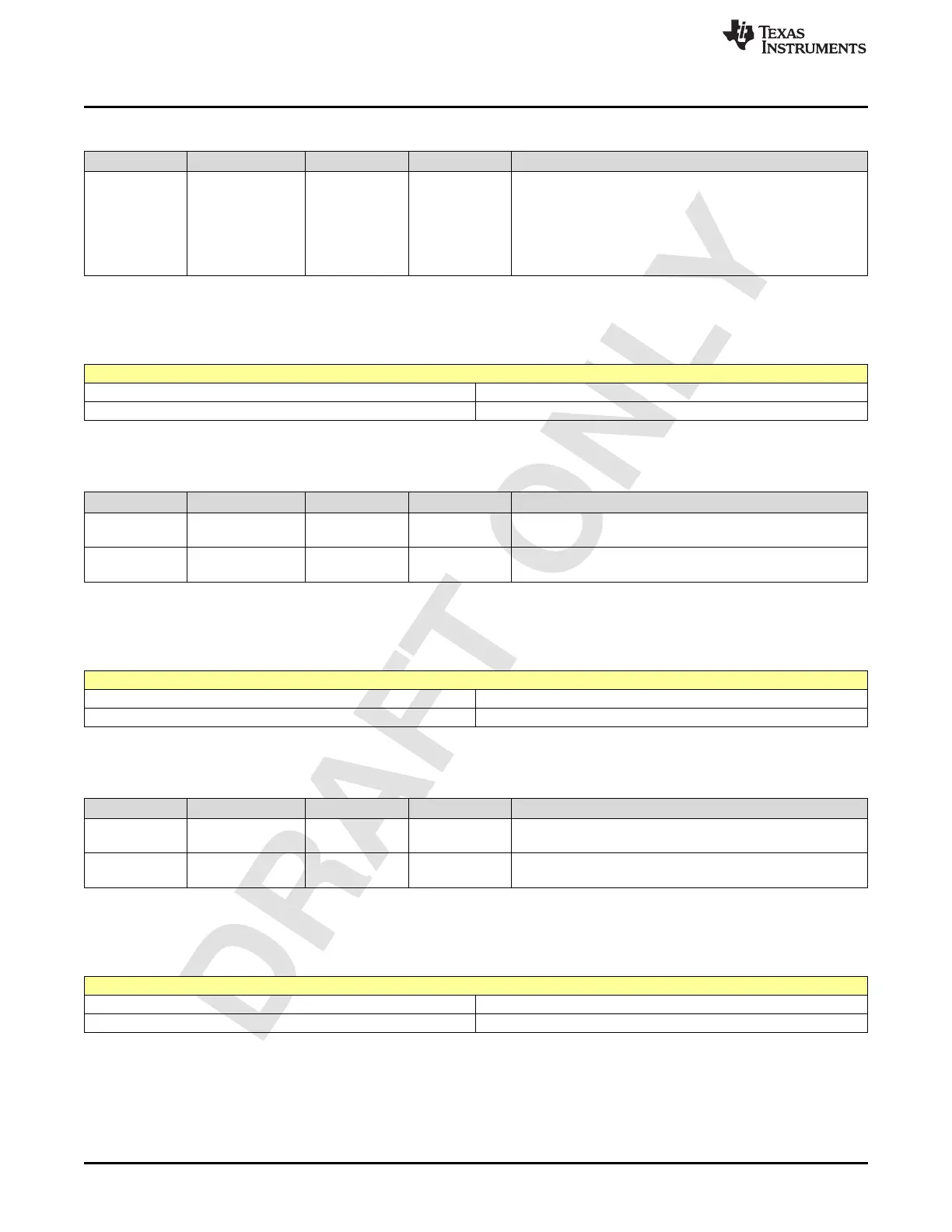

Table 2-57. Register 2F Field Descriptions (continued)

Bit Field Type Reset Description

1-1

MUX_OVR_FOR_

DUC_CLK

R/W 0h

FOR LOW POWER CONSUMPTION:

(To switch off 2T_CD instance clocks completely if all the data

comes from the 4-lanes of 2T-AB instance).Use this mux

select to use the other register bits

'mux_sel_for_duc_txa_to_txb_clk',

'mux_sel_for_duc_txb_to_txc_clk',

'mux_sel_for_duc_txb_to_txd_clk' .

2.3.14 Register 30h (offset = 30h) [reset = 88h]

Figure 2-55. Register 30h

7 6 5 4 3 2 1 0

RXB_AFIFO_OFFSET RXA_AFIFO_OFFSET

R/W-8h R/W-8h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-58. Register 30 Field Descriptions

Bit Field Type Reset Description

7-4

RXB_AFIFO_OFFS

ET

R/W 8h RRF to JESD ASYNC FIFO offset for RXB DATA

3-0

RXA_AFIFO_OFFS

ET

R/W 8h RRF to JESD ASYNC FIFO offset for RXA DATA

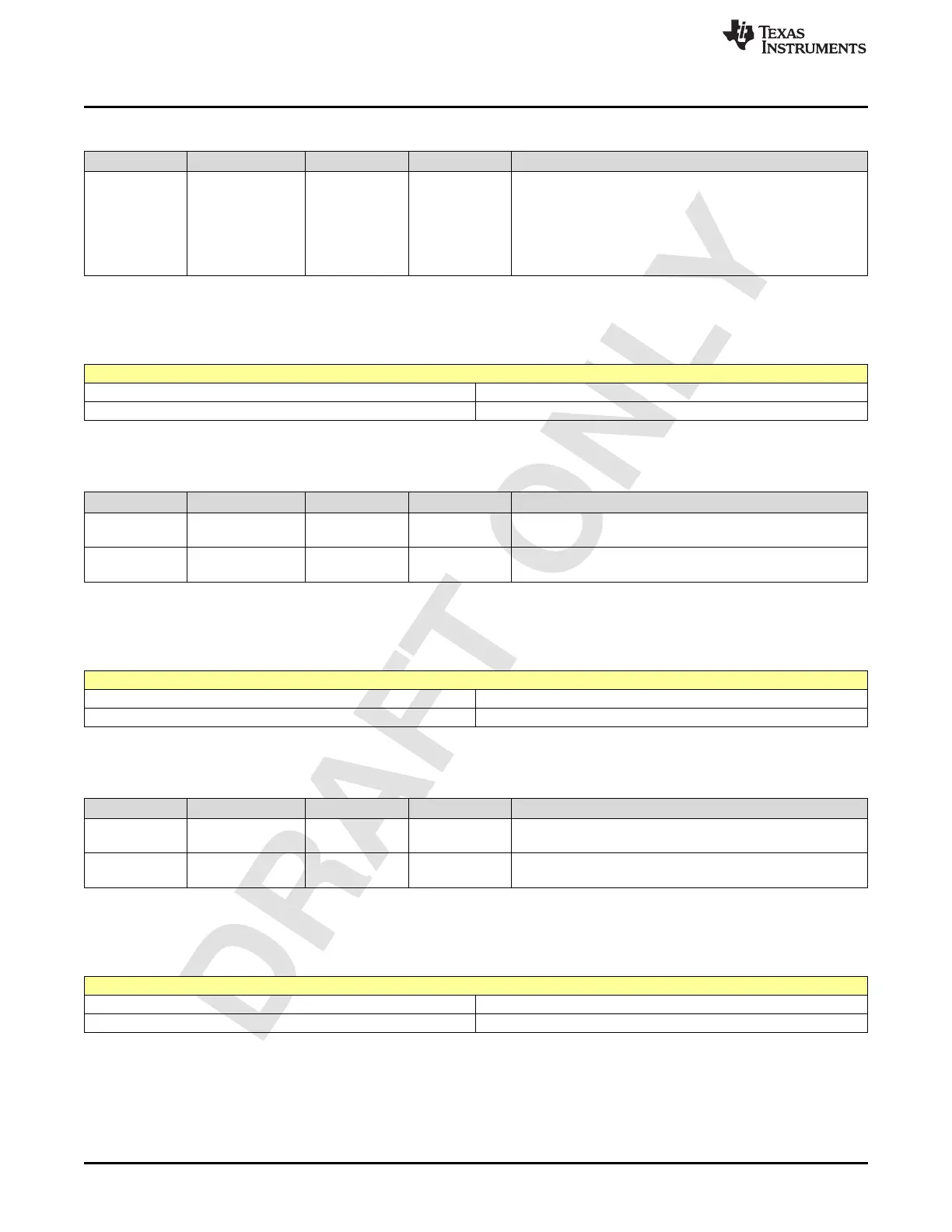

2.3.15 Register 31h (offset = 31h) [reset = 88h]

Figure 2-56. Register 31h

7 6 5 4 3 2 1 0

RXD_AFIFO_OFFSET RXC_AFIFO_OFFSET

R/W-8h R/W-8h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-59. Register 31 Field Descriptions

Bit Field Type Reset Description

7-4

RXD_AFIFO_OFF

SET

R/W 8h RRF to JESD ASYNC FIFO offset for RXD DATA

3-0

RXC_AFIFO_OFF

SET

R/W 8h RRF to JESD ASYNC FIFO offset for RXC DATA

2.3.16 Register 32h (offset = 32h) [reset = 88h]

Figure 2-57. Register 32h

7 6 5 4 3 2 1 0

FBCD_AFIFO_OFFSET FBAB_AFIFO_OFFSET

R/W-8h R/W-8h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...