www.ti.com

DAC JESD Register Map

273

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

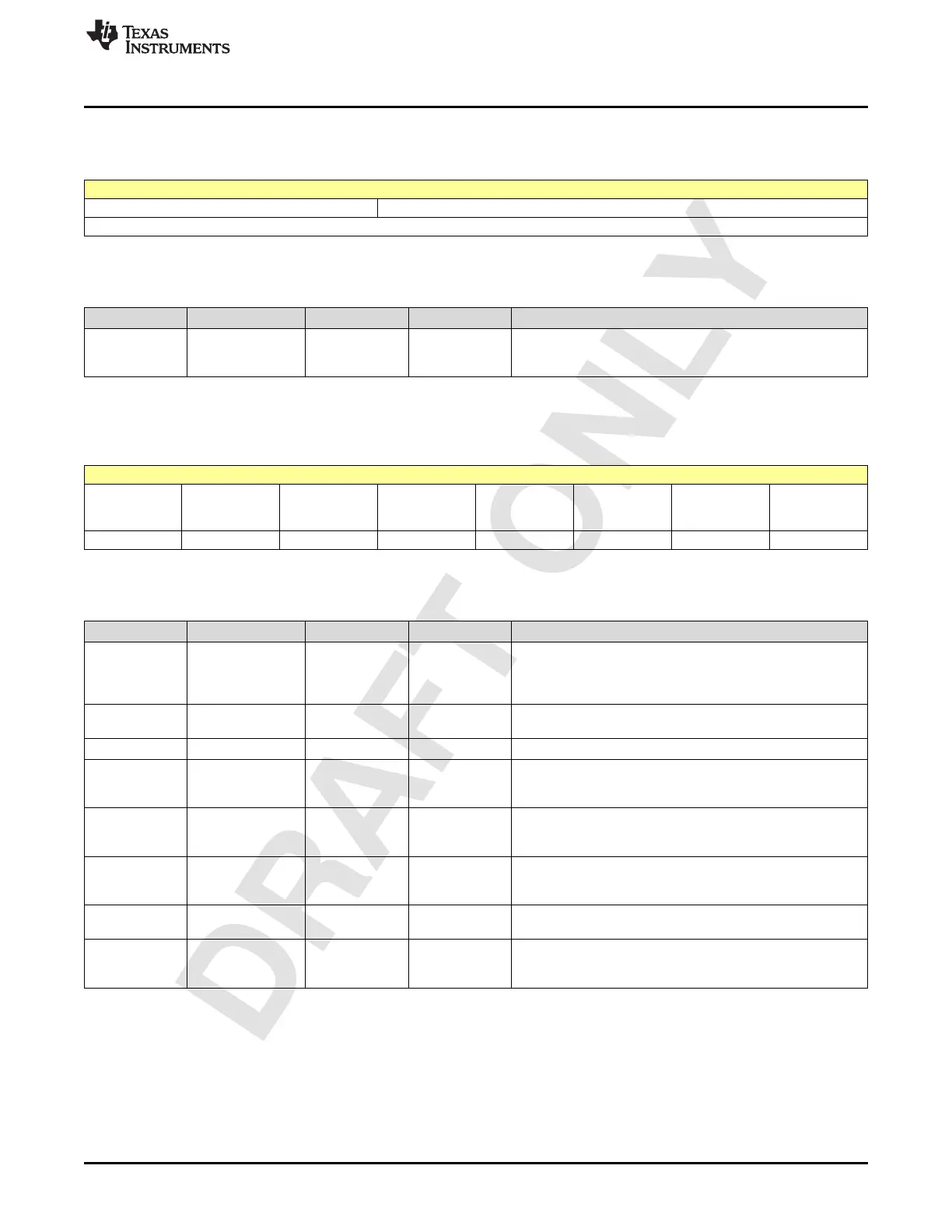

2.4.24 Register 37h (offset = 37h) [reset = 0h]

Figure 2-253. Register 37h

7 6 5 4 3 2 1 0

JESD_CLK_TX2_DIV_N_M1

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-257. Register 37 Field Descriptions

Bit Field Type Reset Description

4-0

JESD_CLK_TX2_D

IV_N_M1

R/W 0h

For lanes[2:3]/[6:7], N_M1 value in Divide ratio of M/N for

generating the JESD_RX_CLK for DAC_JESD from

ROOT_CLK.

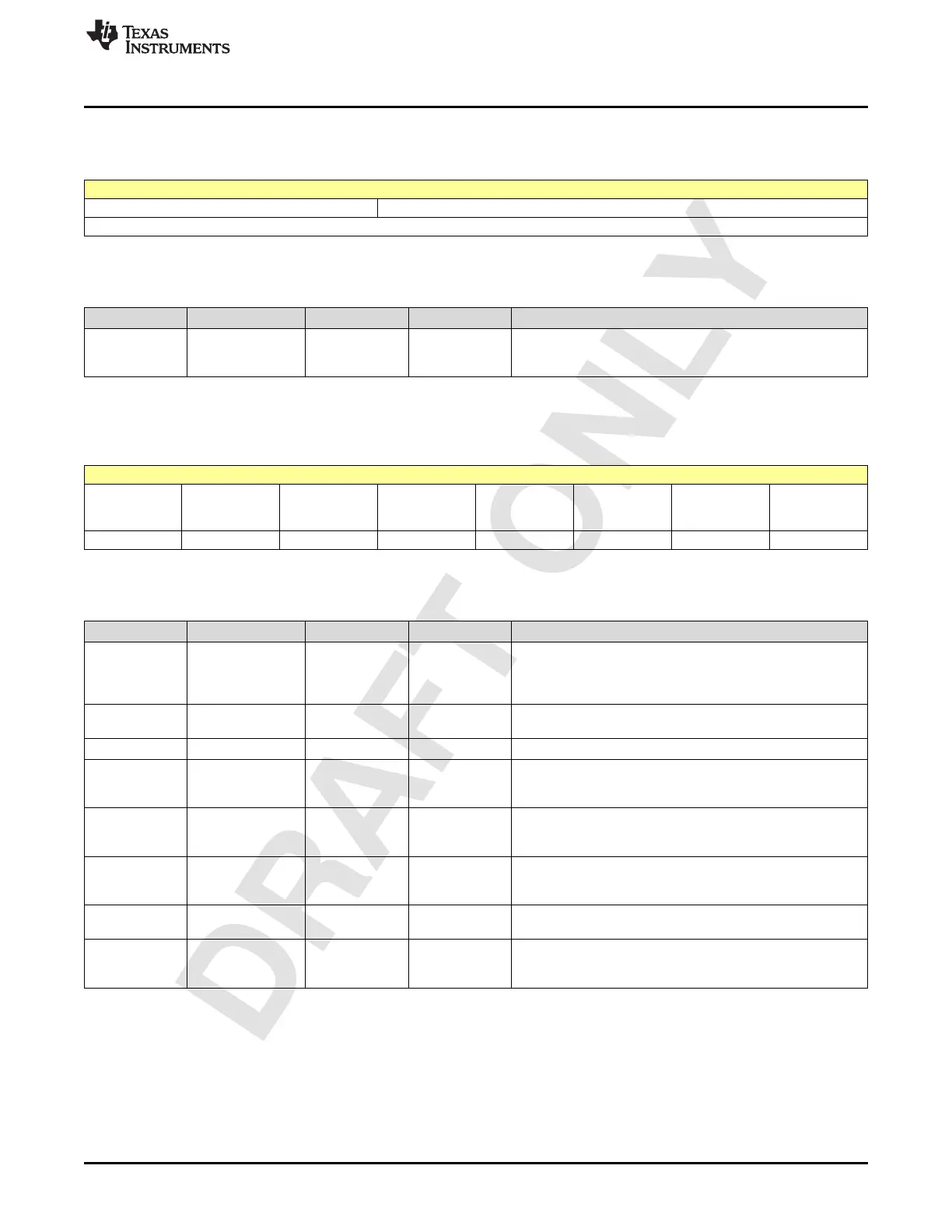

2.4.25 Register 38h (offset = 38h) [reset = 1Fh]

Figure 2-254. Register 38h

7 6 5 4 3 2 1 0

CLK_DIV_LFS

R_SEED_LOA

D

SPI_SYSREF_

OVERRIDE

SPI_SYSREF JESD_CLK_DI

V2_DIV_DITHE

R_EN

JESD_CLK_DI

V_DITHER_EN

DUC_CLK_DIV

_DITHER_EN

DUC_CLK_IO_

DIV_DITHER_

EN

TX_ROOT_CL

K_DIV_DITHE

R_EN

R/W-0h R/W-0h R/W-0h R/W-1h R/W-1h R/W-1h R/W-1h R/W-1h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-258. Register 38 Field Descriptions

Bit Field Type Reset Description

7-7

CLK_DIV_LFSR_S

EED_LOAD

R/W 0h

LFSR load override to load lfsr_seed_val into the LFSR

module. To be used along with clk_div_lfsr_seed_val.

0 : load disable

1 : load enable

6-6

SPI_SYSREF_OV

ERRIDE

R/W 0h UNUSED

5-5 SPI_SYSREF R/W 0h UNUSED

4-4

JESD_CLK_DIV2_

DIV_DITHER_EN

R/W 1h

JESD_RD_DIV2_CLK dither-en

0 : Dither Disable

1 : Dither Enable

3-3

JESD_CLK_DIV_D

ITHER_EN

R/W 1h

JESD_RD_CLK dither-en

0 : Dither Disable

1 : Dither Enable

2-2

DUC_CLK_DIV_DI

THER_EN

R/W 1h

DUC_WR_CLK dither-en

0 : Dither Disable

1 : Dither Enable

1-1

DUC_CLK_IO_DIV

_DITHER_EN

R/W 1h UNUSED

0-0

TX_ROOT_CLK_DI

V_DITHER_EN

R/W 1h

ROOT_CLK dither-en

0 : Dither Disable

1 : Dither Enable

Loading...

Loading...