www.ti.com

SERDES Register Map

517

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

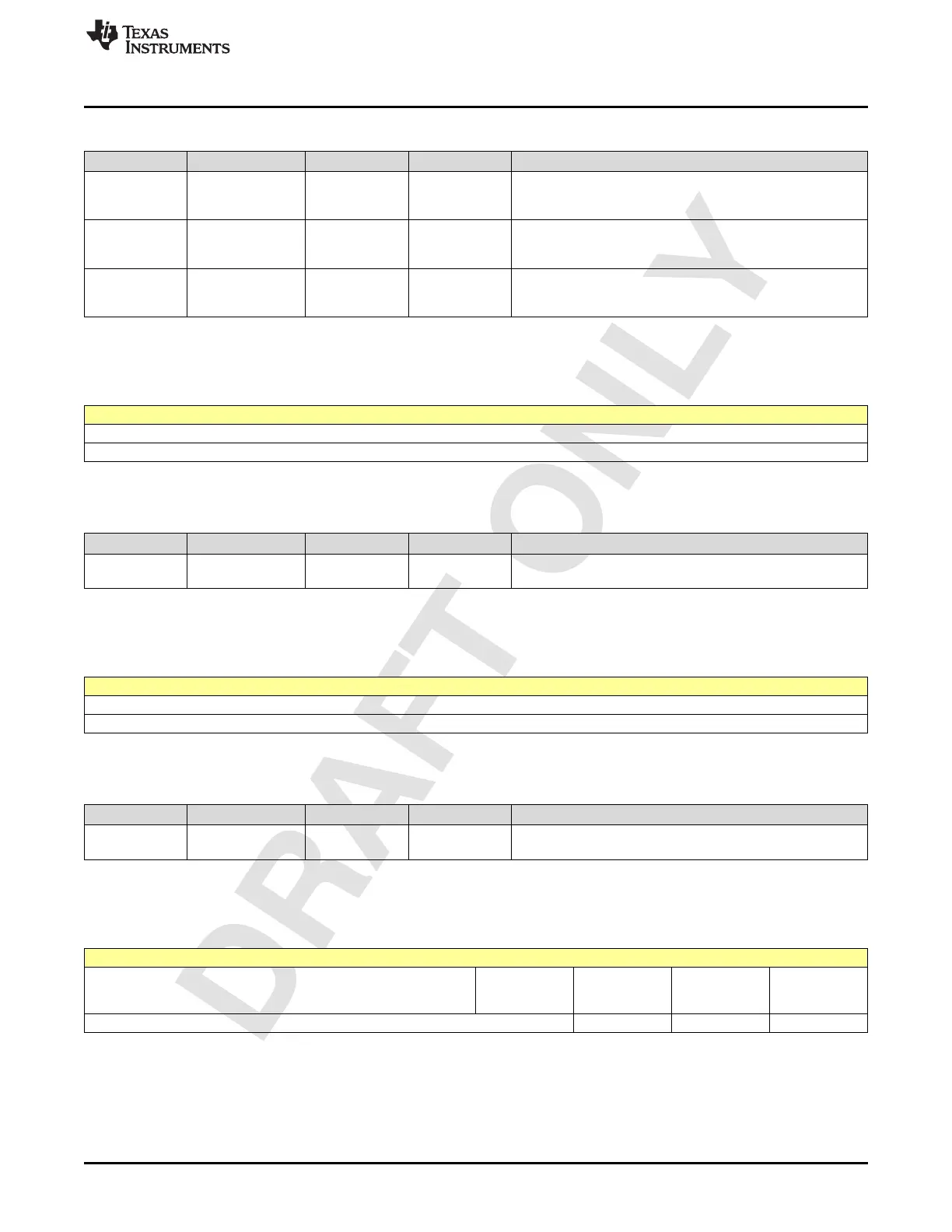

Table 2-878. Register 701E Field Descriptions (continued)

Bit Field Type Reset Description

2-2 OPTICAL_MODE R/W 0h

Optical mode

1h All CTLE are fixed to 7.

0h Normal CTLE search algorithm is applicable.

1-1

PLL_CALIBR_DON

E

R 0h

PLL calibration

1h PLL calibration is done.

0h PLL calibration is not done.

0-0

PLL_CALIBR_RES

TART

R/W 0h

PLL calibration restart

Write 1 to this bit to restart PLL calibration on next PHY link

up. This bit is self-cleaning.

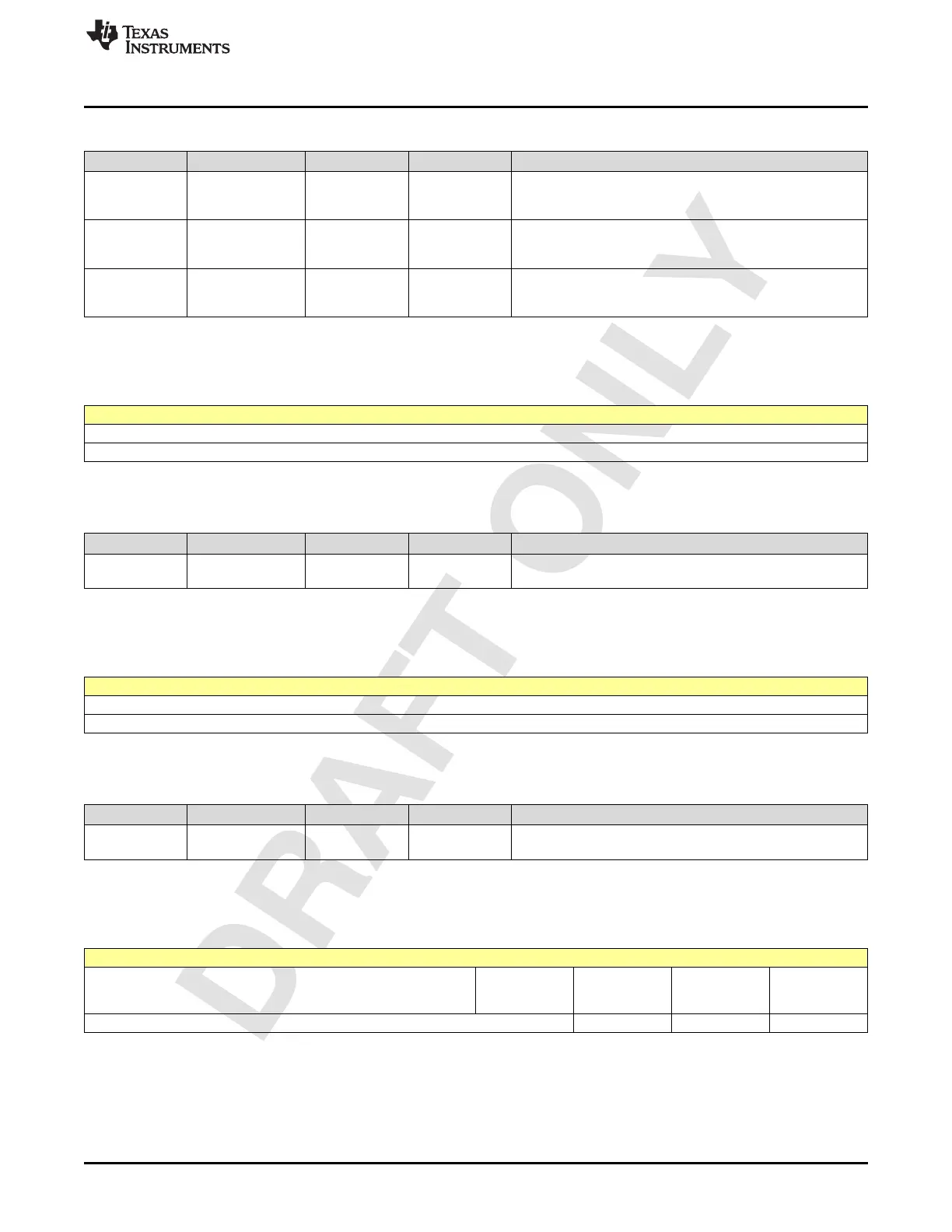

2.6.159 Register 7020h (offset = 7020h) [reset = 0h]

Figure 2-873. Register 7020h

7 6 5 4 3 2 1 0

FIRMWARE_WATCHDOG[7:0]

R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-879. Register 7020 Field Descriptions

Bit Field Type Reset Description

7-0

FIRMWARE_WAT

CHDOG[7:0]

R 0h

Contents increment by a count of 1 approximately every

second. Use to verify that firmware is operating.

2.6.160 Register 7021h (offset = 7021h) [reset = 0h]

Figure 2-874. Register 7021h

7 6 5 4 3 2 1 0

FIRMWARE_WATCHDOG[15:8]

R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-880. Register 7021 Field Descriptions

Bit Field Type Reset Description

7-0

FIRMWARE_WAT

CHDOG[15:8]

R 0h

Contents increment by a count of 1 approximately every

second. Use to verify that firmware is operating.

2.6.161 Register 7022h (offset = 7022h) [reset = 0h]

Figure 2-875. Register 7022h

7 6 5 4 3 2 1 0

CTLE_SEARC

H_DISABLE_L

N3

CTLE_SEARC

H_DISABLE_L

N2

CTLE_SEARC

H_DISABLE_L

N1

CTLE_SEARC

H_DISABLE_L

N0

R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...