www.ti.com

JESD_SUBCHIP Register Map

169

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-60. Register 32 Field Descriptions

Bit Field Type Reset Description

7-4

FBCD_AFIFO_OFF

SET

R/W 8h RRF to JESD ASYNC FIFO offset for FBCD DATA

3-0

FBAB_AFIFO_OFF

SET

R/W 8h RRF to JESD ASYNC FIFO offset for FBAB DATA

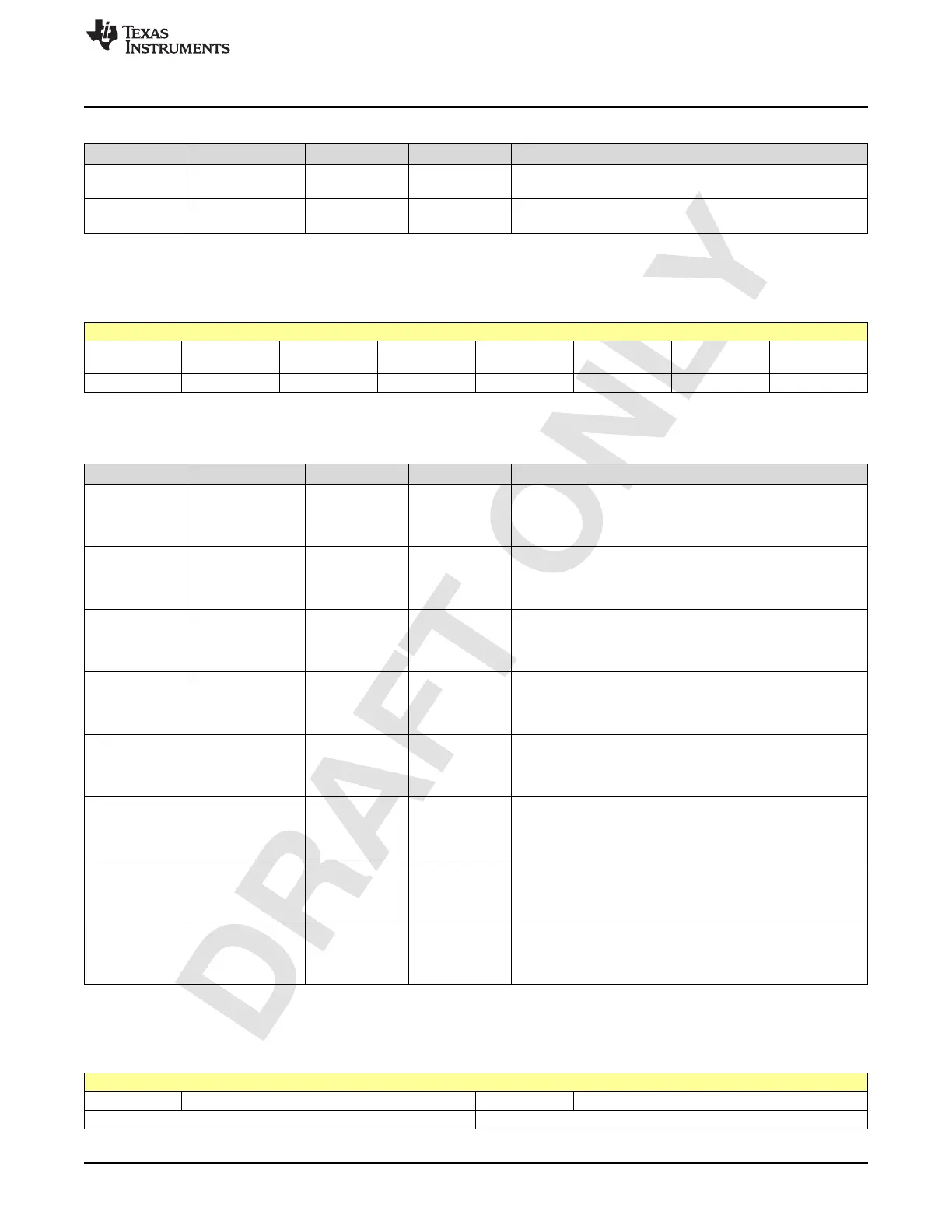

2.3.17 Register 33h (offset = 33h) [reset = 0h]

Figure 2-58. Register 33h

7 6 5 4 3 2 1 0

RXD_P2P3_CL

K_EN_OVR

RXD_P2P3_CL

K_EN_VAL

RXC_P2P3_CL

K_EN_OVR

RXC_P2P3_CL

K_EN_VAL

RXB_P2P3_CL

K_EN_OVR

RXB_P2P3_CL

K_EN_VAL

RXA_P2P3_CL

K_EN_OVR

RXA_P2P3_CL

K_EN_VAL

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-61. Register 33 Field Descriptions

Bit Field Type Reset Description

7-7

RXD_P2P3_CLK_

EN_OVR

R/W 0h

FOR LOW POWER CONSUMPTION:

Single band cases, p2, p3 streams are not valid so clocks to

the ASYNC FIFO are gated. To override the default behaviour

set this enable override register to 1

6-6

RXD_P2P3_CLK_

EN_VAL

R/W 0h

FOR LOW POWER CONSUMPTION:

When RXD_P2P3_CLK_EN_OVR is set to 1

val = 0 , p2,p3 clocks are gated.

val = 1, p2, p3 clocks are ungated

5-5

RXC_P2P3_CLK_

EN_OVR

R/W 0h

FOR LOW POWER CONSUMPTION:

Single band cases, p2, p3 streams are not valid so clocks to

the ASYNC FIFO are gated. To override the default behaviour

set this enable override register to 1

4-4

RXC_P2P3_CLK_

EN_VAL

R/W 0h

FOR LOW POWER CONSUMPTION:

When RXC_P2P3_CLK_EN_OVR is set to 1

val = 0 , p2,p3 clocks are gated.

val = 1, p2, p3 clocks are ungated

3-3

RXB_P2P3_CLK_E

N_OVR

R/W 0h

FOR LOW POWER CONSUMPTION:

Single band cases, p2, p3 streams are not valid so clocks to

the ASYNC FIFO are gated. To override the default behaviour

set this enable override register to 1

2-2

RXB_P2P3_CLK_E

N_VAL

R/W 0h

FOR LOW POWER CONSUMPTION:

When RXB_P2P3_CLK_EN_OVR is set to 1

val = 0 , p2,p3 clocks are gated.

val = 1, p2, p3 clocks are ungated

1-1

RXA_P2P3_CLK_E

N_OVR

R/W 0h

FOR LOW POWER CONSUMPTION:

Single band cases, p2, p3 streams are not valid so clocks to

the ASYNC FIFO are gated. To override the default behaviour

set this enable override register to 1

0-0

RXA_P2P3_CLK_E

N_VAL

R/W 0h

FOR LOW POWER CONSUMPTION:

When RXA_P2P3_CLK_EN_OVR is set to 1

val = 0 , p2,p3 clocks are gated.

val = 1, p2, p3 clocks are ungated

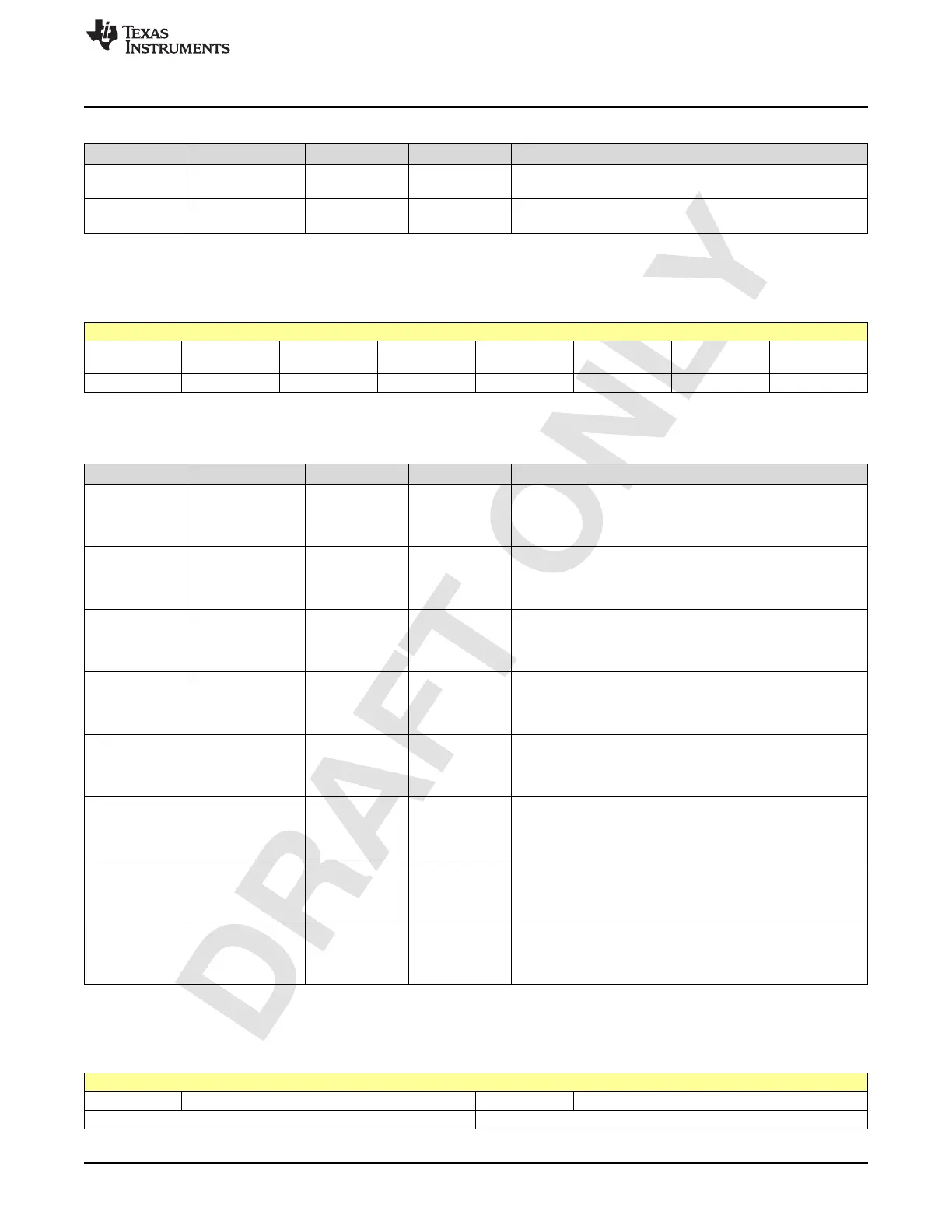

2.3.18 Register 34h (offset = 34h) [reset = 0h]

Figure 2-59. Register 34h

7 6 5 4 3 2 1 0

MUX_SEL_RXA_B1_Q_FOR_2R1F_AB MUX_SEL_RXA_B1_I_FOR_2R1F_AB

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...