www.ti.com

SERDES Register Map

515

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

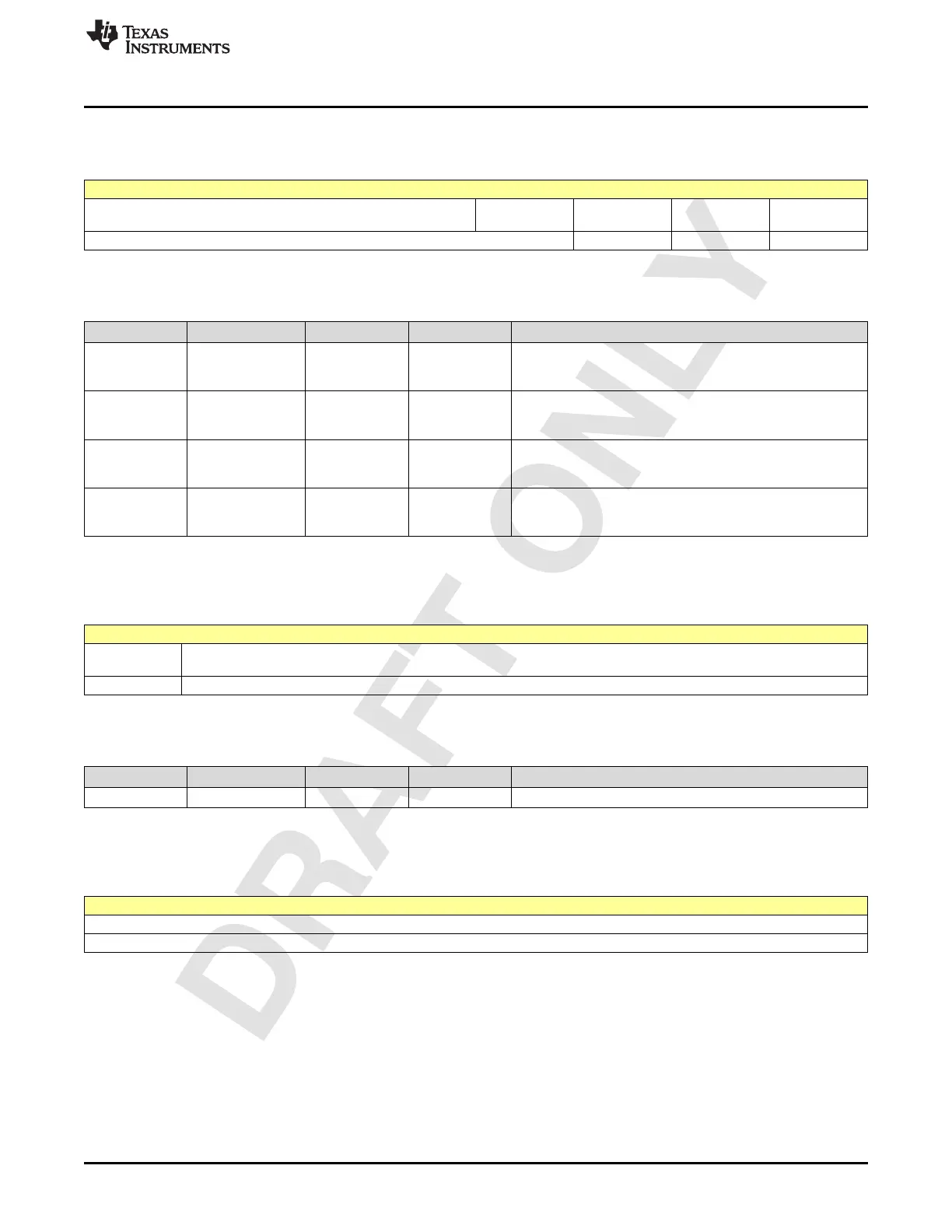

2.6.154 Register 7006h (offset = 7006h) [reset = 0h]

Figure 2-868. Register 7006h

7 6 5 4 3 2 1 0

BUS_WIDTH_L

ANE3

BUS_WIDTH_L

ANE2

BUS_WIDTH_L

ANE1

BUS_WIDTH_L

ANE0

R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-874. Register 7006 Field Descriptions

Bit Field Type Reset Description

3-3

BUS_WIDTH_LAN

E3

R/W 0h

Lane 3 data bus width selection bit:

0h: 39:0 is valid (40 bit data bus width)

1h: 19:0 is valid (20 bit data bus width)

2-2

BUS_WIDTH_LAN

E2

R/W 0h

Lane 2 data bus width selection bit:

0h: 39:0 is valid (40 bit data bus width)

1h: 19:0 is valid (20 bit data bus width)

1-1

BUS_WIDTH_LAN

E1

R/W 0h

Lane 1 data bus width selection bit:

0h: 39:0 is valid (40 bit data bus width)

1h: 19:0 is valid (20 bit data bus width)

0-0

BUS_WIDTH_LAN

E0

R/W 0h

Lane 0 data bus width selection bit:

0h: 39:0 is valid (40 bit data bus width)

1h: 19:0 is valid (20 bit data bus width)

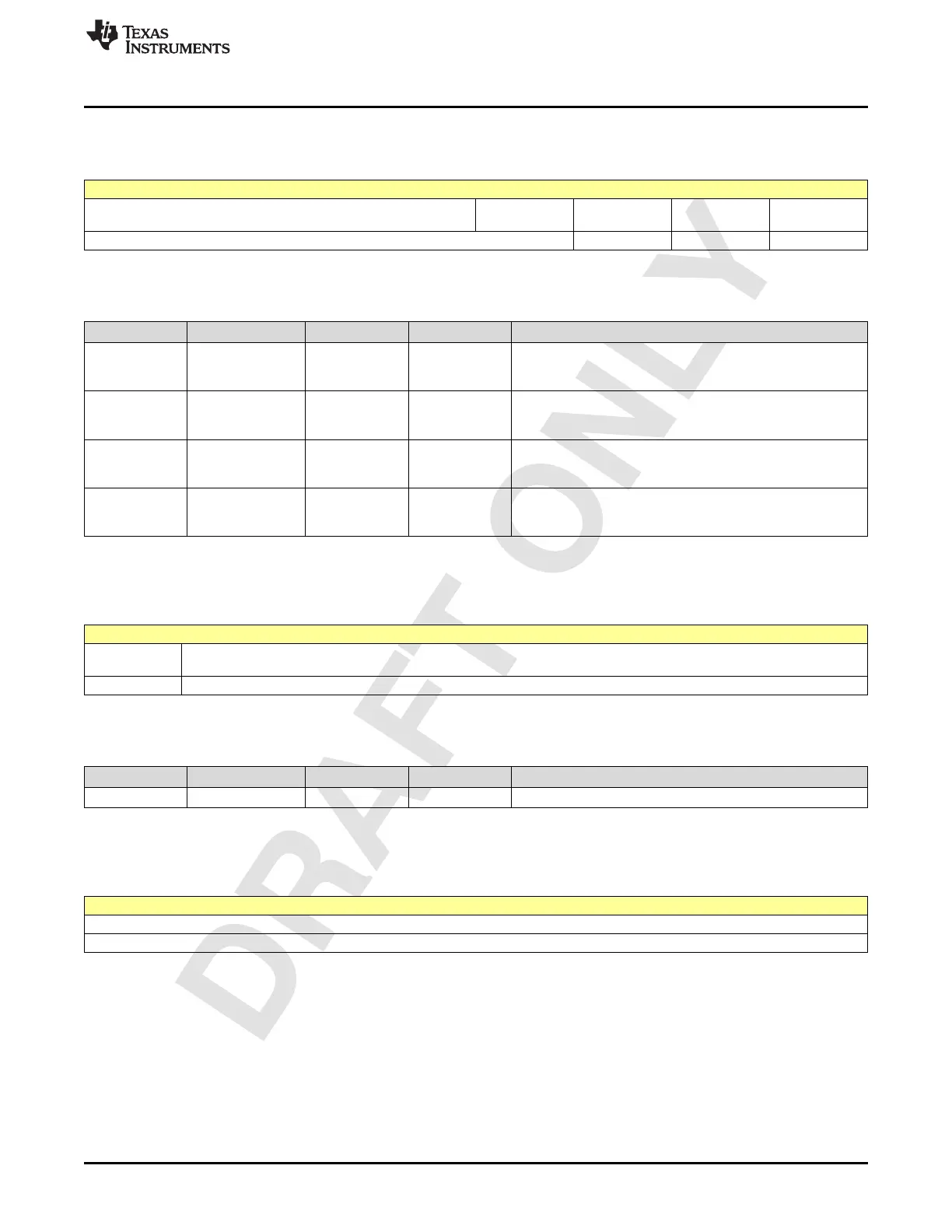

2.6.155 Register 7007h (offset = 7007h) [reset = 0h]

Figure 2-869. Register 7007h

7 6 5 4 3 2 1 0

LOOPBACK_E

N

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-875. Register 7007 Field Descriptions

Bit Field Type Reset Description

7-7 LOOPBACK_EN R/W 0h Loopback enable.

2.6.156 Register 701Ah (offset = 701Ah) [reset = 0h]

Figure 2-870. Register 701Ah

7 6 5 4 3 2 1 0

DOMAIN_RESET[7:0]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...