PLL Register Map

www.ti.com

150

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

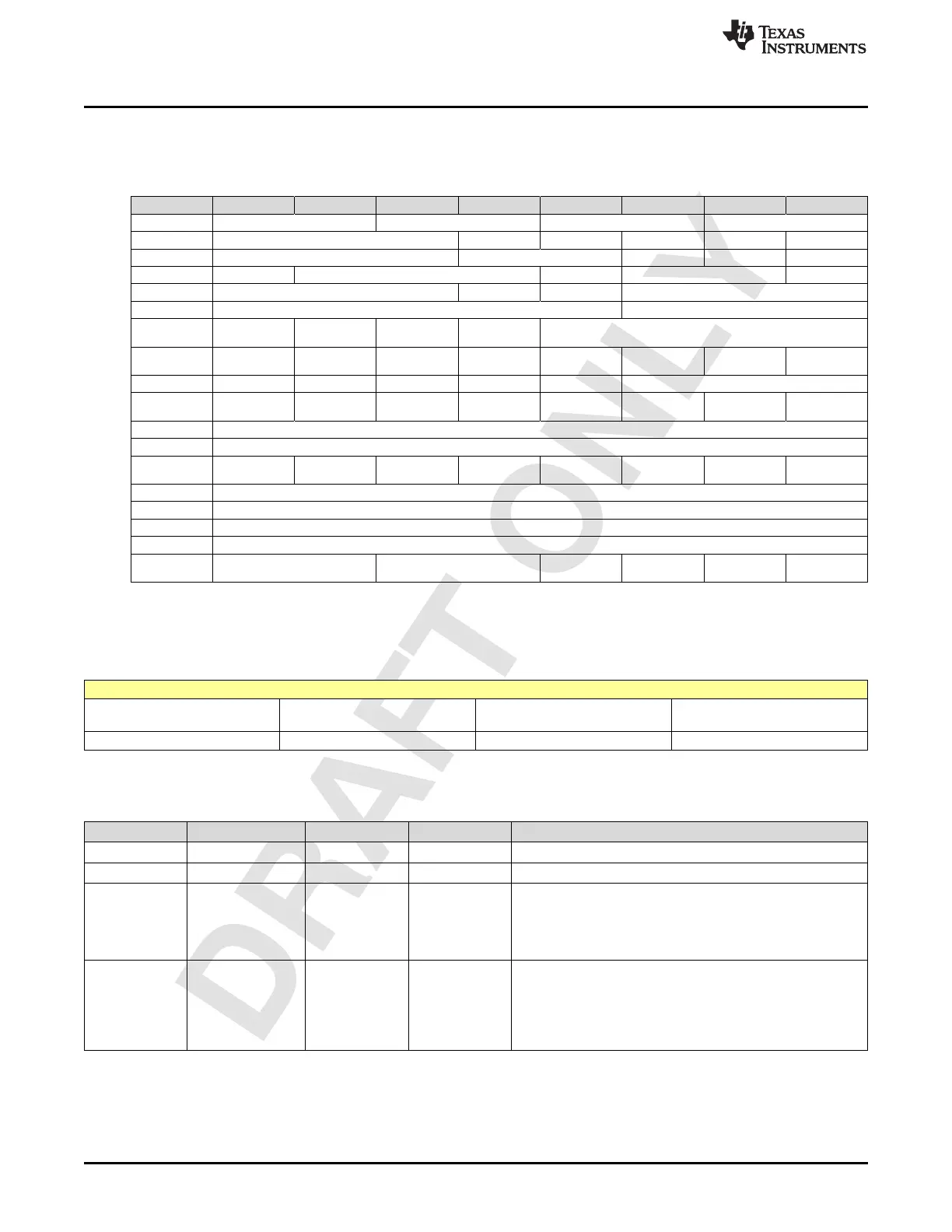

2.2 PLL Register Map

Table 2-25. PLL Register Map

ADDRESS (Hex) D7 D6 D5 D4 D3 D2 D1 D0

2Ah reserved reserved CTL_CP_CONST_100U CTL_REFCLK_BUF_CONST_300U

3Fh CTL_PFD_DEL reserved reserved reserved reserved reserved

40h CTL_CP_CURR reserved reserved reserved reserved

41h reserved reserved CTL_CP_BIAS reserved

43h CTL_LPF_R reserved reserved reserved

5Ch reserved SYSREF_LATCH_DELAY

63h

CLR_FLAG_LO

CK_OUT

CLR_FLAG_LO

CK_LOST

reserved reserved reserved

66h

LOCK_LOST_ST

ICKY

LOCK_OUT_STI

CKY

LOCK reserved reserved

EN_LOCK_DET

ECT

EN_CAL

68h VCO_SEL_RO

6Ah

reserved

LCMGEN_SYNC

_ENA

RST_LOCK_DE

TECT

6Ch LCMGEN_DIV[7:0]

6Dh LCMGEN_DIV[15:8]

6Eh

reserved

LCMGEN_SPI_S

YSREF

LCMGEN_USE_

SPI_SYSREF

6Fh SYSREF_PULSE_CNT_TX

70h SYSREF_PULSE_CNT_RX

71h SYSREF_PULSE_CNT_FB

72h SYSREF_PULSE_CNT_DIG

84h

CTL_LDOVCO_FBRES CTL_LDOVCO_VREF

LDOVCO_FORC

E_OUTTOVDD

reserved reserved reserved

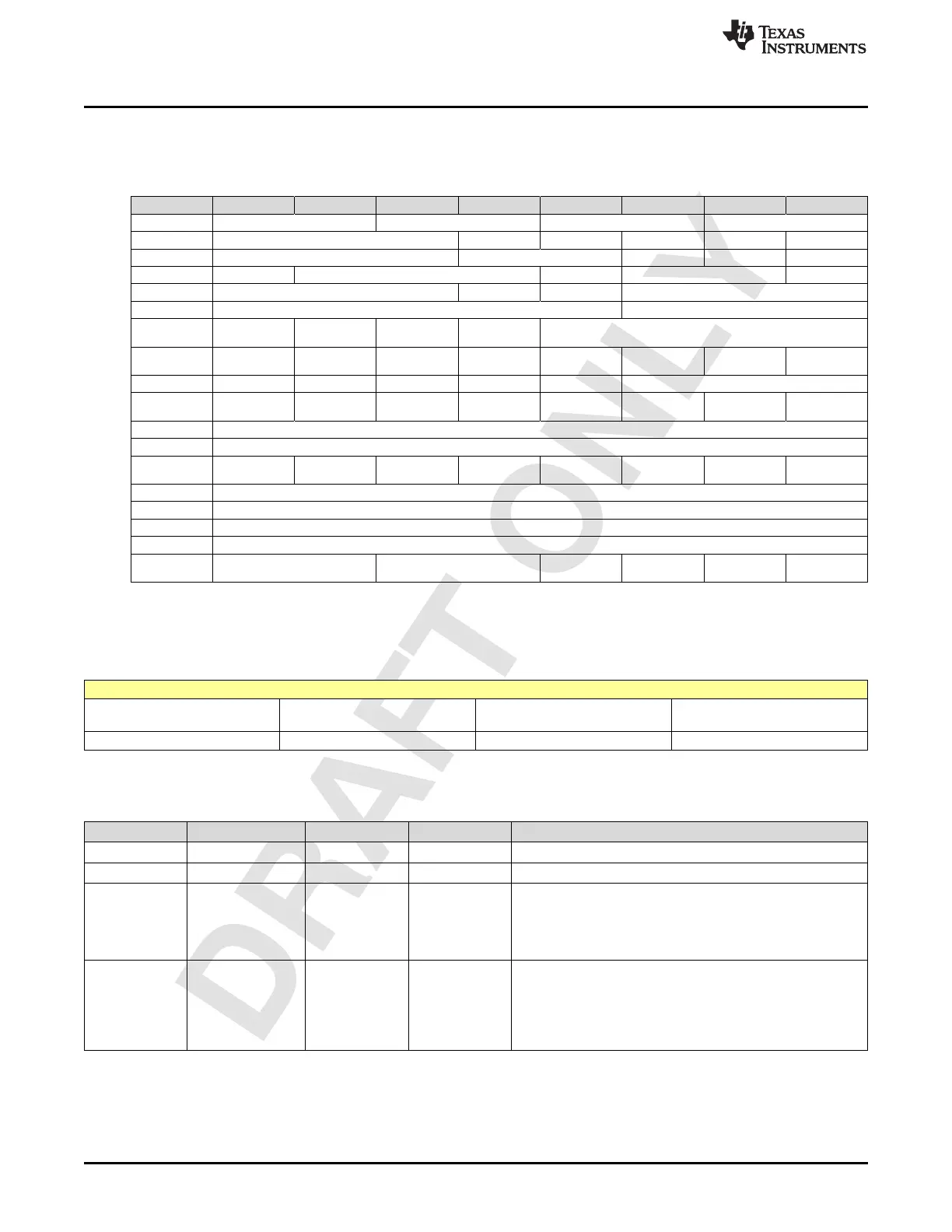

2.2.1 Register 2Ah (offset = 2Ah) [reset = 0h]

Figure 2-24. Register 2Ah

7 6 5 4 3 2 1 0

reserved reserved CTL_CP_CONST_100U CTL_REFCLK_BUF_CONST_30

0U

R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-26. Register 2A Field Descriptions

Bit Field Type Reset Description

7-6 reserved R/W 0h

5-4 reserved R/W 0h

3-2

CTL_CP_CONST_

100U

R/W 0h

scaling of currents.

00 -> scale = 1

01 -> scale = 0.8

10 -> scale = 1.4

11 -> scale = 1.2

1-0

CTL_REFCLK_BU

F_CONST_300U

R/W 0h

Refclock buffer bias current.

scaling of currents.

00 -> scale = 1

01 -> scale = 0.8

10 -> scale = 1.4

11 -> scale = 1.2

Loading...

Loading...