www.ti.com

List of Macros

105

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Macro

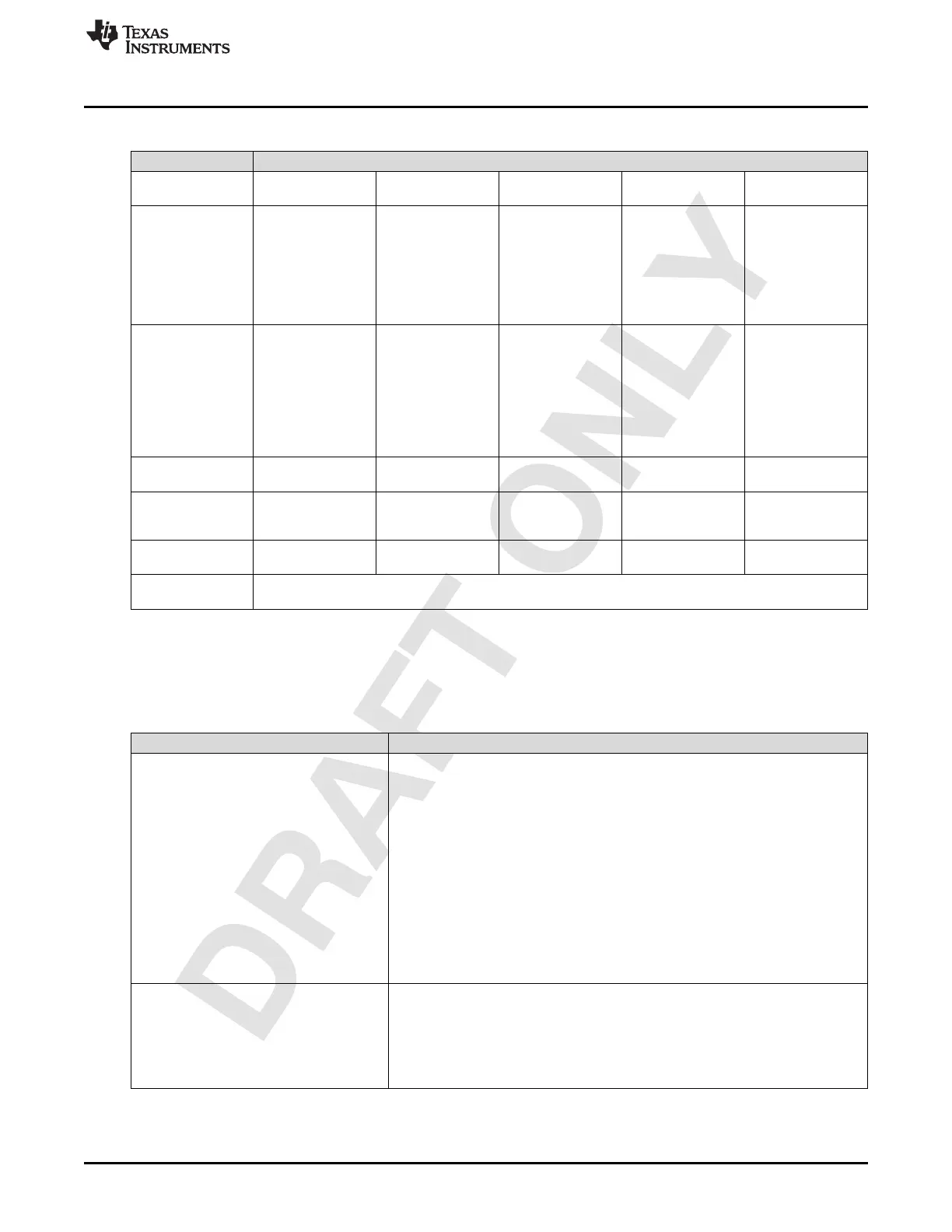

Table 1-49. (continued)

Macro TX DSA Gain-Phase Factory Calibration

7 0x06 4 RESERVED

Write 1 here

8 0x07 1 Start DSA Attn. Start DSA Attn

DSA attenuation (in

dB) where the TX-

DSA gain-phase

calibration should

begin

0 ≤ Start-DSA-Attn

≤ 39

Used only during

‘generate packet’

calibration

command

9 0x08 1 Stop DSA Attn. Stop DSA Attn

Maximum DSA

attenuation (in dB)

till which the TX-

DSA gain-phase

calibration should

be done for.

0 ≤ Stop-DSA-Attn ≤

39

Used only during

‘generate packet’

calibration

command

10 0x09 1 RESERVED

Write 0x03 here

11 0x0A 1 RESERVED

Write RESERVED

Write 0.

12 0x0B 1 RESERVED

Write 0.

Memory DSA Calibration Data will be populated here when this macro is called with Calibration Command = Generate

Calibration Packet

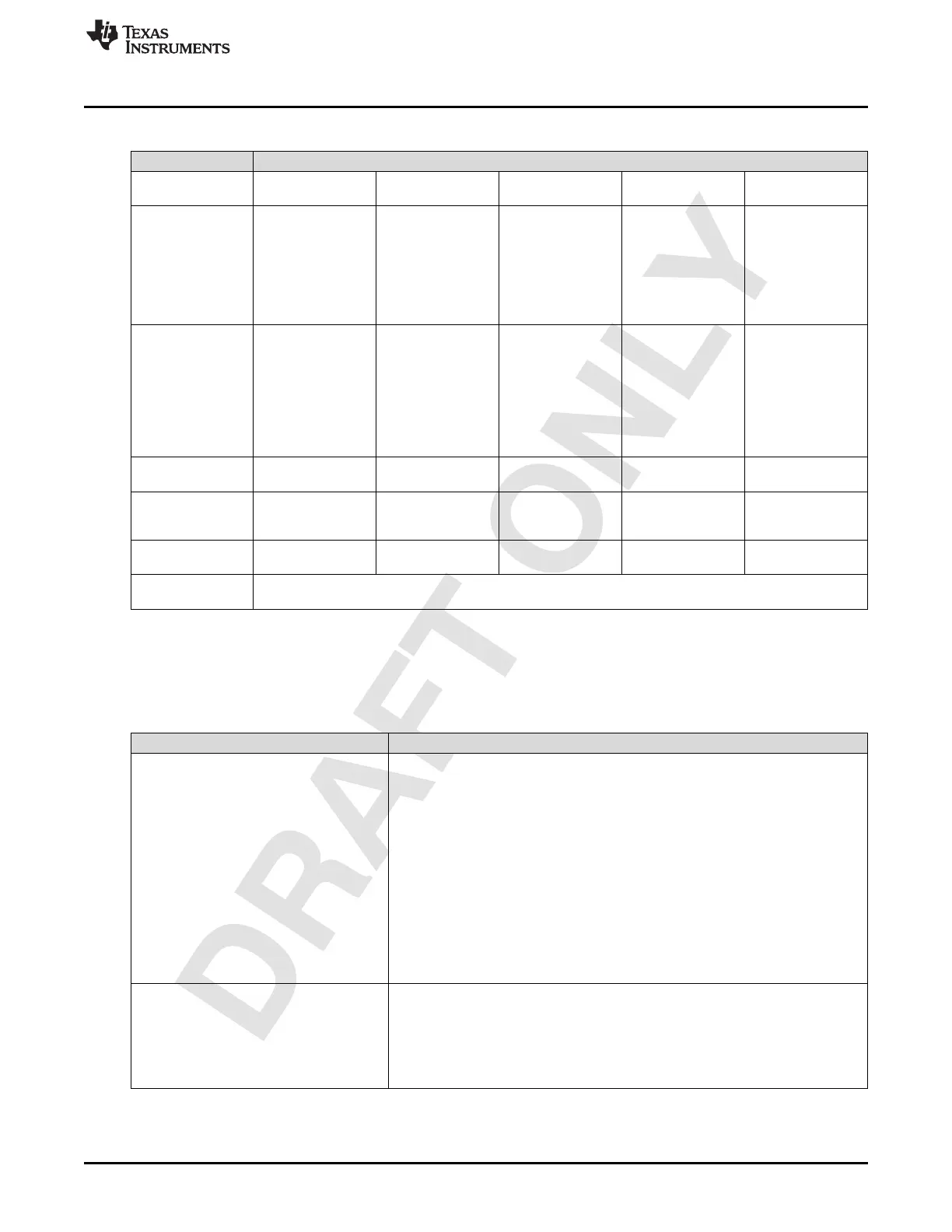

1.2.3.2.1 Error Reporting

Table 1-50 lists the error conditions associated with this macro.

Table 1-50.

Error Status Registers Interpretation

Error Code 1 (16-bit)

Bit[0]: ‘1’ → RESERVED

Bit[1]: ‘1’ → Error in Calibration Data Capture The nature of data capture error is

indicated by using 3-bits in the 32-bit error code.

The value mappings are:

3 → No Valid Capture

5 → Poor SNR in signal

6 → Signal Frequency is not fixed

Other Values are RESERVED

Bit[2]: ‘1’ → Error in Input Signal Integrity. The nature of Input signal integrity error is

indicated by using 3-bits in the 32-bit error code. The value mappings are:

1 → Signal power is low,

3 → High spur in input signal,

4 → Signal not in band,

Other Values are RESERVED

Bit[3]: ‘1’ → Large Phase Error encountered across Codes.

Other bits are RESERVED

Error Code 2 (32-bit) Bit[2:0]: Contains information about the first error condition in the above 16-bit

register. Example: Bit[1] of above register is set -> these 3-bits indicate the nature of

Data Capture error. If however, the data capture error is not set but the input signal

integrity error is set, then these bits correspond to input signal integrity error

Bit[5:3]: Contains information about the second error condition in the above 16-bit

register. Example: Bit[1] and Bit[2] of above register is set -> these 3-bits indicate

the nature of input signal integrity error

Loading...

Loading...