ADC JESD Register Map

www.ti.com

440

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

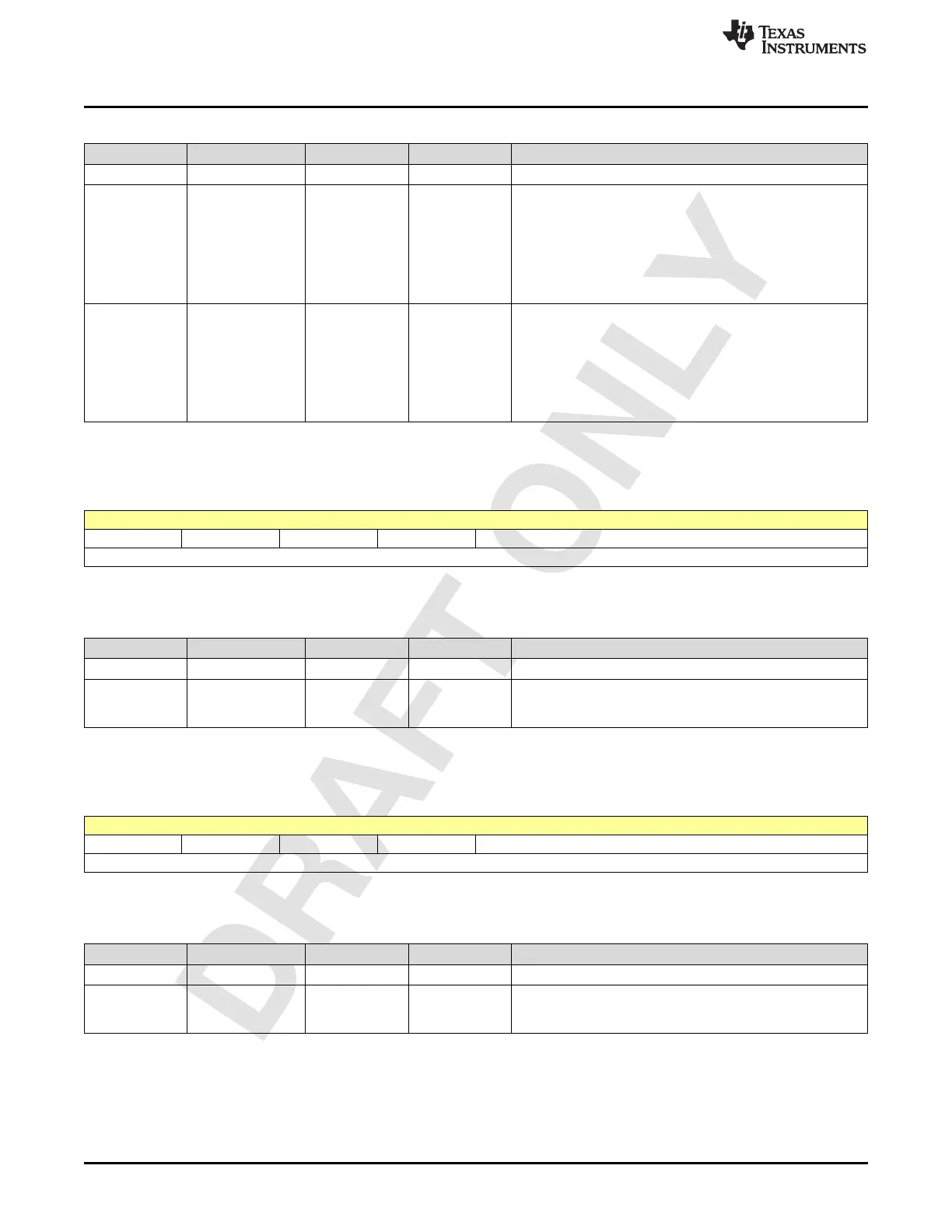

Table 2-659. Register E3 Field Descriptions

Bit Field Type Reset Description

7-4 0 R/W 0h Must read or write 0

3-2

FBAB_SD_CLK_DI

V_N_M1

R/W 1h

If input is 2 samples per clk:

SD by 2 -> M=1, N=1

SD by 3 -> M=1, N=3

SD by 4 -> M=1, N=2

if input is 1 sample per clk:

SD by 2 -> M=1, N=2

SD by 3 -> M=1, N=3

SD by 4 -> M=1, N=4

1-0

FBAB_SD_CLK_DI

V_M

R/W 2h

If input is 2 samples per clk:

SD by 2 -> M=1, N=1

SD by 3 -> M=1, N=3

SD by 4 -> M=1, N=2

if input is 1 sample per clk:

SD by 2 -> M=1, N=2

SD by 3 -> M=1, N=3

SD by 4 -> M=1, N=4

2.5.159 Register F0h (offset = F0h) [reset = 0h]

Figure 2-655. Register F0h

7 6 5 4 3 2 1 0

0 0 0 0 ALARMS_SERDES_FIFO_ERRORS_CLEAR

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-660. Register F0 Field Descriptions

Bit Field Type Reset Description

7-4 0 R/W 0h Must read or write 0

3-0

ALARMS_SERDES

_FIFO_ERRORS_

CLEAR

R/W 0h register to clear serdes_fifo_errors alarm register

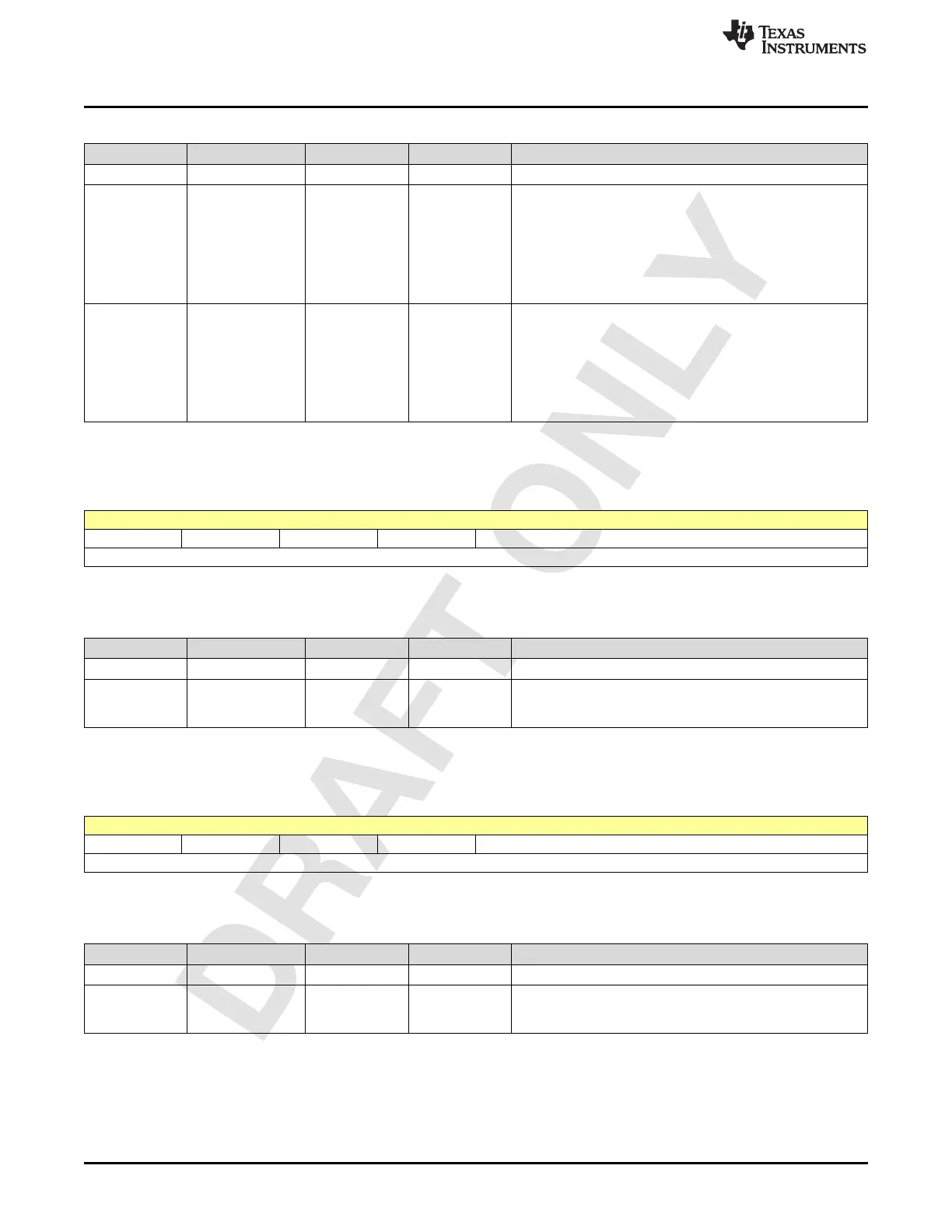

2.5.160 Register F1h (offset = F1h) [reset = 0h]

Figure 2-656. Register F1h

7 6 5 4 3 2 1 0

0 0 0 0 ALARMS_SERDES_FIFO_ERRORS_MASK

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-661. Register F1 Field Descriptions

Bit Field Type Reset Description

7-4 0 R/W 0h Must read or write 0

3-0

ALARMS_SERDES

_FIFO_ERRORS_

MASK

R/W 0h

register to mask serdes_fifo_errors alarm register

Masked alarms are ored and sent to the pin

Loading...

Loading...