www.ti.com

AFE79xx_GLOBAL Register Map

141

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

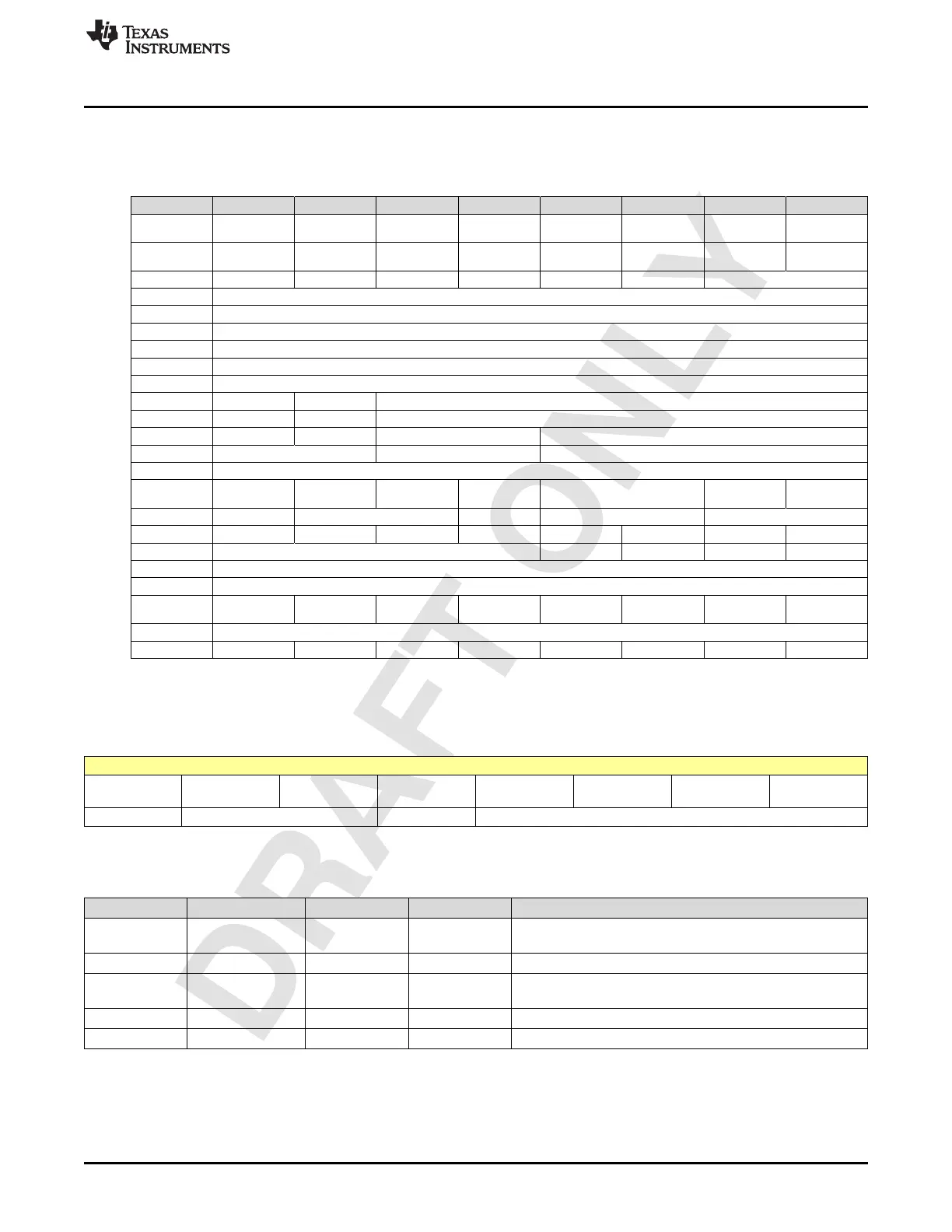

2.1 AFE79xx_GLOBAL Register Map

Table 2-1. Global Register Map

ADDRESS (Hex) D7 D6 D5 D4 D3 D2 D1 D0

00h

GLOBAL_SOFT

_RESET 0

GLOBAL_ASCE

ND

GLOBAL_4PIN

0 0 0 0

01h

GLOBAL_ADDR

ESSING_TYPE 0 0 0 0 0 0 0

02h 0 0 0 0 0 0 GLOBAL_MODE

03h CHIP_TYPE

04h CHIP_ID[7:0]

05h CHIP_ID[15:8]

06h CHIP_VER

07h VENDOR_ID[7:0]

08h VENDOR_ID[15:8]

10h reserved 0 EC_DIG

11h 0 0 EC_ANA

12h 0 0 FB TOP RX TOP

13h DSA_PAGE1 DSA_PAGE0 TX_ANA

14h TXCALIB

15h

TIMING_CONTR

OLLER

DIGTOP reserved IO_WRAP reserved ANA_4T4R PLL

16h 0 SERDES JESD_SUBCHIP DAC_JESD ADC_JESD

18h calib_memory reserved MACRO reserved MCU_mem reserved reserved reserved

19h TX TOP reserved reserved reserved reserved

1Bh ALARMS_CLEAR[7:0]

1Ch ALARMS_MASK[7:0]

1Dh 0 0 0 0 0 0

ALARMS_MASK

[8]

ALARMS_CLEA

R[8]

1Eh ALARMS[7:0]

1Fh 0 0 0 0 0 0 0 ALARMS[8]

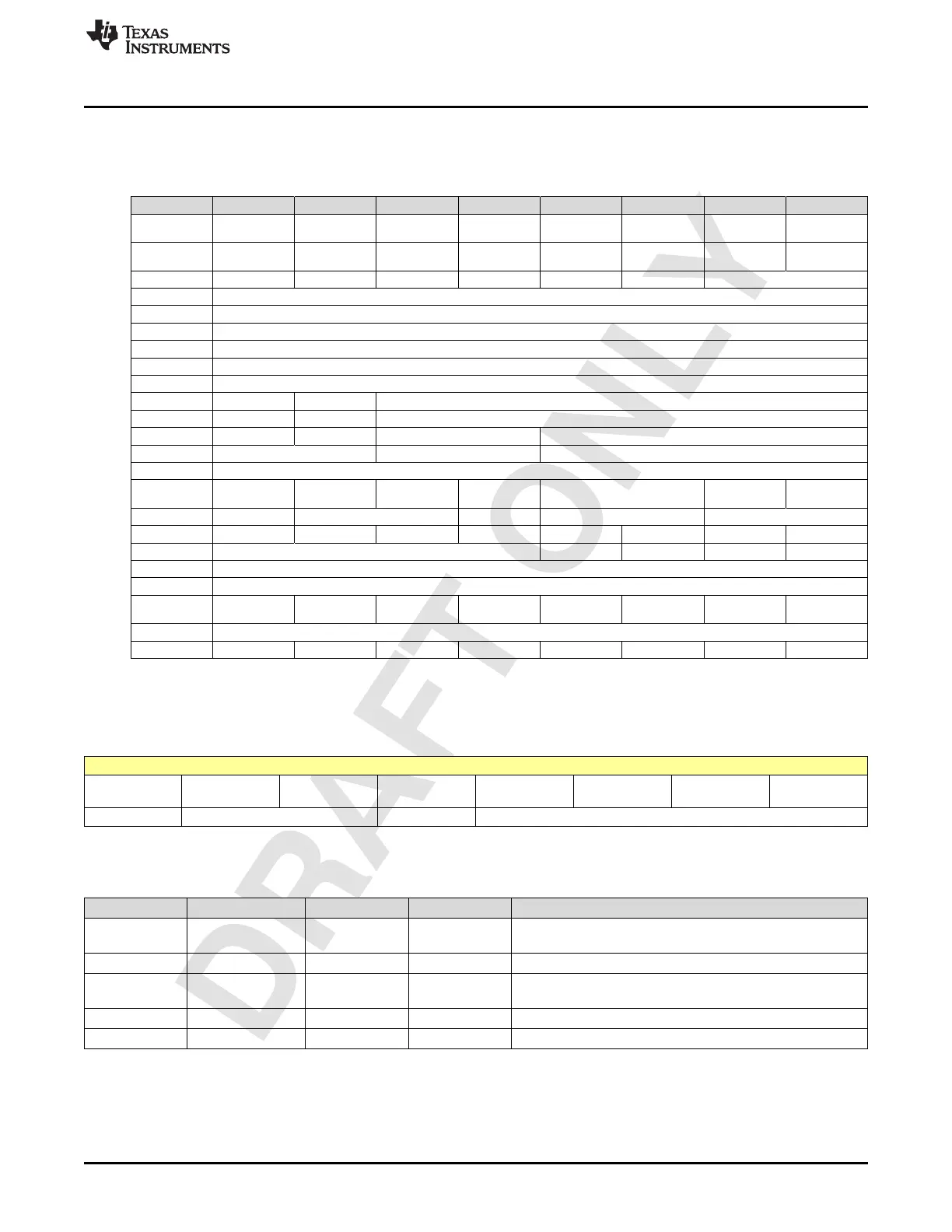

2.1.1 Register 0h (offset = 0h) [reset = 30h]

Figure 2-1. Register 0h

7 6 5 4 3 2 1 0

GLOBAL_SOF

T_RESET

0 GLOBAL_ASC

END

GLOBAL_4PIN 0 0 0 0

R/W-0h R/W-0h R/W-1h R/W-1h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2. Register 00 Field Descriptions

Bit Field Type Reset Description

7-7

GLOBAL_SOFT_R

ESET

R/W 0h soft reset when asserted.

6-6 0 R/W 0h Must read or write 0

5-5 GLOBAL_ASCEND R/W 1h

In streaming mode 1=addreses increases 0=address

decreases

4-4 GLOBAL_4PIN R/W 1h Use 4 pin SPI interface when asserted.

3-0 0 R/W 0h Must read or write 0

Loading...

Loading...