JESD_SUBCHIP Register Map

www.ti.com

240

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

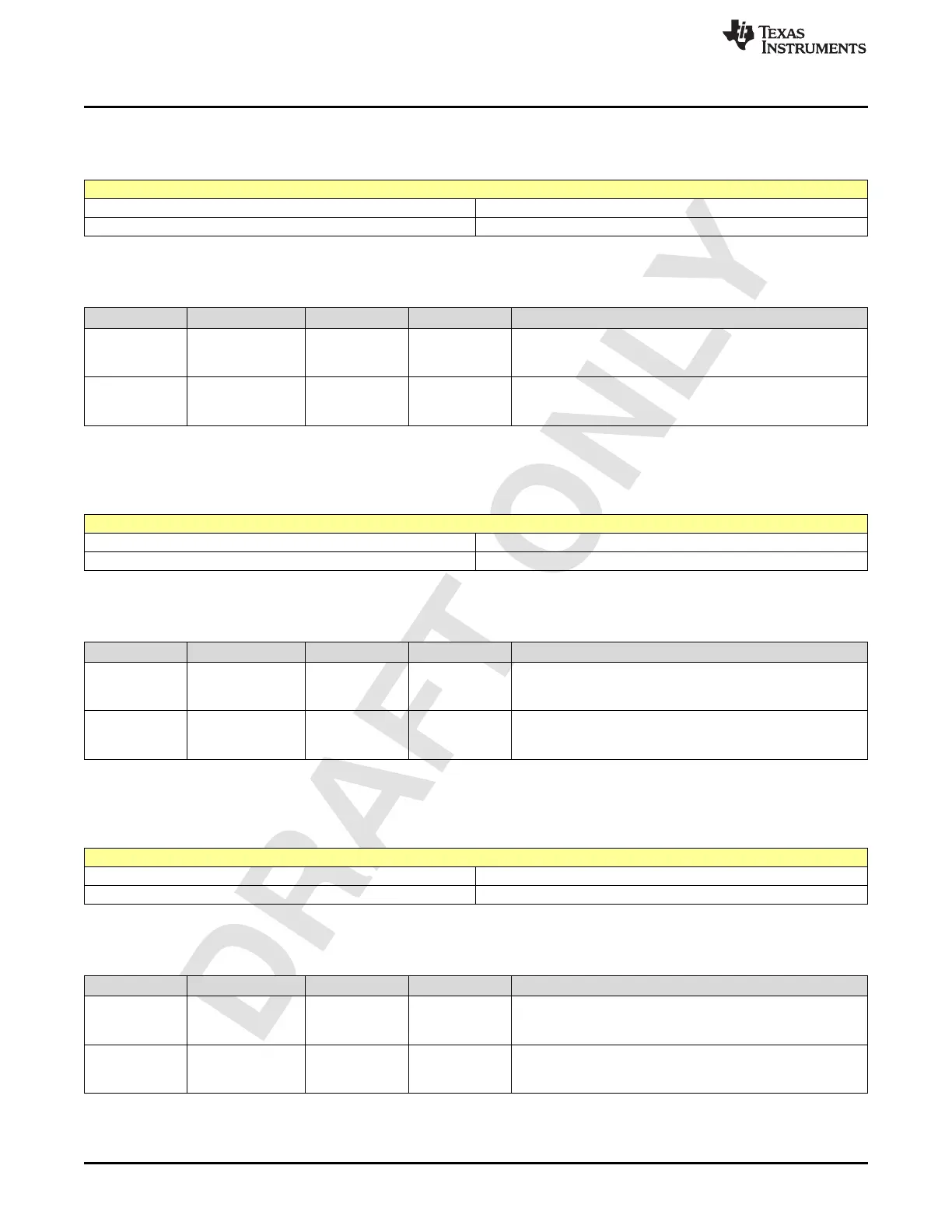

2.3.143 Register 162h (offset = 162h) [reset = 0h]

Figure 2-184. Register 162h

7 6 5 4 3 2 1 0

DBG_FIFO_SAMPLED_WR_PTR DBG_FIFO_SAMPLED_RD_PTR

R-0h R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-187. Register 162 Field Descriptions

Bit Field Type Reset Description

7-4

DBG_FIFO_SAMP

LED_WR_PTR

R 0h

RX/FB Async-FIFO Sampled write pointer. Which Async-FIFO

write-pointer to be captured is selected by 'dbg_fifo_sel'

register

3-0

DBG_FIFO_SAMP

LED_RD_PTR

R 0h

RX/FB Async-FIFO Sampled read pointer. Which Async-FIFO

read-pointer to be captured is selected by 'dbg_fifo_sel'

register

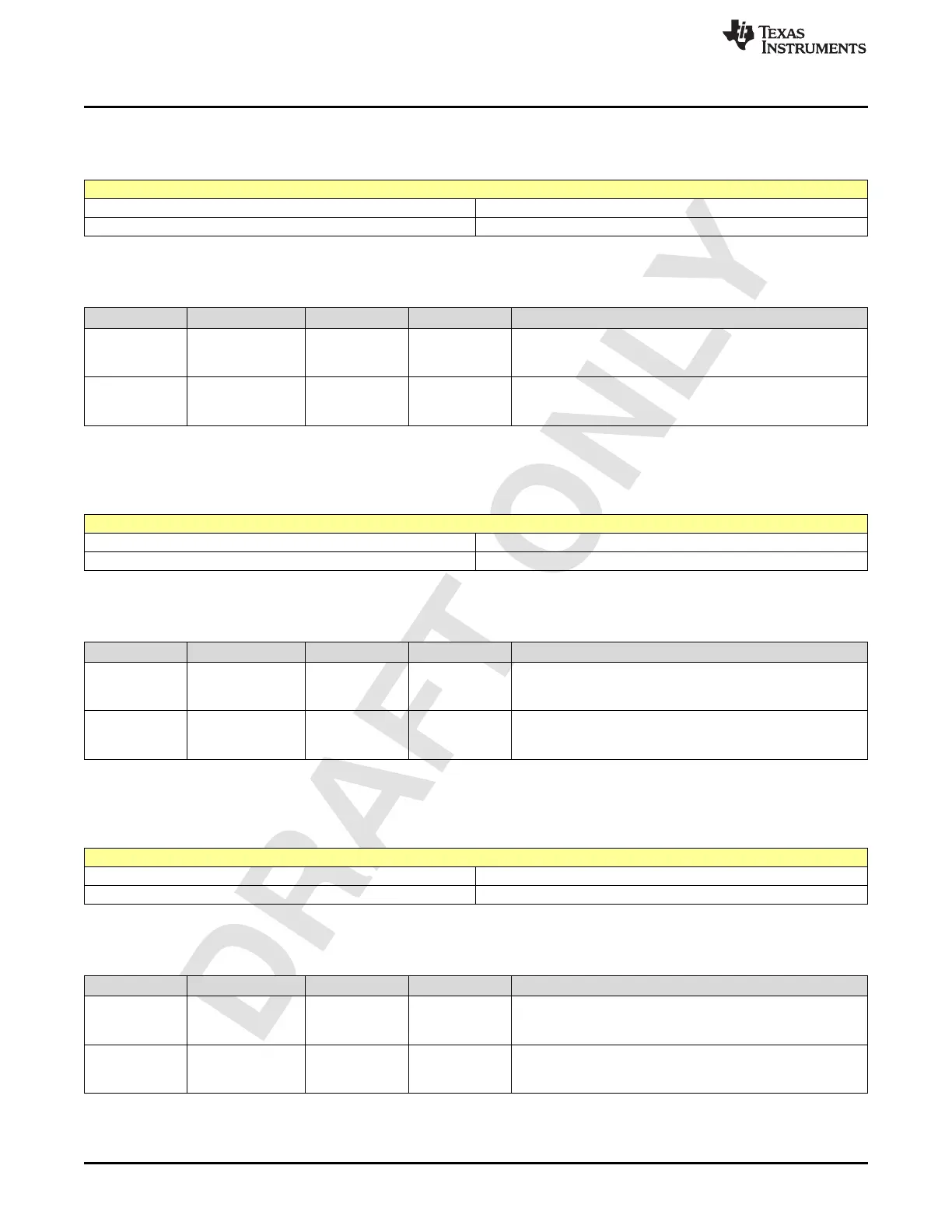

2.3.144 Register 164h (offset = 164h) [reset = 0h]

Figure 2-185. Register 164h

7 6 5 4 3 2 1 0

DBG_RXB_ASYNC_FIFO_ALARM_CLR DBG_RXA_ASYNC_FIFO_ALARM_CLR

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-188. Register 164 Field Descriptions

Bit Field Type Reset Description

7-4

DBG_RXB_ASYNC

_FIFO_ALARM_CL

R

R/W 0h

clear for RXB to JESD Async-FIFO debug debug alarm. Only

bit0 is valid.

3-0

DBG_RXA_ASYNC

_FIFO_ALARM_CL

R

R/W 0h

clear for RXA to JESD Async-FIFO debug alarm. Only bit0 is

valid.

2.3.145 Register 165h (offset = 165h) [reset = 0h]

Figure 2-186. Register 165h

7 6 5 4 3 2 1 0

DBG_RXD_ASYNC_FIFO_ALARM_CLR DBG_RXC_ASYNC_FIFO_ALARM_CLR

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-189. Register 165 Field Descriptions

Bit Field Type Reset Description

7-4

DBG_RXD_ASYN

C_FIFO_ALARM_

CLR

R/W 0h

clear for RXD to JESD Async-FIFO debug alarm. Only bit0 is

valid.

3-0

DBG_RXC_ASYN

C_FIFO_ALARM_

CLR

R/W 0h

clear for RXC to JESD Async-FIFO debug alarm. Only bit0 is

valid.

Loading...

Loading...