www.ti.com

DAC JESD Register Map

363

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

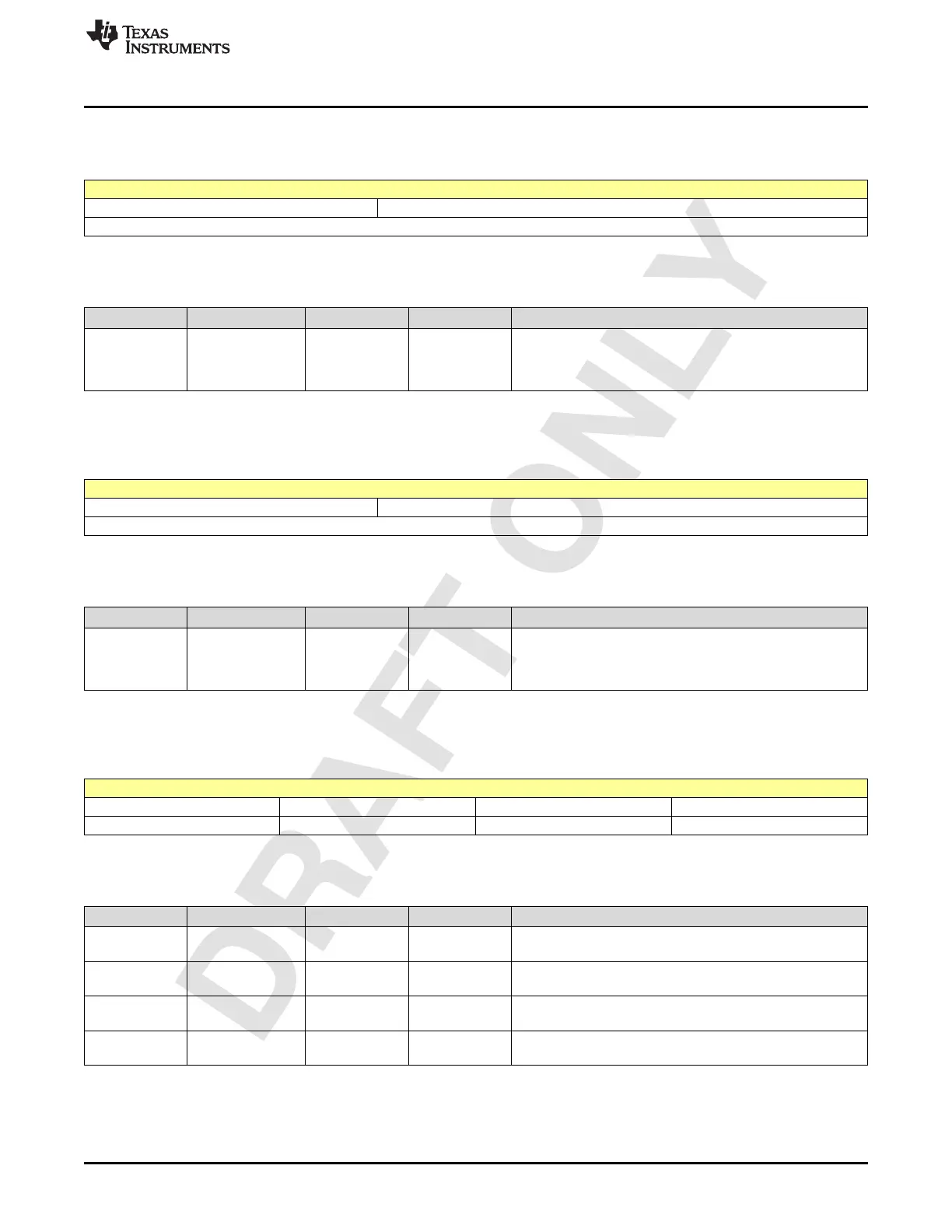

2.4.250 Register 13Eh (offset = 13Eh) [reset = 0h]

Figure 2-479. Register 13Eh

7 6 5 4 3 2 1 0

LANE2_SKEW

R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-483. Register 13E Field Descriptions

Bit Field Type Reset Description

4-0 LANE2_SKEW R 0h

JESDB: Measure lane2 skew from lane2 getting ctrl-R

character to all the lanes getting ctrl-R character

JESDC: Measure lane2 skew from lane2 getting emb-lock to

all the lanes getting emb-locks character

2.4.251 Register 13Fh (offset = 13Fh) [reset = 0h]

Figure 2-480. Register 13Fh

7 6 5 4 3 2 1 0

LANE3_SKEW

R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-484. Register 13F Field Descriptions

Bit Field Type Reset Description

4-0 LANE3_SKEW R 0h

JESDB: Measure lane3 skew from lane3 getting ctrl-R

character to all the lanes getting ctrl-R character

JESDC: Measure lane3 skew from lane3 getting emb-lock to

all the lanes getting emb-locks character

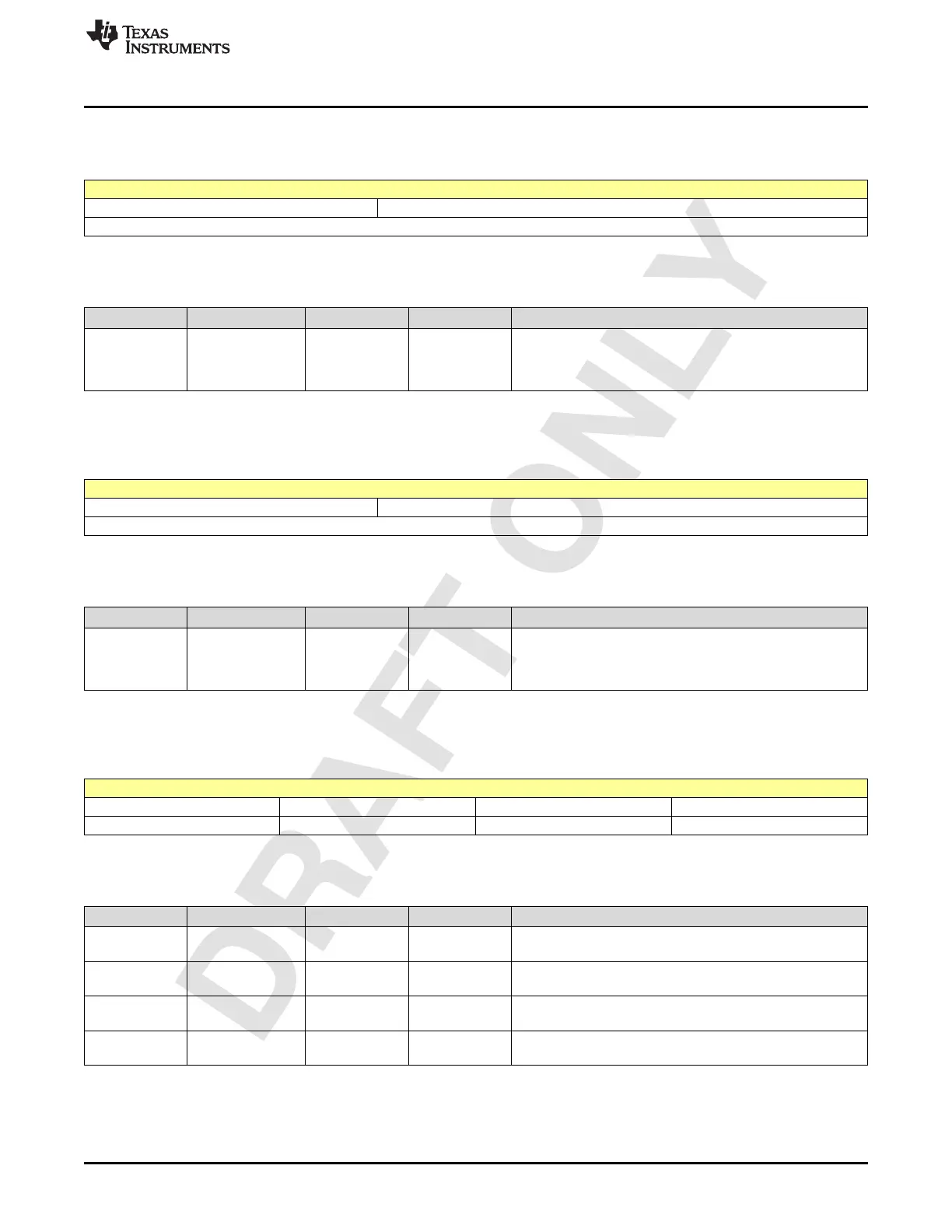

2.4.252 Register 140h (offset = 140h) [reset = 0h]

Figure 2-481. Register 140h

7 6 5 4 3 2 1 0

CTRL_TX1_ROOT_CLK_P3 CTRL_TX1_ROOT_CLK_P2 CTRL_TX1_ROOT_CLK_P1 CTRL_TX1_ROOT_CLK_P0

R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-485. Register 140 Field Descriptions

Bit Field Type Reset Description

7-6

CTRL_TX1_ROOT

_CLK_P3

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

5-4

CTRL_TX1_ROOT

_CLK_P2

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

3-2

CTRL_TX1_ROOT

_CLK_P1

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

1-0

CTRL_TX1_ROOT

_CLK_P0

R/W 0h

bit[1] - select bit[0] as clk-en

bit[0] - 0:DIS, 1-EN

Loading...

Loading...