www.ti.com

PLL Register Map

151

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

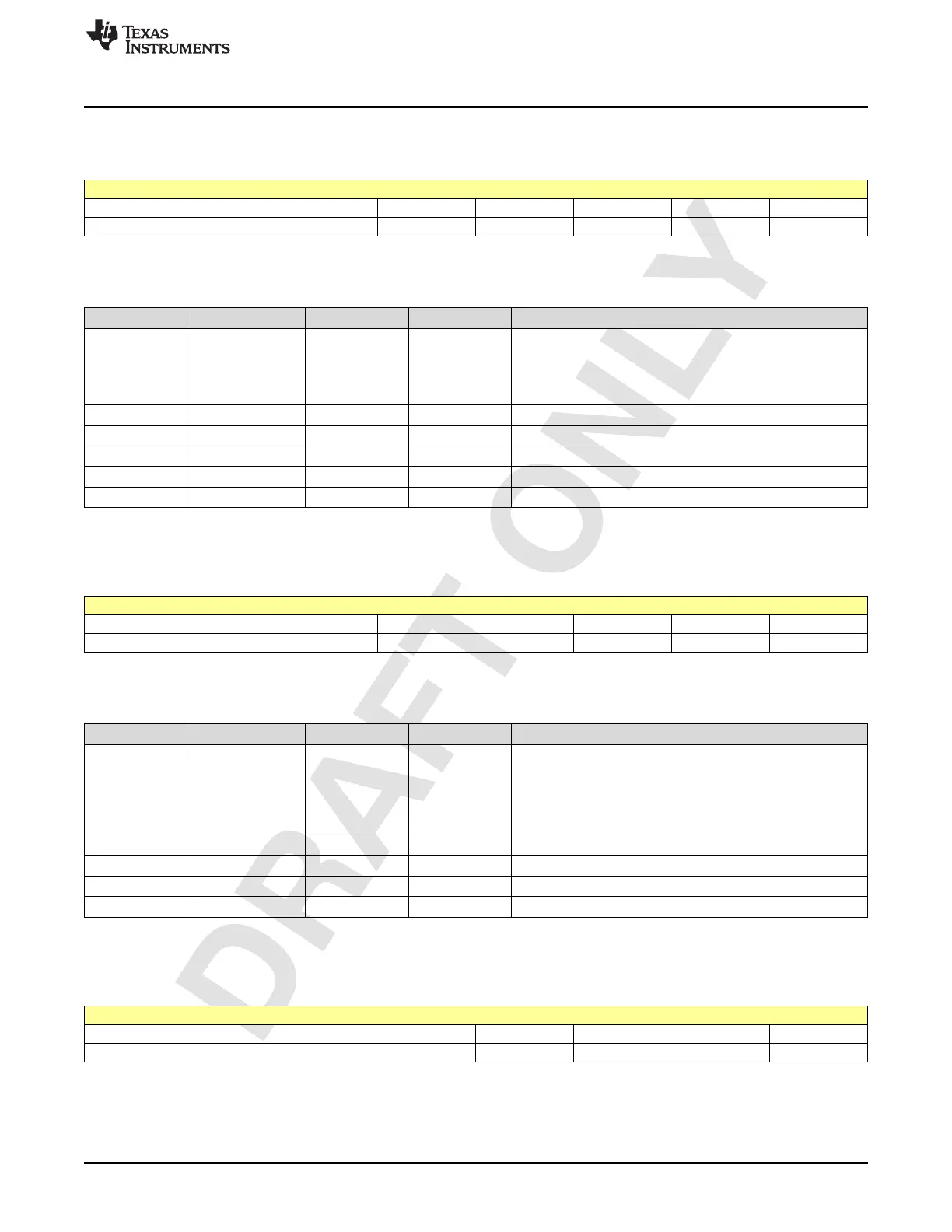

2.2.2 Register 3Fh (offset = 3Fh) [reset = 8h]

Figure 2-25. Register 3Fh

7 6 5 4 3 2 1 0

CTL_PFD_DEL reserved reserved reserved reserved reserved

R/W-0h R/W-0h R/W-1h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-27. Register 3F Field Descriptions

Bit Field Type Reset Description

7-5 CTL_PFD_DEL R/W 0h

Phase Frequency detector UP/Down Pulse Width:

0 : 190 ps

1 : 100 ps

2 : 280 ps

3 : 360 ps

4-4 reserved R/W 0h

3-3 reserved R/W 1h

2-2 reserved R/W 0h

1-1 reserved R/W 0h

0-0 reserved R/W 0h

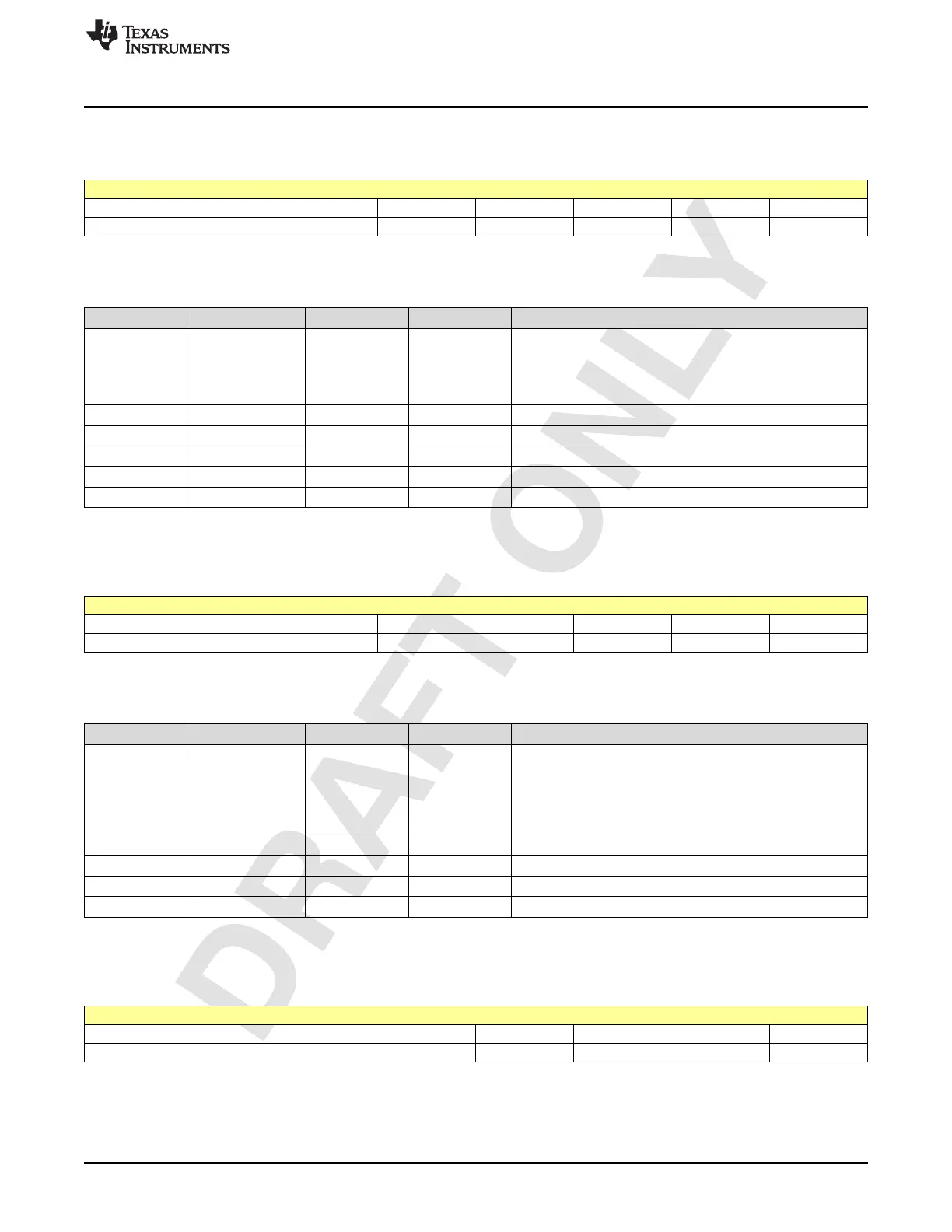

2.2.3 Register 40h (offset = 40h) [reset = 0h]

Figure 2-26. Register 40h

7 6 5 4 3 2 1 0

CTL_CP_CURR reserved reserved reserved reserved

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-28. Register 40 Field Descriptions

Bit Field Type Reset Description

7-5 CTL_CP_CURR R/W 0h

Charge pump current

0 : 250 uA

1 : 125 uA

2 : 500 uA

3 : 1000 uA

4 to 7 are invalid.

4-3 reserved R/W 0h

2-2 reserved R/W 0h

1-1 reserved R/W 0h

0-0 reserved R/W 0h

2.2.4 Register 41h (offset = 41h) [reset = 0h]

Figure 2-27. Register 41h

7 6 5 4 3 2 1 0

reserved reserved CTL_CP_BIAS reserved

R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...