SERDES Register Map

www.ti.com

510

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

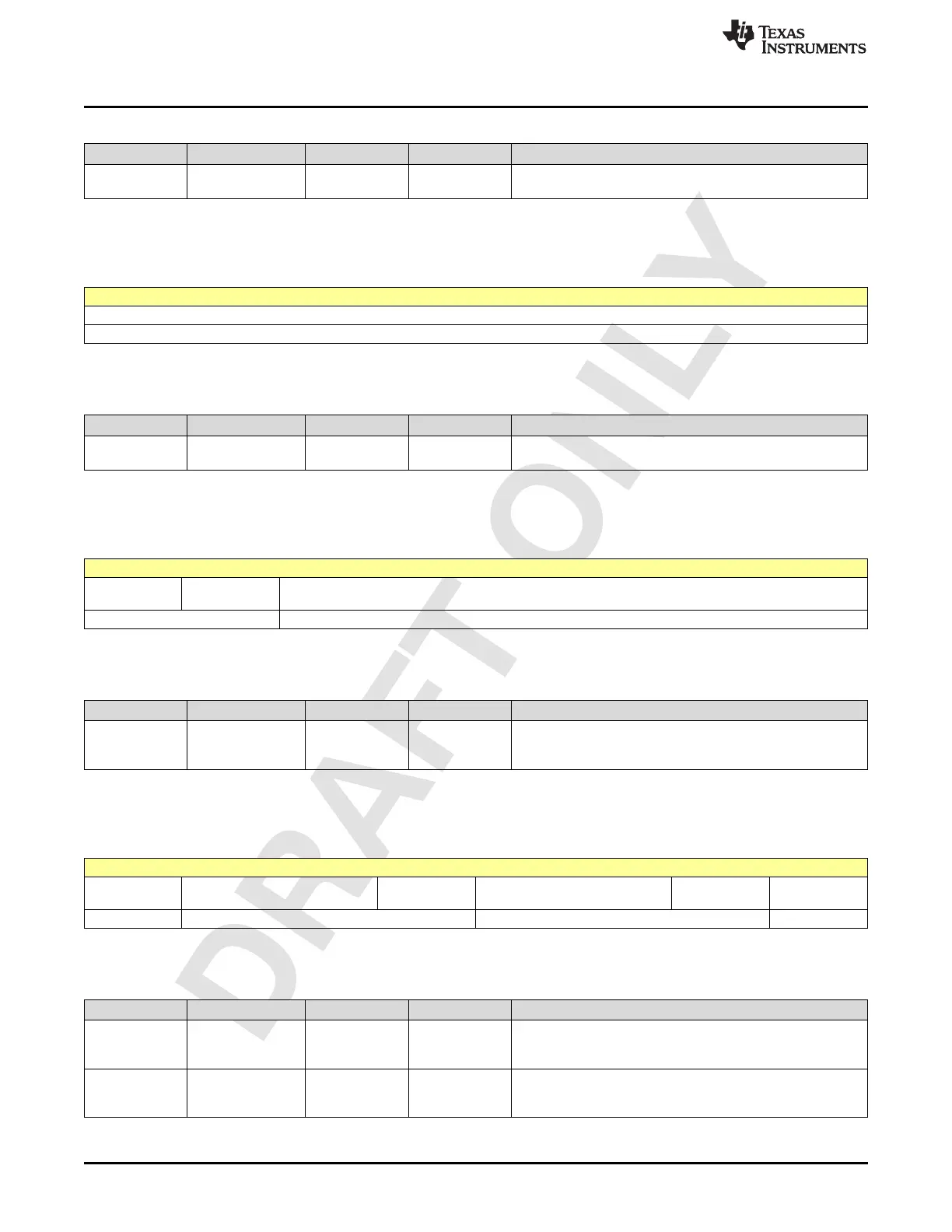

Table 2-858. Register 49EE Field Descriptions

Bit Field Type Reset Description

7-7

TEST_MUX_SEL_

B[0]

R/W 0h Analog test mux select bits. For Serdes debug only.

2.6.139 Register 49EFh (offset = 49EFh) [reset = 0h]

Figure 2-853. Register 49EFh

7 6 5 4 3 2 1 0

TEST_MUX_SEL_B[8:1]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-859. Register 49EF Field Descriptions

Bit Field Type Reset Description

7-0

TEST_MUX_SEL_

B[8:1]

R/W 0h Analog test mux select bits. For Serdes debug only.

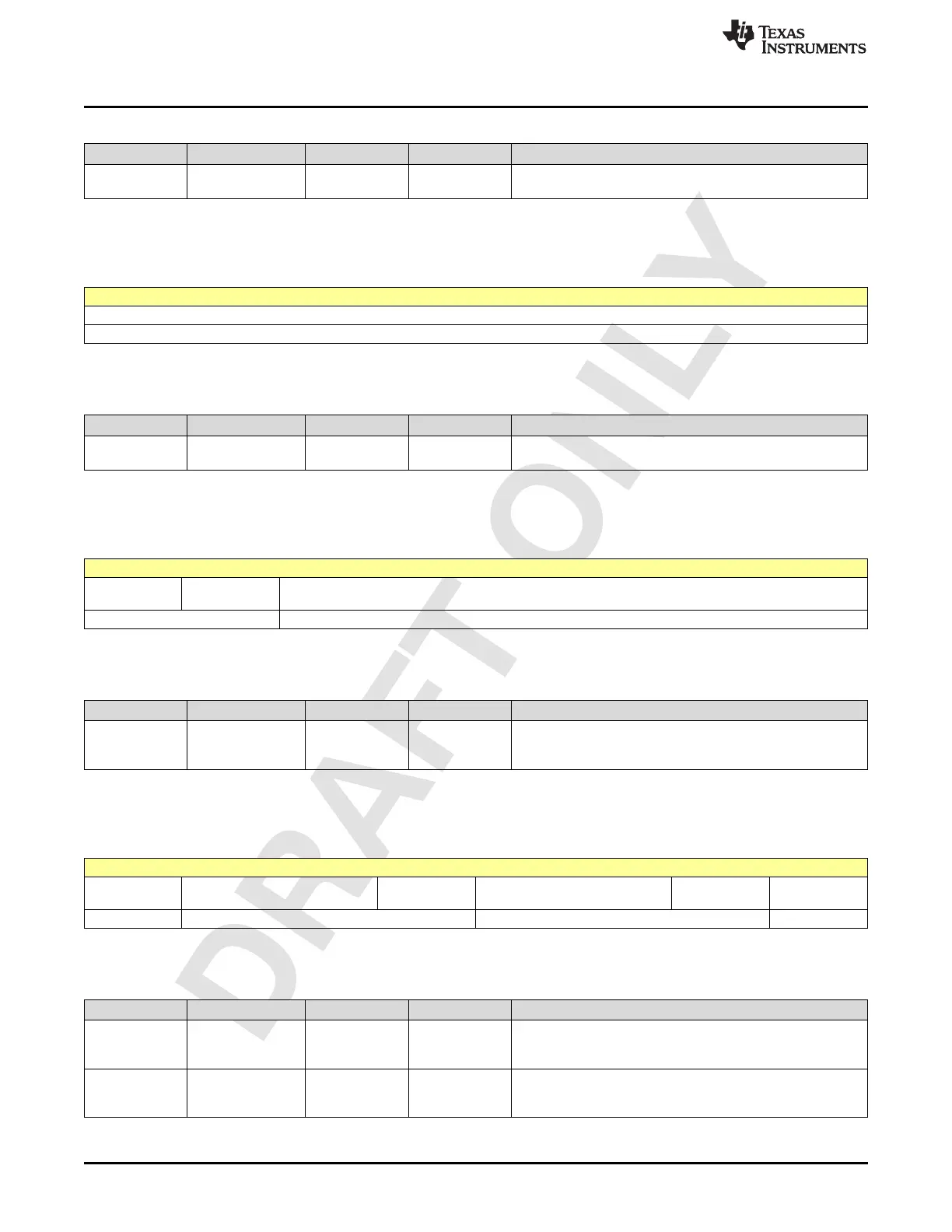

2.6.140 Register 49F0h (offset = 49F0h) [reset = 40h]

Figure 2-854. Register 49F0h

7 6 5 4 3 2 1 0

PU_RX_INTP_

LANE3

R/W-1h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-860. Register 49F0 Field Descriptions

Bit Field Type Reset Description

6-6

PU_RX_INTP_LAN

E3

R/W 1h

Power up RX Lane 3 interpolator.

0h: Power down

1h: Power up

2.6.141 Register 49F1h (offset = 49F1h) [reset = 92h]

Figure 2-855. Register 49F1h

7 6 5 4 3 2 1 0

PU_RX_INTP_

LANE0

PU_RX_INTP_

LANE1

PU_RX_INTP_

LANE2

R/W-1h R/W-1h R/W-1h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-861. Register 49F1 Field Descriptions

Bit Field Type Reset Description

7-7

PU_RX_INTP_LAN

E0

R/W 1h

Power up RX Lane 0 interpolator.

0h: Power down

1h: Power up

4-4

PU_RX_INTP_LAN

E1

R/W 1h

Power up RX Lane 1 interpolator.

0h: Power down

1h: Power up

Loading...

Loading...