JESD_SUBCHIP Register Map

www.ti.com

246

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-202. Register 176 Field Descriptions (continued)

Bit Field Type Reset Description

5-5

DBG_FBCD_AFIF

O_SYS_REF_RD_

STICKY

R 0h FBCD to JESD Async FIFO rd-sysref monitor

4-4

DBG_FBCD_AFIF

O_SYS_REF_WR_

STICKY

R 0h FBCD to JESD Async FIFO wr-sysref monitor

3-3

DBG_FBAB_AFIF

O_RD_CLK_TOGG

LE_STICKY

R 0h FBAB to JESD Async FIFO rd-clk monitor

2-2

DBG_FBAB_AFIF

O_WR_CLK_TOG

GLE_STICKY

R 0h FBAB to JESD Async FIFO wr-clk monitor

1-1

DBG_FBAD_AFIF

O_SYS_REF_RD_

STICKY

R 0h FBAB to JESD Async FIFO rd-sysref monitor

0-0

DBG_FBAB_AFIF

O_SYS_REF_WR_

STICKY

R 0h FBAB to JESD Async FIFO wr-sysref monitor

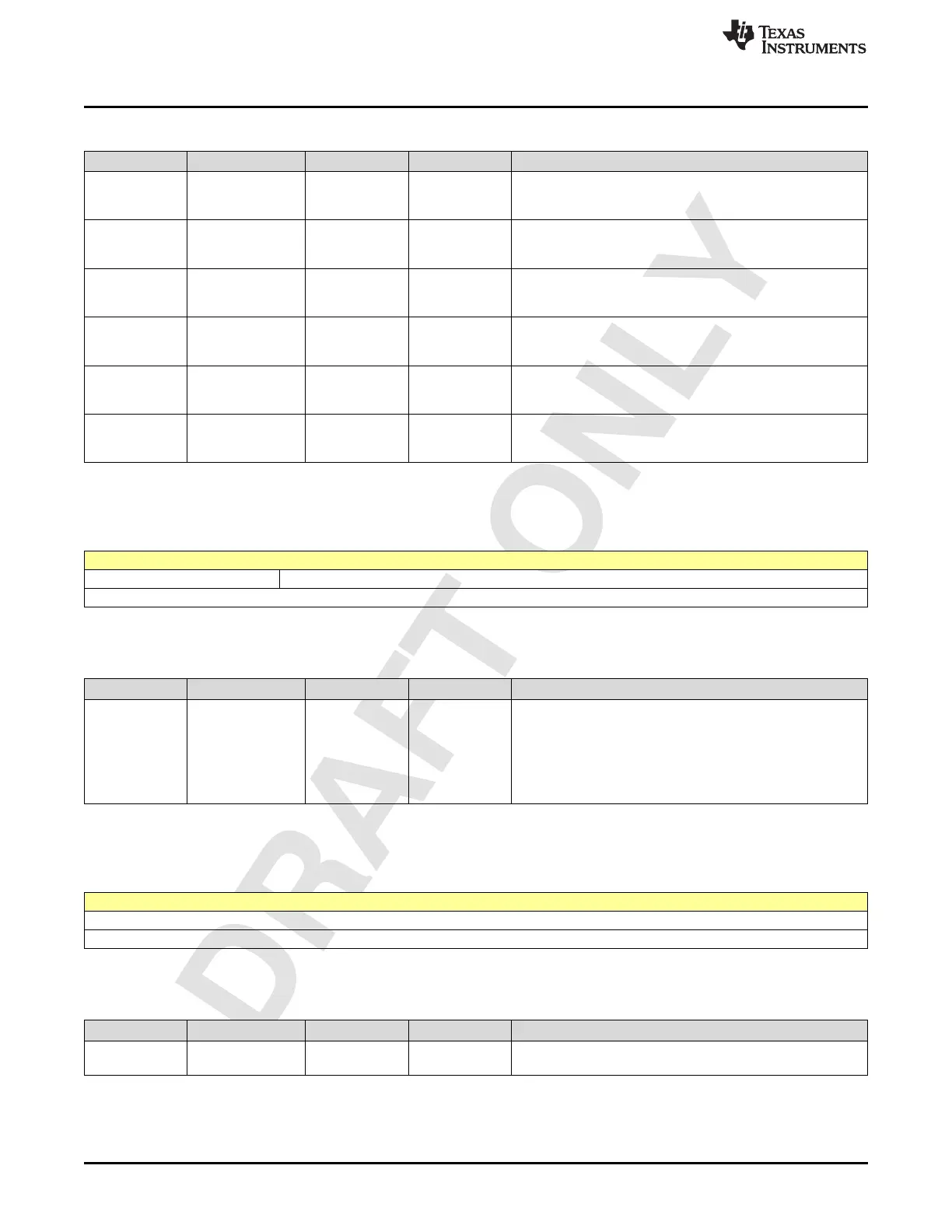

2.3.159 Register 180h (offset = 180h) [reset = 0h]

Figure 2-200. Register 180h

7 6 5 4 3 2 1 0

ADC_SYNC_N_FROM_PIN

R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-203. Register 180 Field Descriptions

Bit Field Type Reset Description

5-0

ADC_SYNC_N_FR

OM_PIN

R 0h

Spi monitor of adc_sync_n input ports

Bit0 : For adc_sync_n[0].

Bit1 : For adc_sync_n[1].

Bit2 : For adc_sync_n[2].

Bit3 : For adc_sync_n[3].

Bit4 : For adc_sync_n[4].

Bit5 : For adc_sync_n[5].

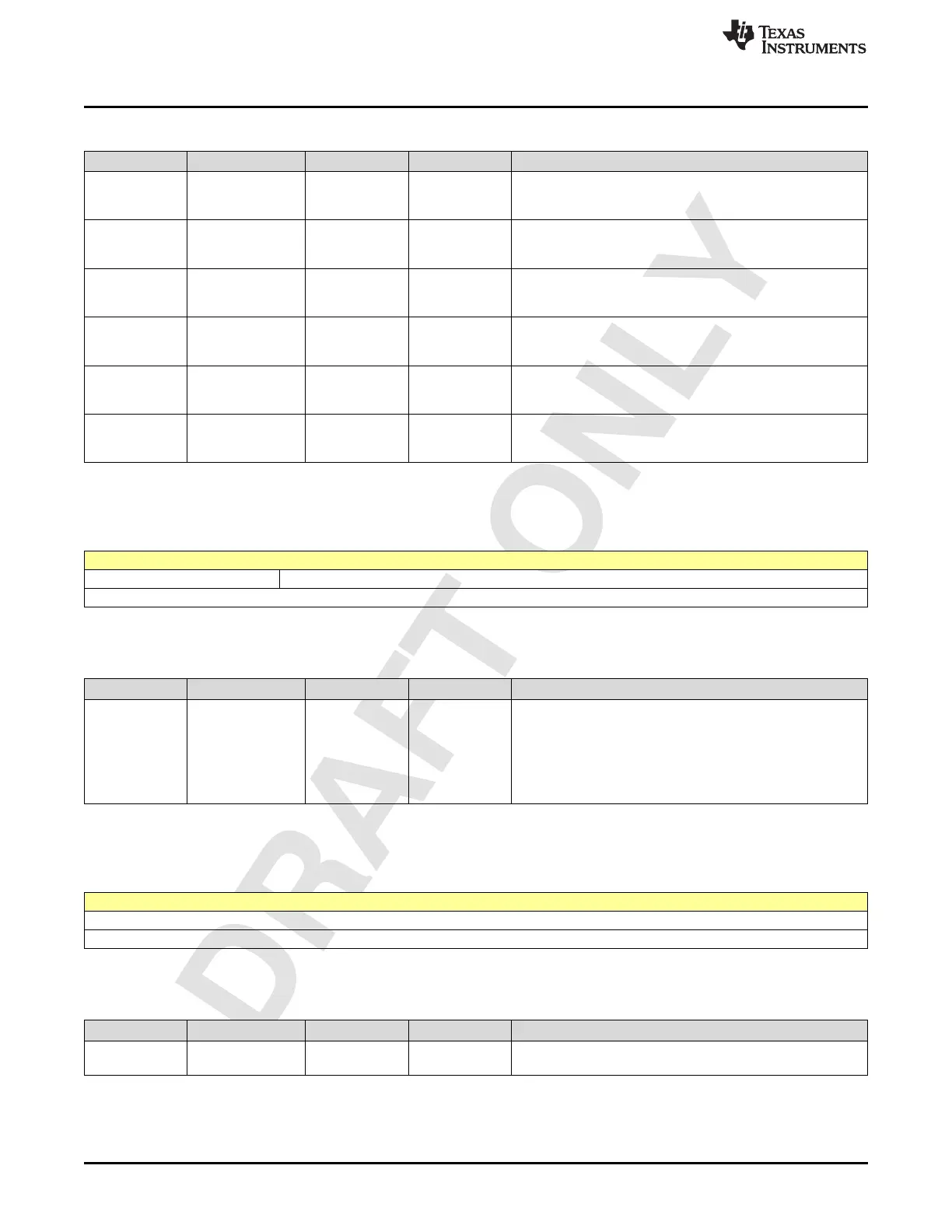

2.3.160 Register 181h (offset = 181h) [reset = 0h]

Figure 2-201. Register 181h

7 6 5 4 3 2 1 0

ADC_SYNC_N_POST_MUX

R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-204. Register 181 Field Descriptions

Bit Field Type Reset Description

7-0

ADC_SYNC_N_PO

ST_MUX

R 0h

Spi monitor of adc_sync_n values post sync_n mux. 8 bits

correspond to sync going to 8 lanes

Loading...

Loading...