Timing Controller Register Map

www.ti.com

964

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

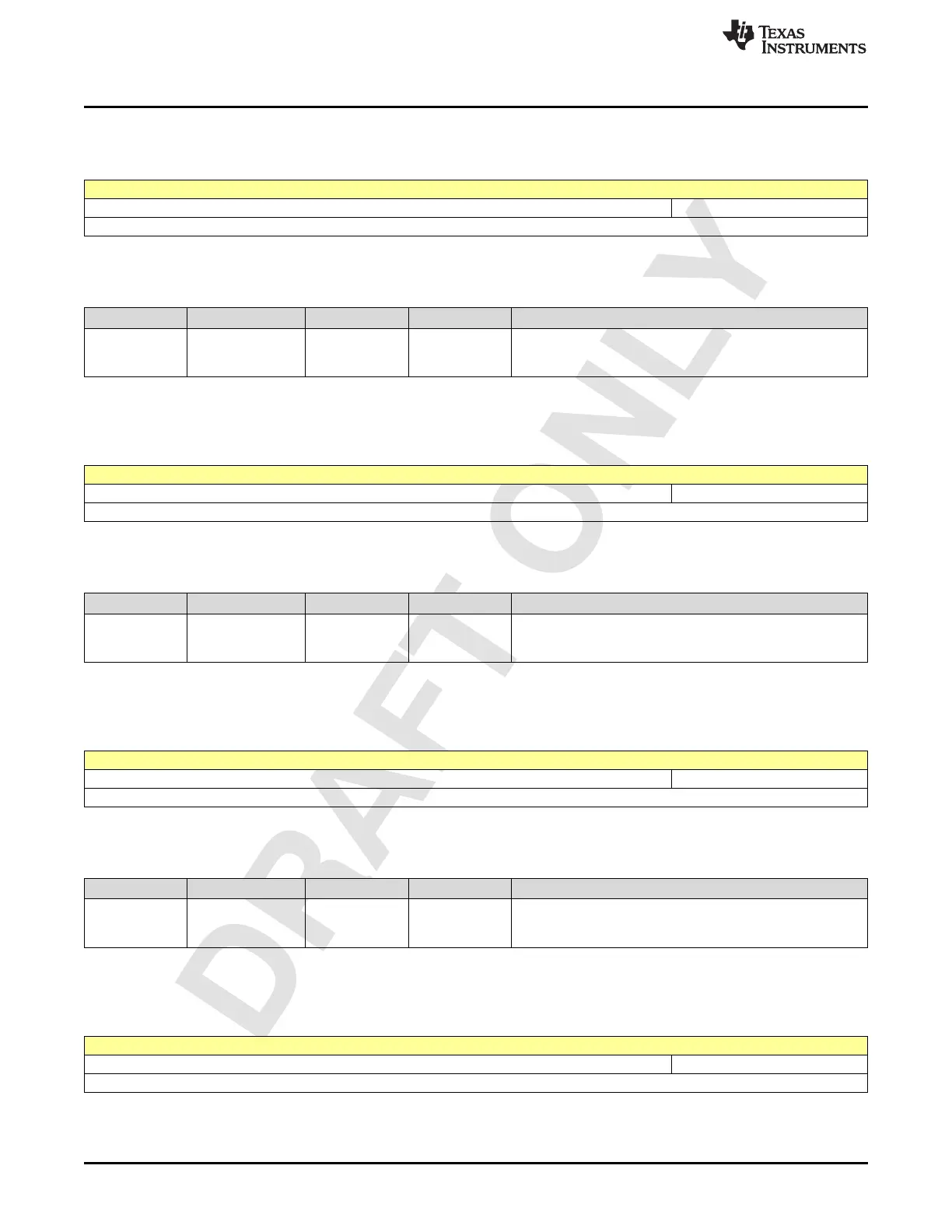

2.15.13 Register 90h (offset = 90h) [reset = 0h]

Figure 2-2220. Register 90h

7 6 5 4 3 2 1 0

ENABLE_TX_GAIN_SWAP_A

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2235. Register 90 Field Descriptions

Bit Field Type Reset Description

1-0

ENABLE_TX_GAIN

_SWAP_A

R/W 0h

Acts as an EN for txgswap for each bit of chA. If a bit of the

enable is 0, then the corresponding gain_swap bit will be

always 0.

2.15.14 Register 91h (offset = 91h) [reset = 0h]

Figure 2-2221. Register 91h

7 6 5 4 3 2 1 0

ENABLE_TX_GAIN_SWAP_B

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2236. Register 91 Field Descriptions

Bit Field Type Reset Description

1-0

ENABLE_TX_GAIN

_SWAP_B

R/W 0h

Acts as an EN for txgswap for each bit of chB. If a bit of the

enable is 0, then the corresponding gain_swap bit will be

always 0.

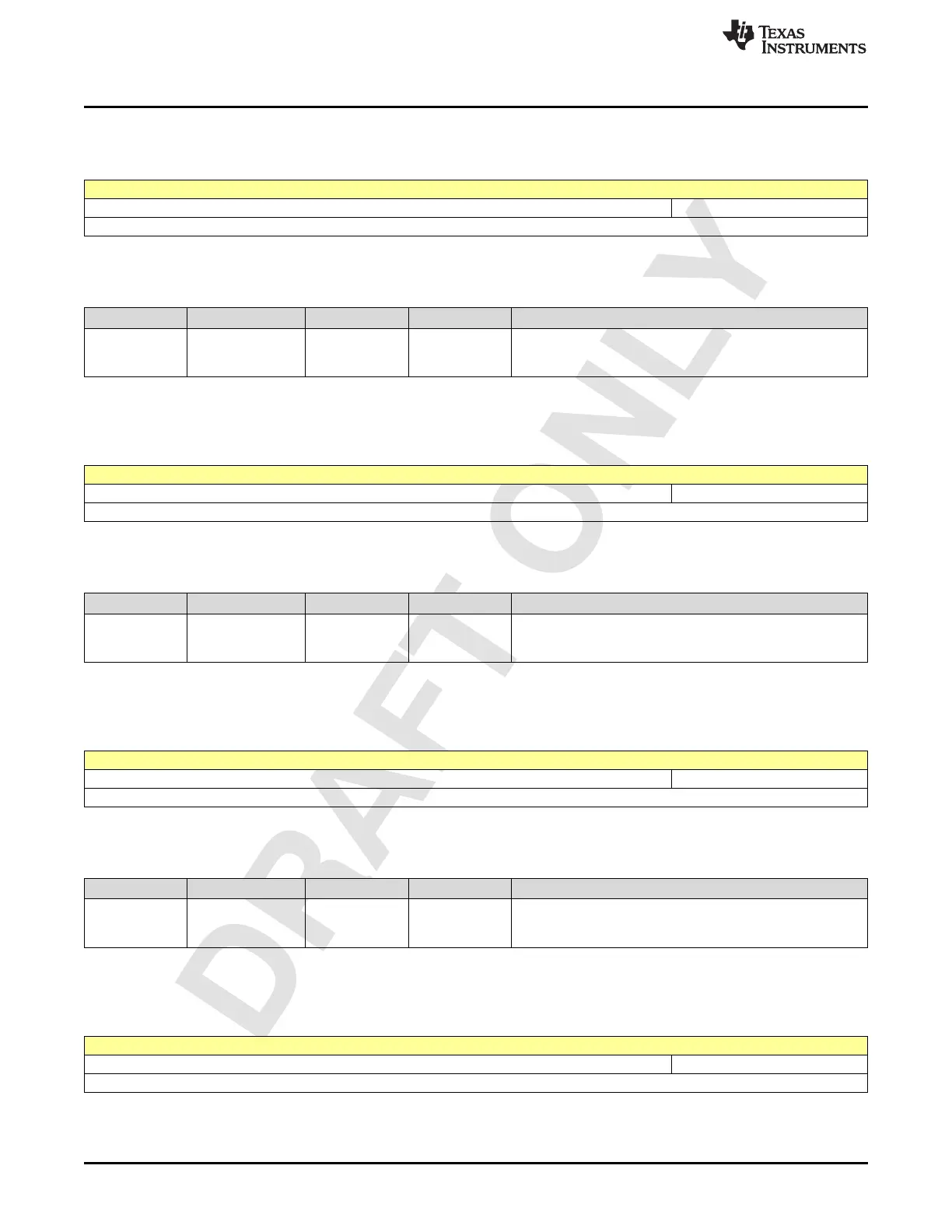

2.15.15 Register 92h (offset = 92h) [reset = 0h]

Figure 2-2222. Register 92h

7 6 5 4 3 2 1 0

ENABLE_TX_GAIN_SWAP_C

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-2237. Register 92 Field Descriptions

Bit Field Type Reset Description

1-0

ENABLE_TX_GAIN

_SWAP_C

R/W 0h

Acts as an EN for txgswap for each bit of chC. If a bit of the

enable is 0, then the corresponding gain_swap bit will be

always 0.

2.15.16 Register 93h (offset = 93h) [reset = 0h]

Figure 2-2223. Register 93h

7 6 5 4 3 2 1 0

ENABLE_TX_GAIN_SWAP_D

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...