RX Top Register Map

www.ti.com

832

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

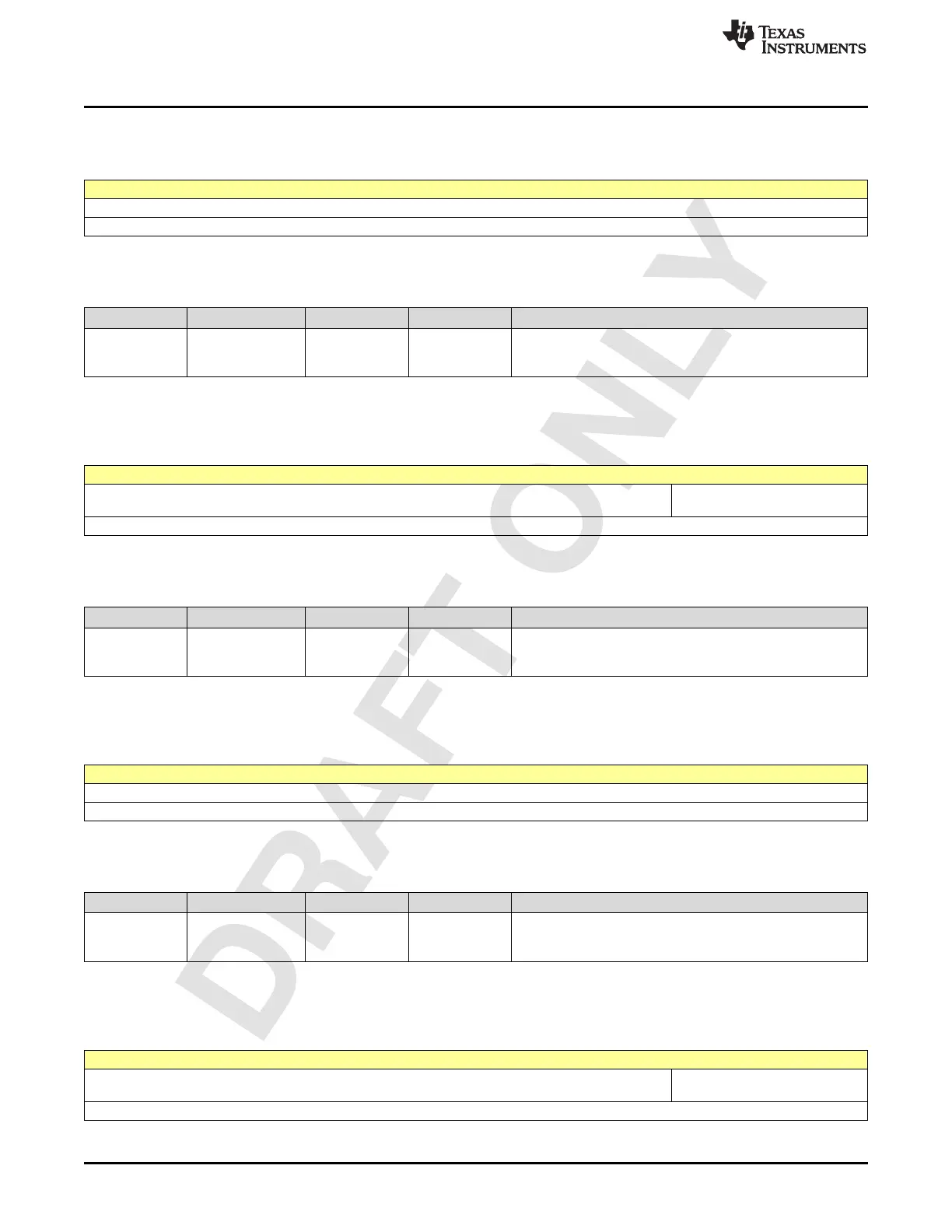

2.13.410 Register 5AEh (offset = 5AEh) [reset = 0h]

Figure 2-1822. Register 5AEh

7 6 5 4 3 2 1 0

RX_AGC_BAND1_LNA_PHASE25[7:0]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-1835. Register 5AE Field Descriptions

Bit Field Type Reset Description

7-0

RX_AGC_BAND1_

LNA_PHASE25[7:0

]

R/W 0h

LNA Phase for Band1 for temp index 25 in case of External

LNA Control , Phase for DVGA Index 57 in case of External

DVGA control

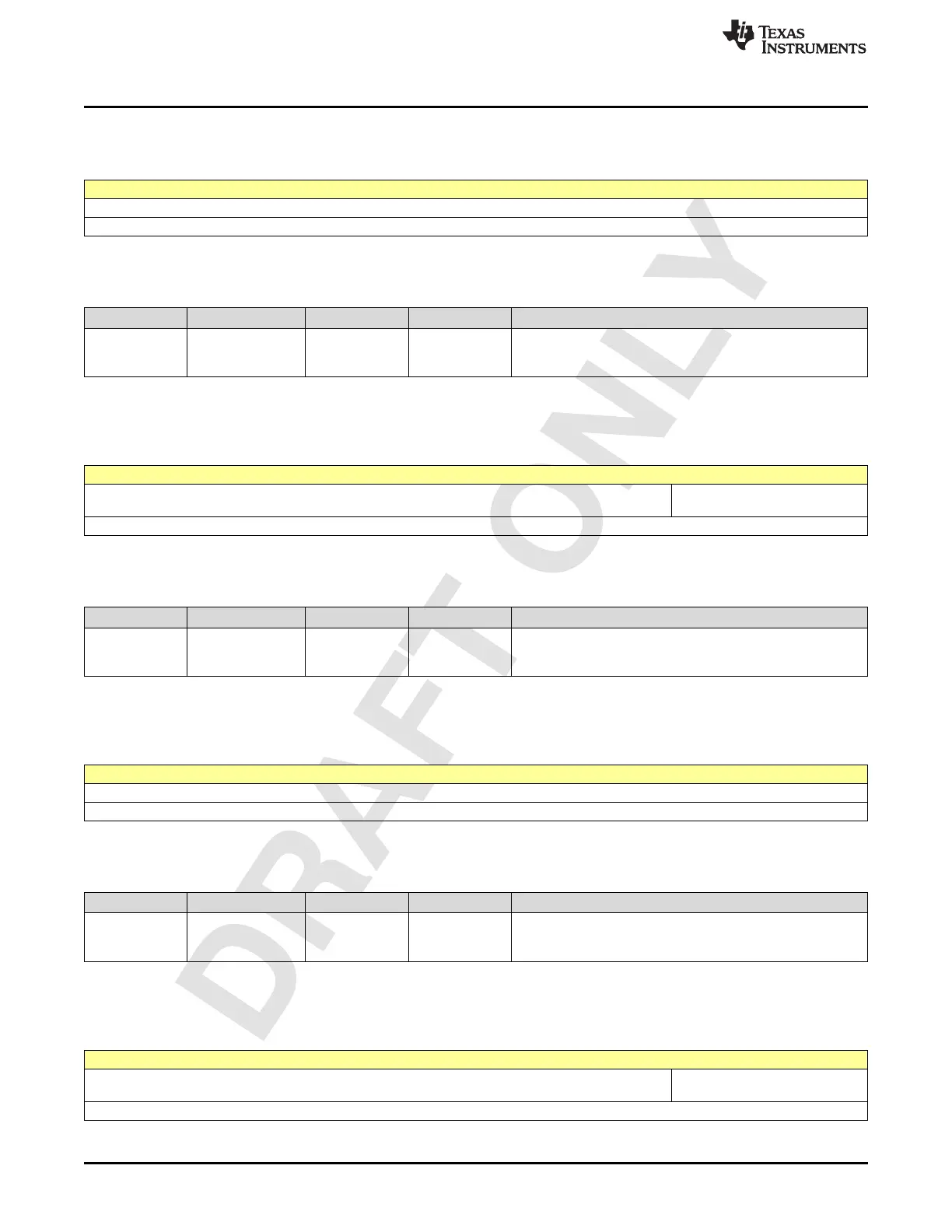

2.13.411 Register 5AFh (offset = 5AFh) [reset = 0h]

Figure 2-1823. Register 5AFh

7 6 5 4 3 2 1 0

RX_AGC_BAND1_LNA_PHASE

25[9:8]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-1836. Register 5AF Field Descriptions

Bit Field Type Reset Description

1-0

RX_AGC_BAND1_

LNA_PHASE25[9:8

]

R/W 0h

LNA Phase for Band1 for temp index 25 in case of External

LNA Control , Phase for DVGA Index 57 in case of External

DVGA control

2.13.412 Register 5B0h (offset = 5B0h) [reset = 0h]

Figure 2-1824. Register 5B0h

7 6 5 4 3 2 1 0

RX_AGC_BAND1_LNA_PHASE26[7:0]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-1837. Register 5B0 Field Descriptions

Bit Field Type Reset Description

7-0

RX_AGC_BAND1_

LNA_PHASE26[7:0

]

R/W 0h

LNA Phase for Band1 for temp index 26 in case of External

LNA Control , Phase for DVGA Index 58 in case of External

DVGA control

2.13.413 Register 5B1h (offset = 5B1h) [reset = 0h]

Figure 2-1825. Register 5B1h

7 6 5 4 3 2 1 0

RX_AGC_BAND1_LNA_PHASE

26[9:8]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...