www.ti.com

RX Top Register Map

837

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

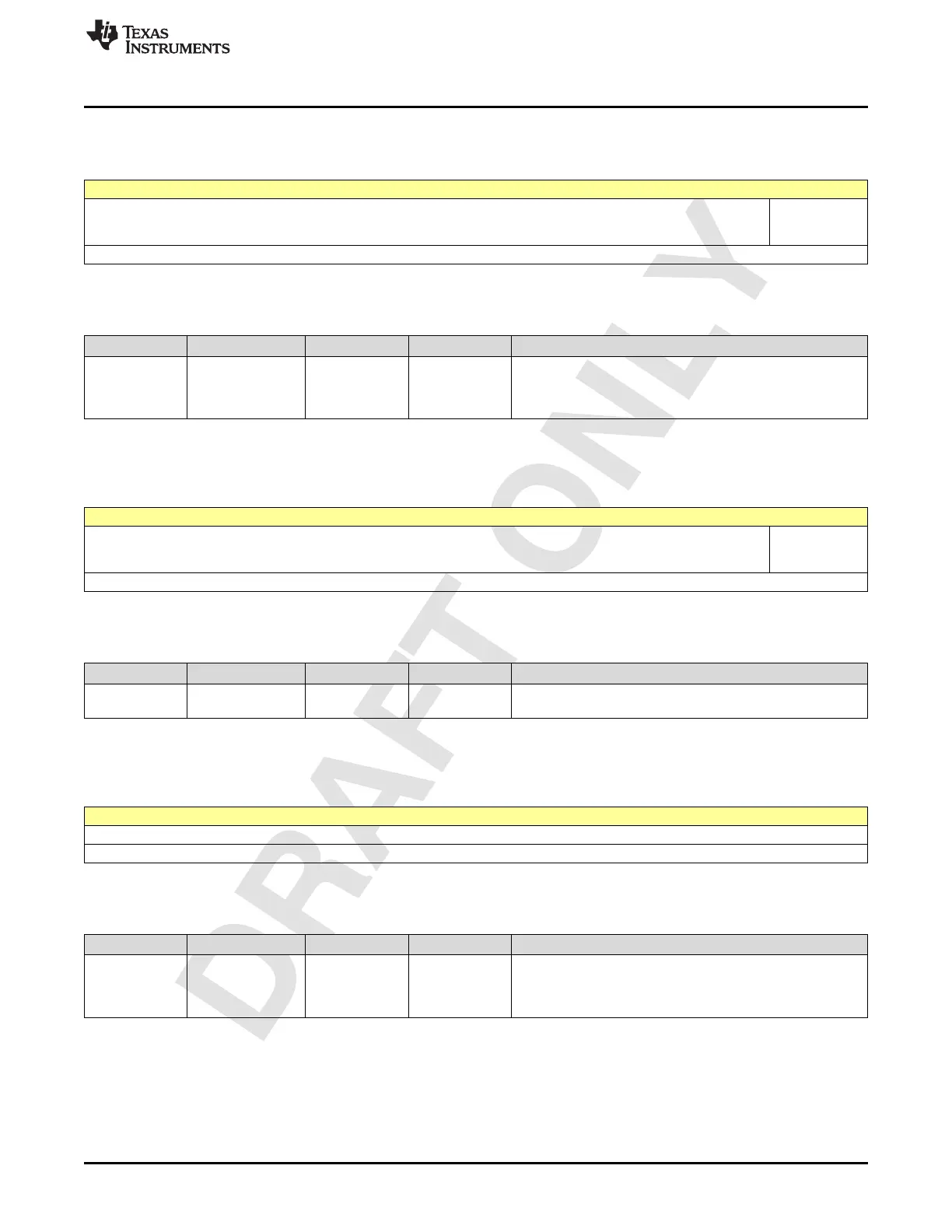

2.13.427 Register 5C2h (offset = 5C2h) [reset = 0h]

Figure 2-1839. Register 5C2h

7 6 5 4 3 2 1 0

RX_AGC_SWA

P_DVGA_SPI_

ORDER

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-1852. Register 5C2 Field Descriptions

Bit Field Type Reset Description

0-0

RX_AGC_SWAP_

DVGA_SPI_ORDE

R

R/W 0h

Controls which channel information is sent on first 6 bits of

DVGA transaction. If low information is DVGA gain of RXCHA

followed by RXCHB. If made high DVGA gain of RXCHB

followed by RXCHA

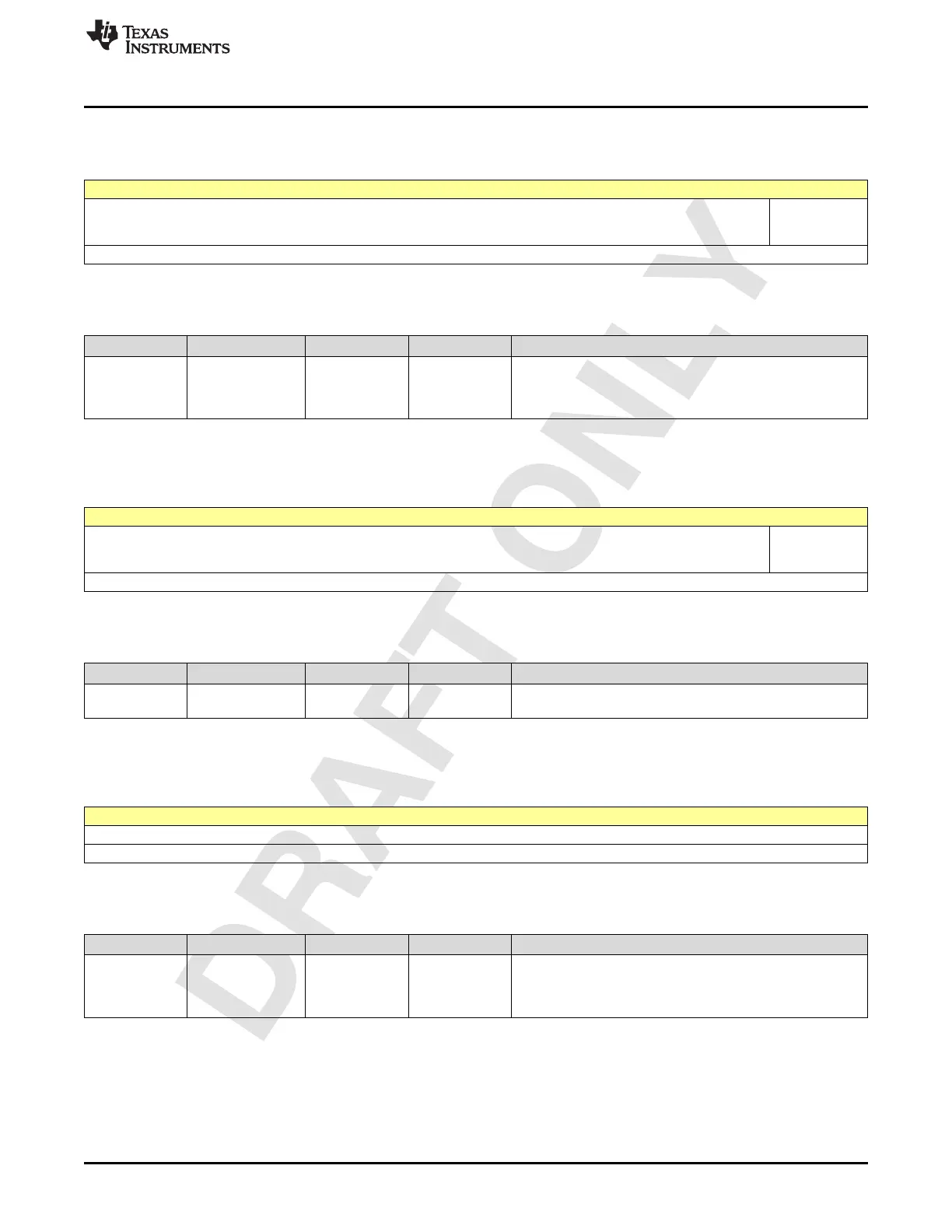

2.13.428 Register 5C4h (offset = 5C4h) [reset = 0h]

Figure 2-1840. Register 5C4h

7 6 5 4 3 2 1 0

RX_AGC_UPD

ATE_DET_STA

TUS

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-1853. Register 5C4 Field Descriptions

Bit Field Type Reset Description

0-0

RX_AGC_UPDATE

_DET_STATUS

R/W 0h

Update pulse for all detector read out status including Digital

peak, power, analog and band detectors

2.13.429 Register 5D0h (offset = 5D0h) [reset = 0h]

Figure 2-1841. Register 5D0h

7 6 5 4 3 2 1 0

RX_AGC_AVG_PWR_DET_SEEN[7:0]

R-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-1854. Register 5D0 Field Descriptions

Bit Field Type Reset Description

7-0

RX_AGC_AVG_P

WR_DET_SEEN[7:

0]

R 0h

Indicates average power seen by the power detector. Based

on pwr_det_read_sel corresponding power detector is

selected. Update pulse needs to be provided for reading this.

Power read will be equal to 10 * log (value read/65535)

Loading...

Loading...