ADC JESD Register Map

www.ti.com

376

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-504. Register 22 Field Descriptions

Bit Field Type Reset Description

7-3 0 R/W 0h Must read or write 0

2-0

SYSREF_JESD_M

ODE

R/W 1h

Determines how SYSREF is used in the JESD synchronizing

block.

000 = Don't use SYSREF pulse

001 = Use all SYSREF pulses

010 = Use only the next SYSREF pulse

011 = Skip one SYSREF pulse then use only the next one

100 = Skip one SYSREF pulse then use all pulses.

101 = skip two SYSREFs and then use one

110 = skip two SYSREFs and then use all

2.5.4 Register 23h (offset = 23h) [reset = Fh]

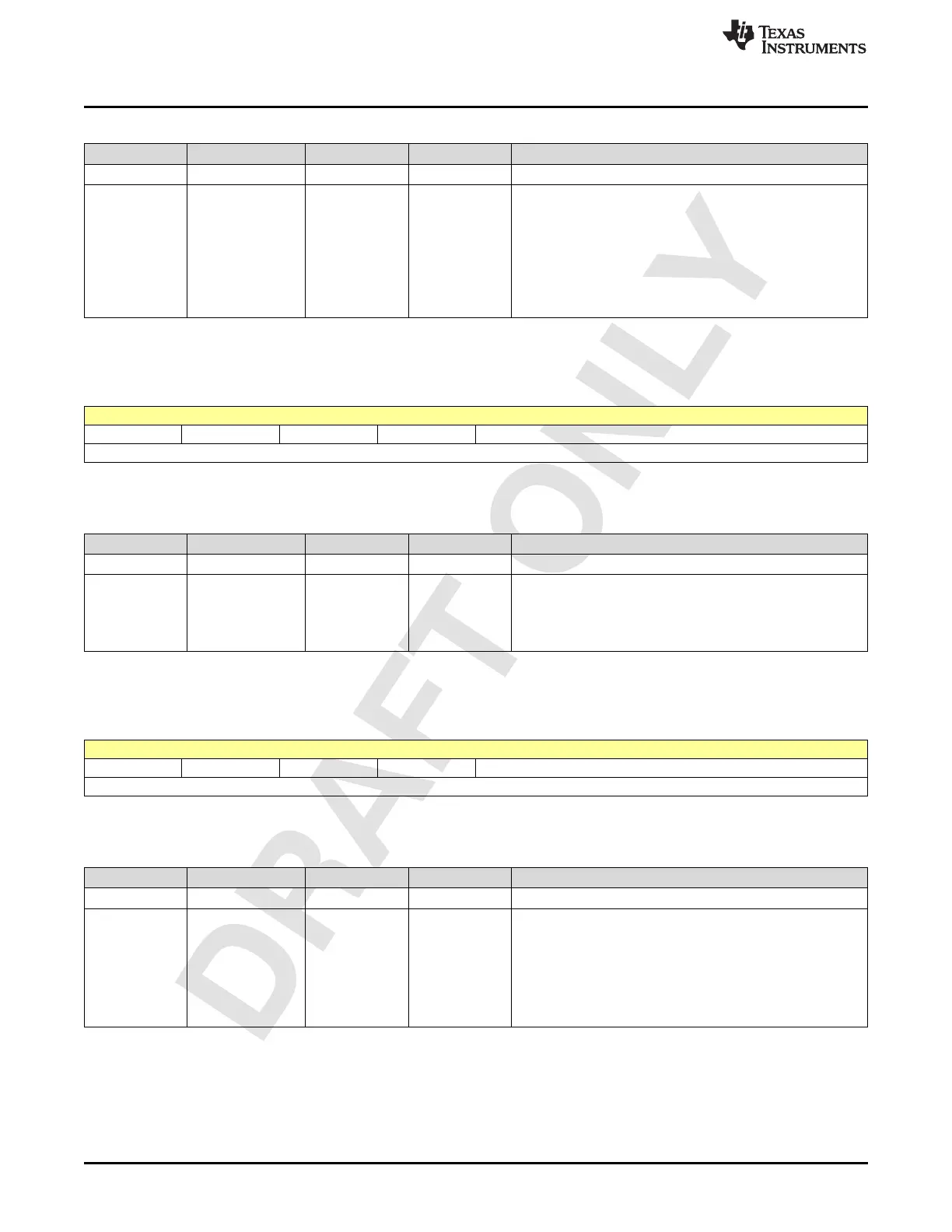

Figure 2-500. Register 23h

7 6 5 4 3 2 1 0

0 0 0 0 LANE_ENA

R/W-0h R/W-0h R/W-0h R/W-0h R/W-Fh

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-505. Register 23 Field Descriptions

Bit Field Type Reset Description

7-4 0 R/W 0h Must read or write 0

3-0 LANE_ENA R/W Fh

Turns on individual lanes:

bit 0 - STX1/5

bit 1 - STX2/6

bit 2 - STX3/7

bit 3 - STX4/8

2.5.5 Register 24h (offset = 24h) [reset = 0h]

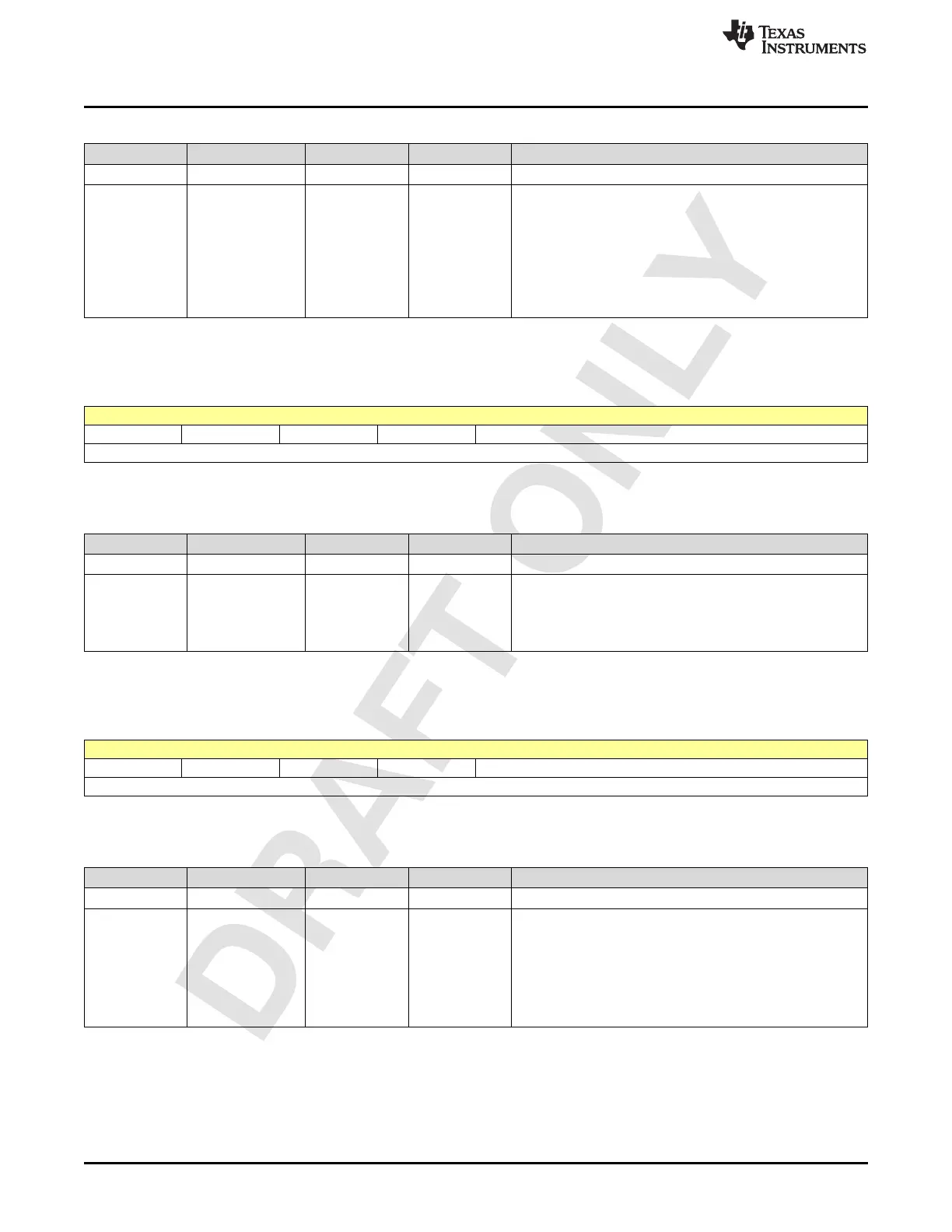

Figure 2-501. Register 24h

7 6 5 4 3 2 1 0

0 0 0 0 JESD_CLEAR_DATA

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-506. Register 24 Field Descriptions

Bit Field Type Reset Description

7-4 0 R/W 0h Must read or write 0

3-0

JESD_CLEAR_DA

TA

R/W 0h

Clears the JESD data going to serdes

1'b1 - Sends Test pattern Spi reg values on lane (No encoding

done, so no JESD STD is followed)

1'b0 - No change in lane-data

bit 0 - STX1/5

bit 1 - STX2/6

bit 2 - STX3/7

bit 3 - STX4/8

Loading...

Loading...