www.ti.com

ADC JESD Register Map

377

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

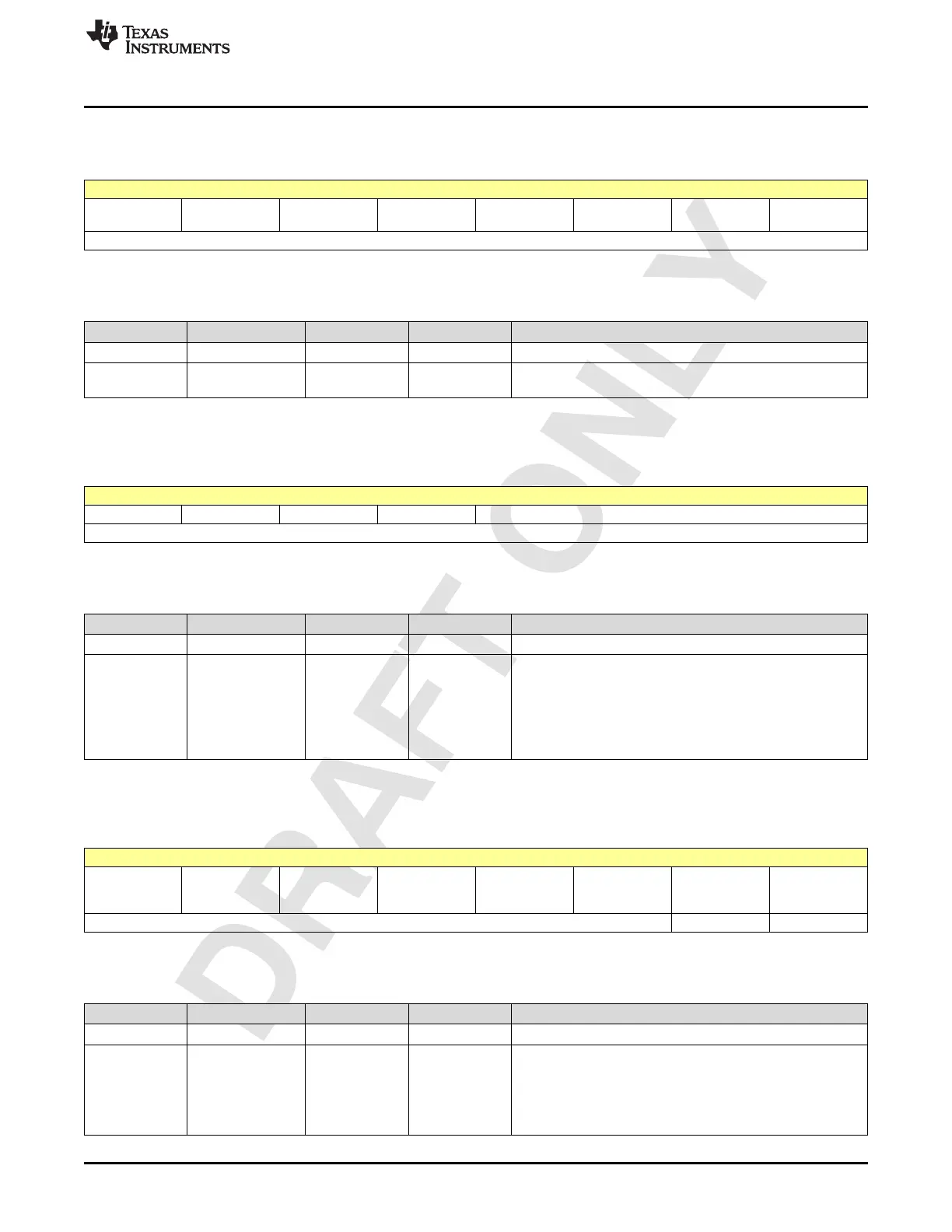

2.5.6 Register 26h (offset = 26h) [reset = 0h]

Figure 2-502. Register 26h

7 6 5 4 3 2 1 0

0 0 0 0 0 0 0 INIT_MAPPER

_ALIGN

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-507. Register 26 Field Descriptions

Bit Field Type Reset Description

7-1 0 R/W 0h Must read or write 0

0-0

INIT_MAPPER_ALI

GN

R/W 0h to reset mapper_align sticky bit.

2.5.7 Register 27h (offset = 27h) [reset = Fh]

Figure 2-503. Register 27h

7 6 5 4 3 2 1 0

0 0 0 0 MASK_INIT_STATE_TO_DATA_MUX

R/W-0h R/W-0h R/W-0h R/W-0h R/W-Fh

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-508. Register 27 Field Descriptions

Bit Field Type Reset Description

7-4 0 R/W 0h Must read or write 0

3-0

MASK_INIT_STAT

E_TO_DATA_MUX

R/W Fh

By default sysref aligned init_state is used to mask the data

going on lanes

If not needed, make it zero.

bit 0 - STX1/5

bit 1 - STX2/6

bit 2 - STX3/7

bit 3 - STX4/8

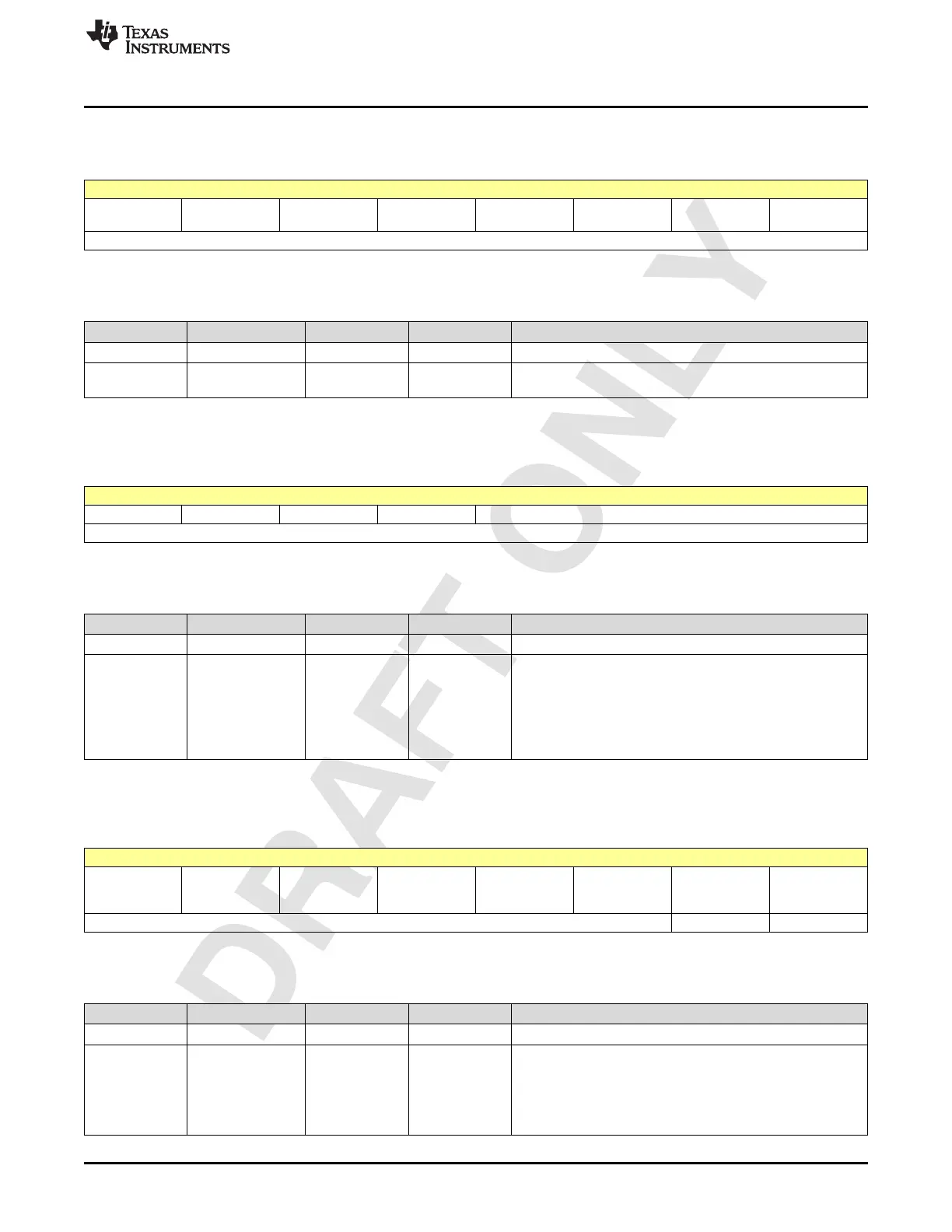

2.5.8 Register 2Ch (offset = 2Ch) [reset = 0h]

Figure 2-504. Register 2Ch

7 6 5 4 3 2 1 0

0 0 0 0 0 TDD_RX_FBZ_

DYN_SWITCH

_INV

TDD_RX_FBZ_

DYN_SWITCH

_OVR

TDD_RX_FBZ_

DYN_SWITCH

_VAL

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-509. Register 2C Field Descriptions

Bit Field Type Reset Description

7-3 0 R/W 0h Must read or write 0

2-2

TDD_RX_FBZ_DY

N_SWITCH_INV

R/W 0h

Relevant when jesd_system_mode is in TDD

When 1, polarity of the RX, FB dynamic switching signal is

inverted.

So, then inverted behavior

0 -> RX

1 -> FB

Loading...

Loading...