www.ti.com

ADC JESD Register Map

437

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

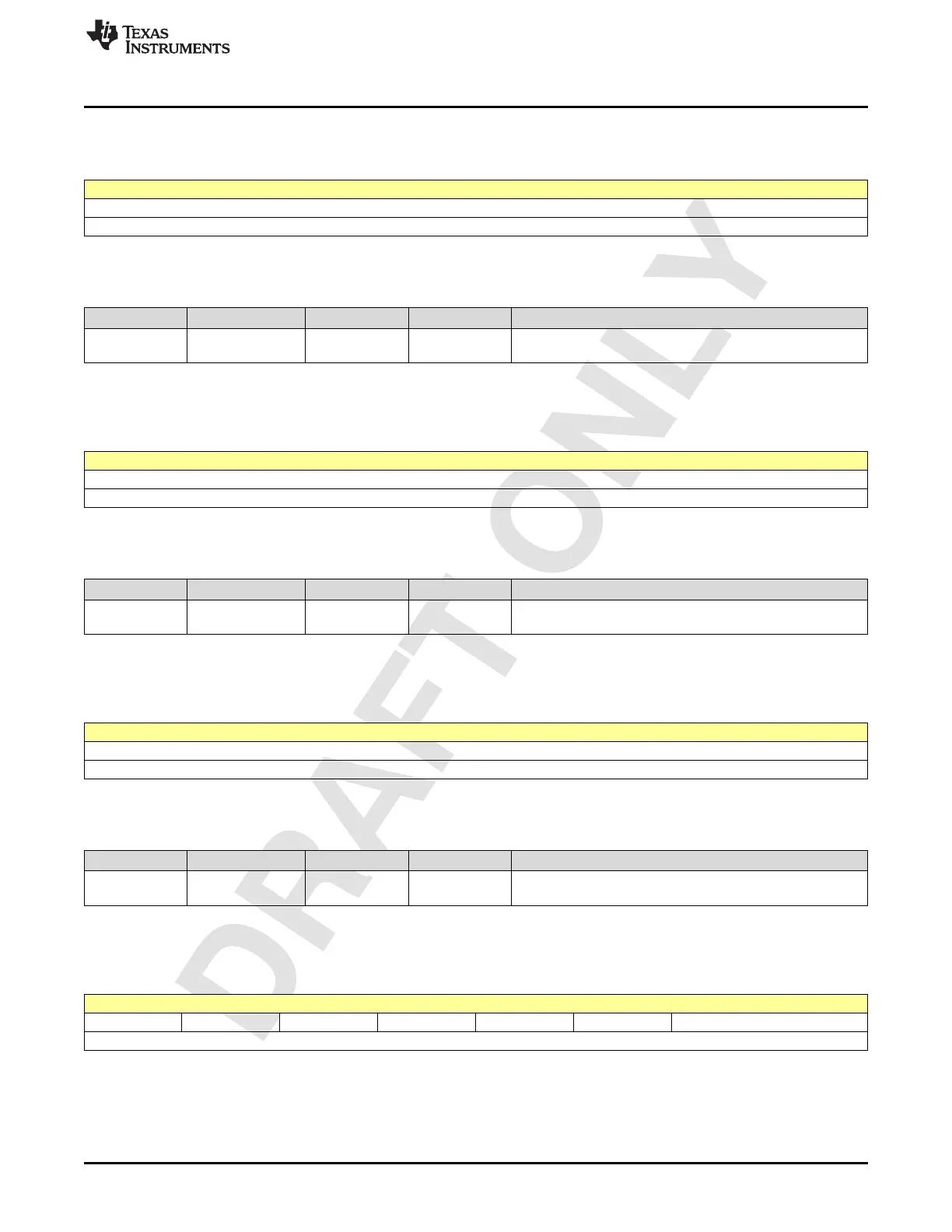

2.5.151 Register D8h (offset = D8h) [reset = 0h]

Figure 2-647. Register D8h

7 6 5 4 3 2 1 0

SCR_64B_INITVAL[39:32]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-652. Register D8 Field Descriptions

Bit Field Type Reset Description

7-0

SCR_64B_INITVAL

[39:32]

R/W 0h

58 bit inital value used by 64b scrambler (1+x^39+x^58)

Relevant for JESD-C

2.5.152 Register D9h (offset = D9h) [reset = 0h]

Figure 2-648. Register D9h

7 6 5 4 3 2 1 0

SCR_64B_INITVAL[47:40]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-653. Register D9 Field Descriptions

Bit Field Type Reset Description

7-0

SCR_64B_INITVAL

[47:40]

R/W 0h

58 bit inital value used by 64b scrambler (1+x^39+x^58)

Relevant for JESD-C

2.5.153 Register DAh (offset = DAh) [reset = 0h]

Figure 2-649. Register DAh

7 6 5 4 3 2 1 0

SCR_64B_INITVAL[55:48]

R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-654. Register DA Field Descriptions

Bit Field Type Reset Description

7-0

SCR_64B_INITVAL

[55:48]

R/W 0h

58 bit inital value used by 64b scrambler (1+x^39+x^58)

Relevant for JESD-C

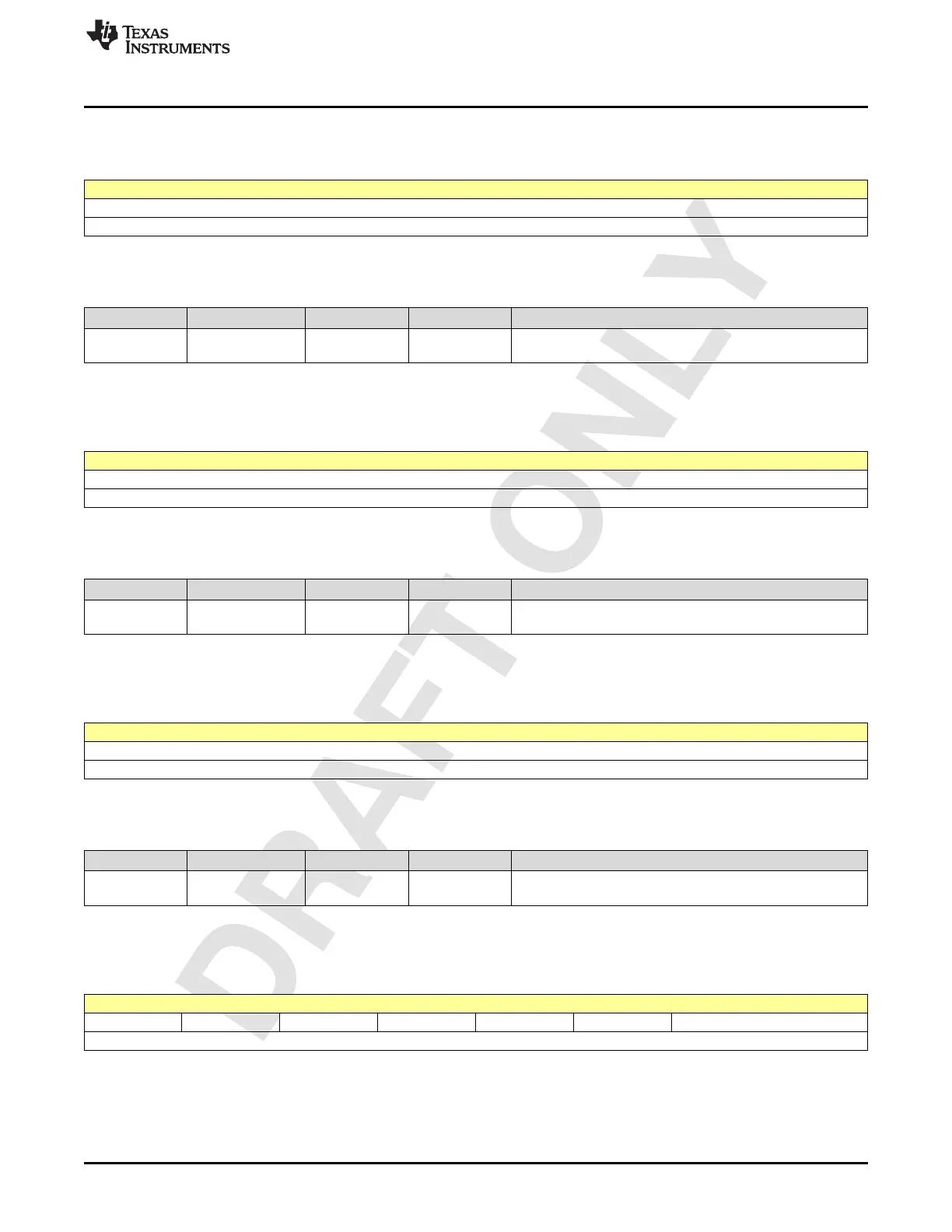

2.5.154 Register DBh (offset = DBh) [reset = 1h]

Figure 2-650. Register DBh

7 6 5 4 3 2 1 0

0 0 0 0 0 0 SCR_64B_INITVAL[57:56]

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-1h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...