ANA_4T4R Register Map

www.ti.com

536

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-934. Register 111 Field Descriptions

Bit Field Type Reset Description

7-3 0 R/W 0h Must read or write 0

2-0

CTL_OUTDIV_DIV

_TX

R/W 0h

Divider before the DAC after PLL. Normally this is 0 except

when the divn chosed..

2.7.7 Register 112h (offset = 112h) [reset = 1h]

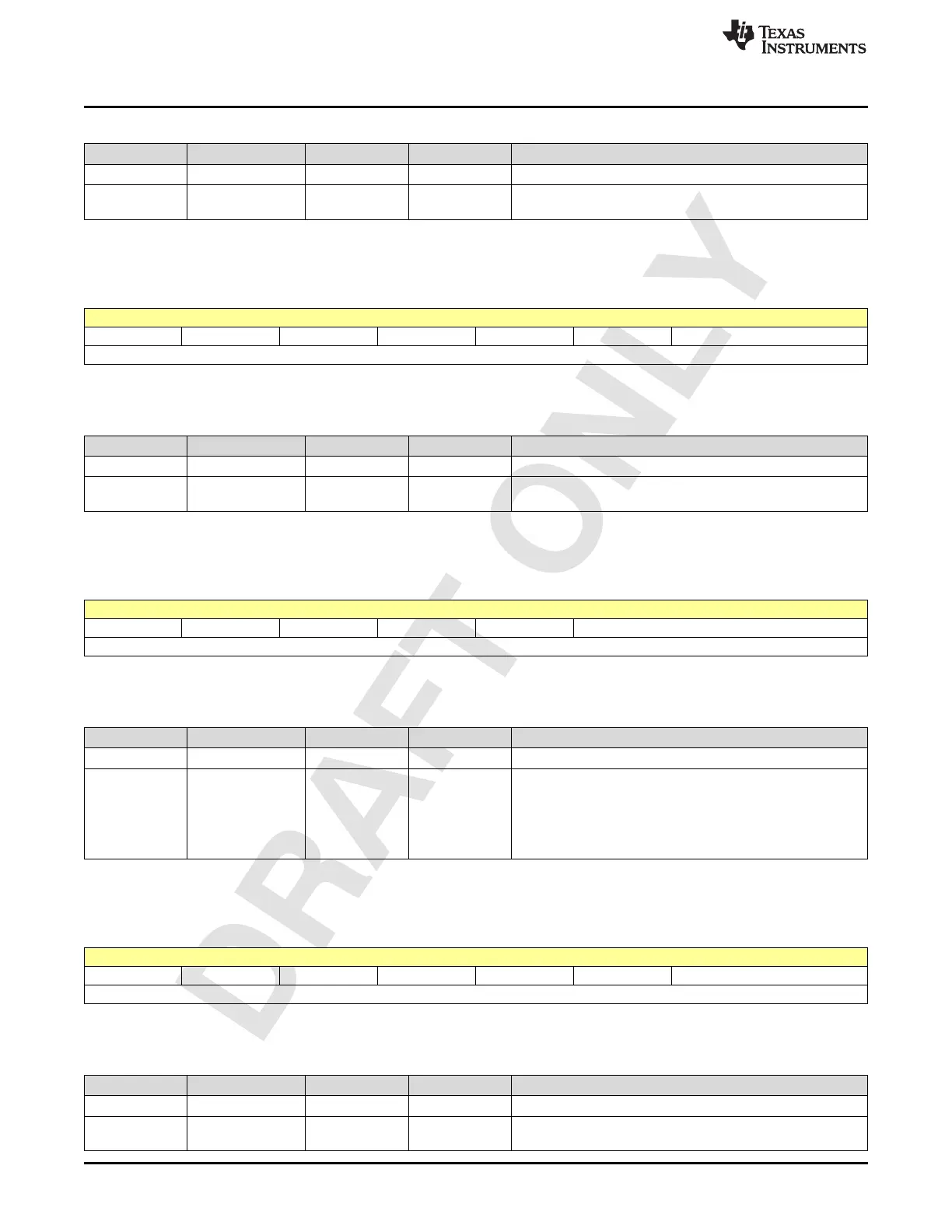

Figure 2-928. Register 112h

7 6 5 4 3 2 1 0

0 0 0 0 0 0 CTL_OUTDIV_MUX_RX

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-1h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-935. Register 112 Field Descriptions

Bit Field Type Reset Description

7-2 0 R/W 0h Must read or write 0

1-0

CTL_OUTDIV_MU

X_RX

R/W 1h

Mux for chosing rx clock. Similar to tx mux. usually here divn

is chosen.

2.7.8 Register 113h (offset = 113h) [reset = 2h]

Figure 2-929. Register 113h

7 6 5 4 3 2 1 0

0 0 0 0 0 CTL_OUTDIV_DIV_RX

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-2h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-936. Register 113 Field Descriptions

Bit Field Type Reset Description

7-3 0 R/W 0h Must read or write 0

2-0

CTL_OUTDIV_DIV

_RX

R/W 2h

Division factor for the outdiv.

1 - > 2

2 - > 3,

3 - > 4,

4 - > 5,

5 - > 6.

2.7.9 Register 114h (offset = 114h) [reset = 1h]

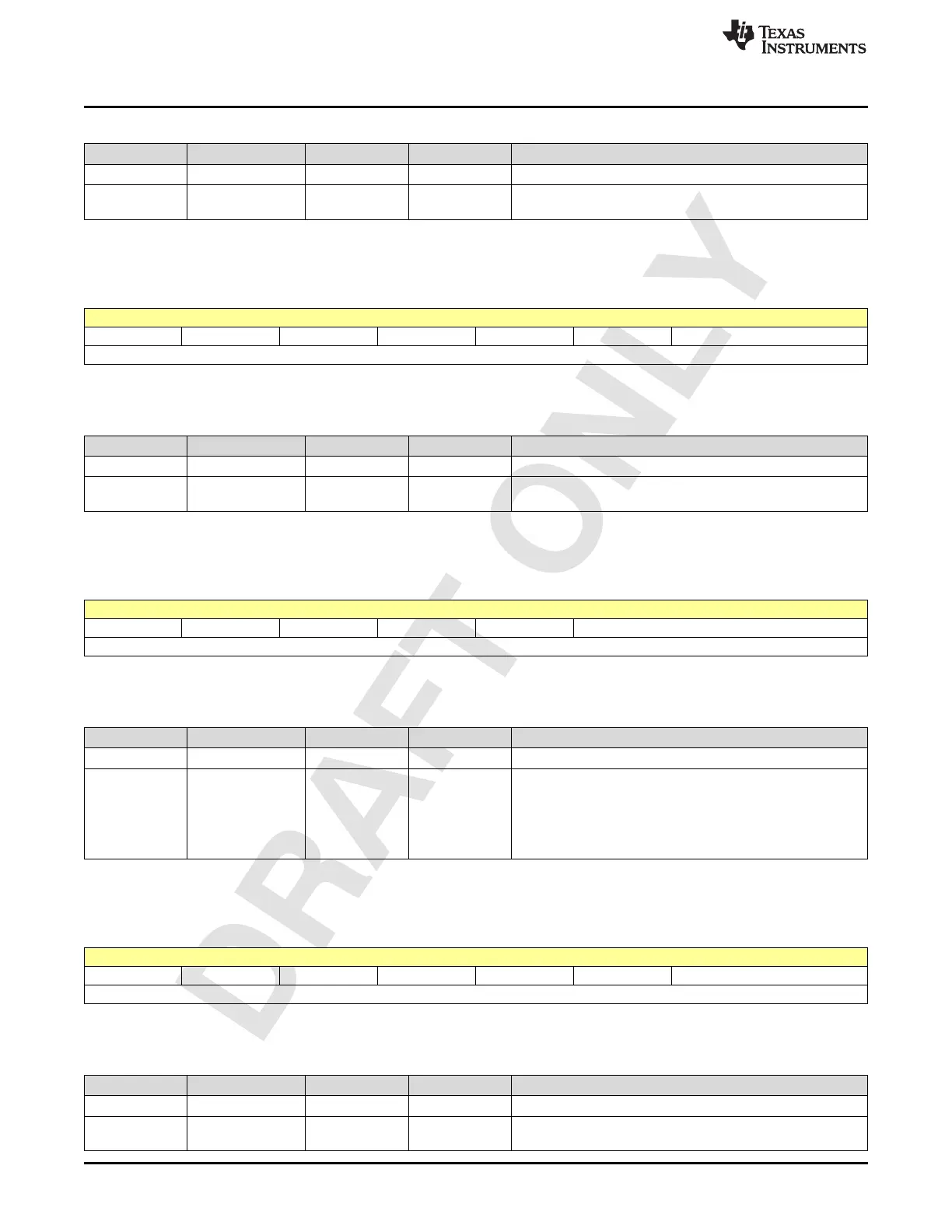

Figure 2-930. Register 114h

7 6 5 4 3 2 1 0

0 0 0 0 0 0 CTL_OUTDIV_MUX_FB

R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-0h R/W-1h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-937. Register 114 Field Descriptions

Bit Field Type Reset Description

7-2 0 R/W 0h Must read or write 0

1-0

CTL_OUTDIV_MU

X_FB

R/W 1h

Similar to the RX and TX. However here MSB is always 0. As

the other mux already happened in tx.

Loading...

Loading...