SERDES Register Map

www.ti.com

476

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

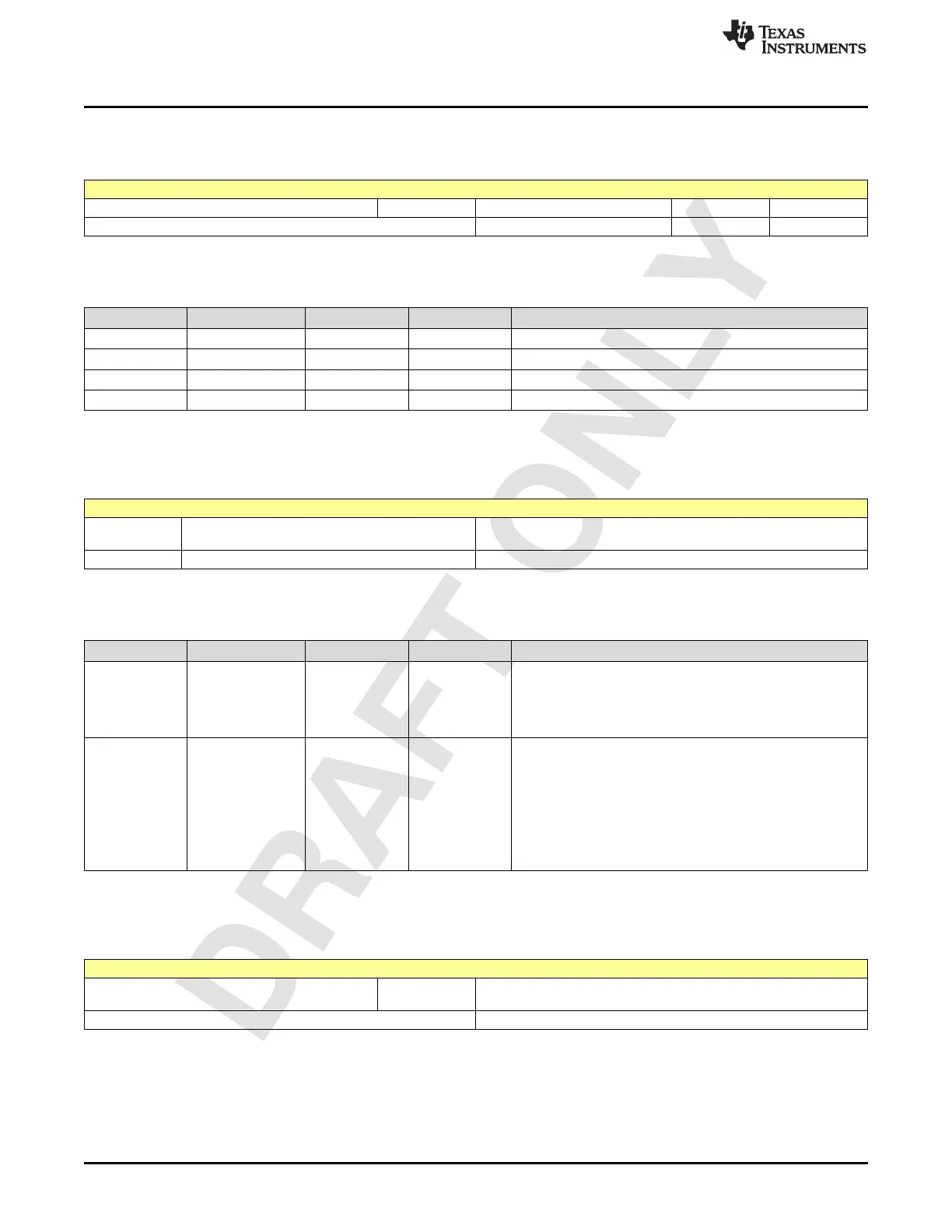

2.6.30 Register 4039h (offset = 4039h) [reset = 0h]

Figure 2-744. Register 4039h

7 6 5 4 3 2 1 0

OWEN_KF OW_KF OWEN_KP OW_KP[2]

R/W-0h R/W-0h R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-750. Register 4039 Field Descriptions

Bit Field Type Reset Description

4-4 OWEN_KF R/W 0h Overwrite enable signal for OW_KF.

3-2 OW_KF R/W 0h Overwrite value for KF. Format U2.0

1-1 OWEN_KP R/W 0h Overwrite enable signal for OW_KP.

0-0 OW_KP[2] R/W 0h Overwrite value for KP. Format U3.0

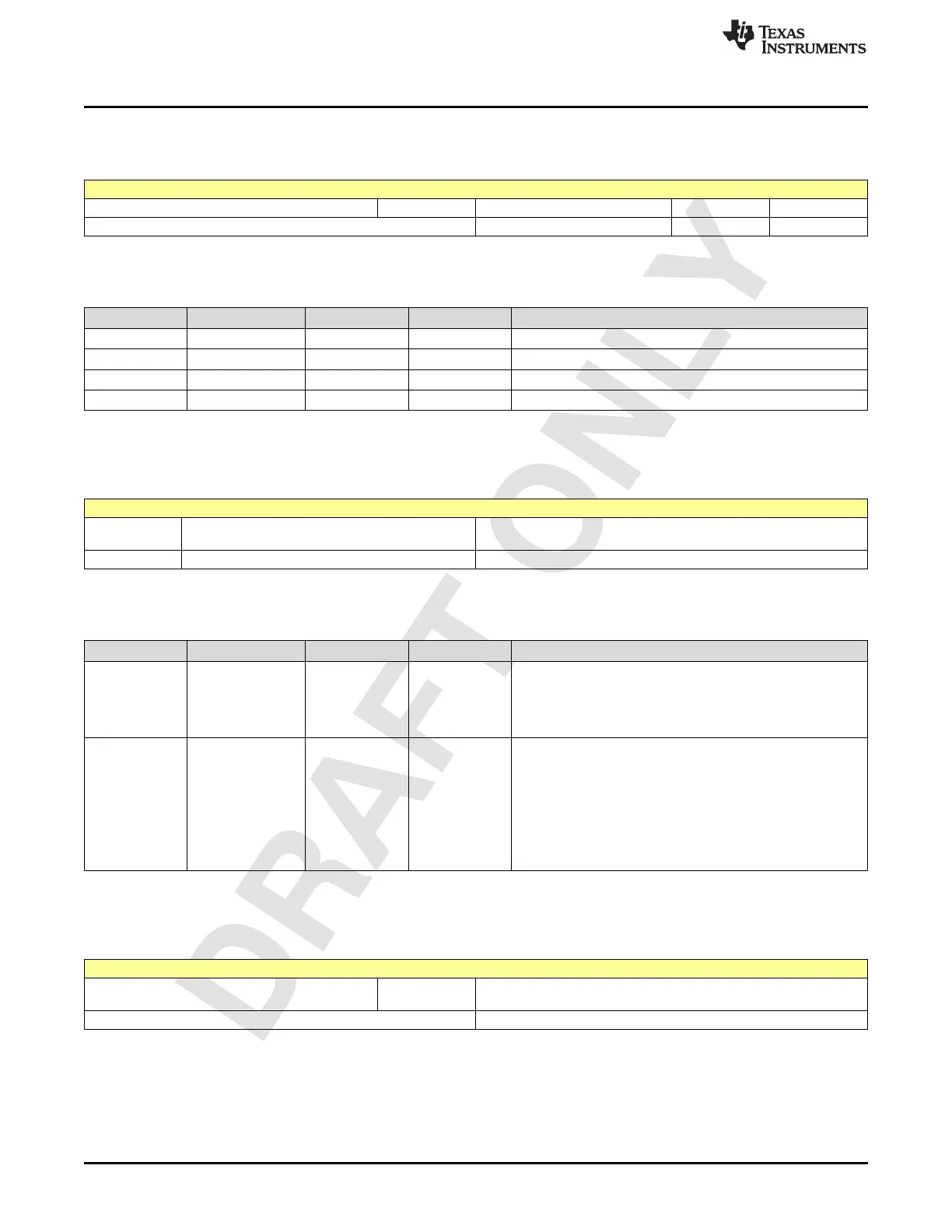

2.6.31 Register 403Ah (offset = 403Ah) [reset = 0h]

Figure 2-745. Register 403Ah

7 6 5 4 3 2 1 0

CTLE_OVERRI

DE_EN

CTLE_OVERRIDE_VAL

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-751. Register 403A Field Descriptions

Bit Field Type Reset Description

7-7

CTLE_OVERRIDE

_EN

R/W 0h

When enabled, the CTLE setting is programmed with the

override values and no adaptation occurs. For use in testing

only.

0h: Override disabled

1h: Override enabled

6-4

CTLE_OVERRIDE

_VAL

R/W 0h

CTLE value written when CTLE_OVERRIDE_EN is enabled

0h: 17.5dB

1h: 15.0dB

2h: 12.5dB

3h: 10.0dB

4h: 7.5dB

5h: 5.0dB

6h: 2.5dB

7h: 0.0dB

2.6.32 Register 403Bh (offset = 403Bh) [reset = 0h]

Figure 2-746. Register 403Bh

7 6 5 4 3 2 1 0

OWEN_DAC_S

EL

OW_DAC_SEL

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Loading...

Loading...