www.ti.com

JESD_SUBCHIP Register Map

235

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

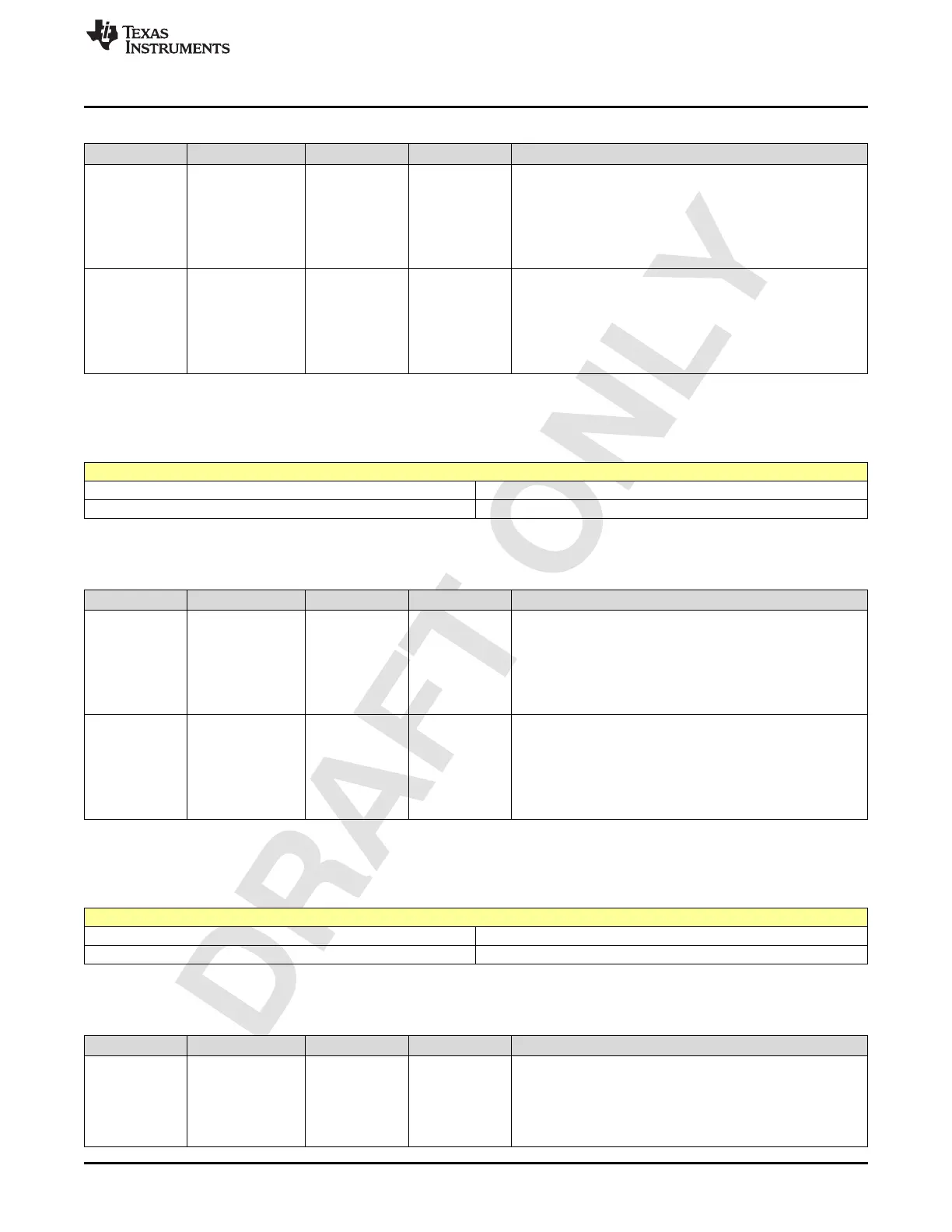

Table 2-175. Register 156 Field Descriptions

Bit Field Type Reset Description

7-4

TXB_DAC_CLK_E

N_VAL

R/W Fh

Register to gate the TXB clocks used internally and going to

TX_TOP. Need to be used along with 'txb_dac_clk_en_ovr'

register

bit0 - TXB_B0_I

bit1 - TXB_B0_Q

bit2 - TXB_B1_I

bit3 - TXB_B1_Q

3-0

TXA_DAC_CLK_E

N_VAL

R/W Fh

Register to gate the TXA clocks used internally and going to

TX_TOP. Need to be used along with 'txa_dac_clk_en_ovr'

register

bit0 - TXA_B0_I

bit1 - TXA_B0_Q

bit2 - TXA_B1_I

bit3 - TXA_B1_Q

2.3.132 Register 157h (offset = 157h) [reset = FFh]

Figure 2-173. Register 157h

7 6 5 4 3 2 1 0

TXD_DAC_CLK_EN_VAL TXC_DAC_CLK_EN_VAL

R/W-Fh R/W-Fh

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-176. Register 157 Field Descriptions

Bit Field Type Reset Description

7-4

TXD_DAC_CLK_E

N_VAL

R/W Fh

Register to gate the TXD clocks used internally and going to

TX_TOP. Need to be used along with 'txd_dac_clk_en_ovr'

register

bit0 - TXD_B0_I

bit1 - TXD_B0_Q

bit2 - TXD_B1_I

bit3 - TXD_B1_Q

3-0

TXC_DAC_CLK_E

N_VAL

R/W Fh

Register to gate the TXC clocks used internally and going to

TX_TOP. Need to be used along with 'txc_dac_clk_en_ovr'

register

bit0 - TXC_B0_I

bit1 - TXC_B0_Q

bit2 - TXC_B1_I

bit3 - TXC_B1_Q

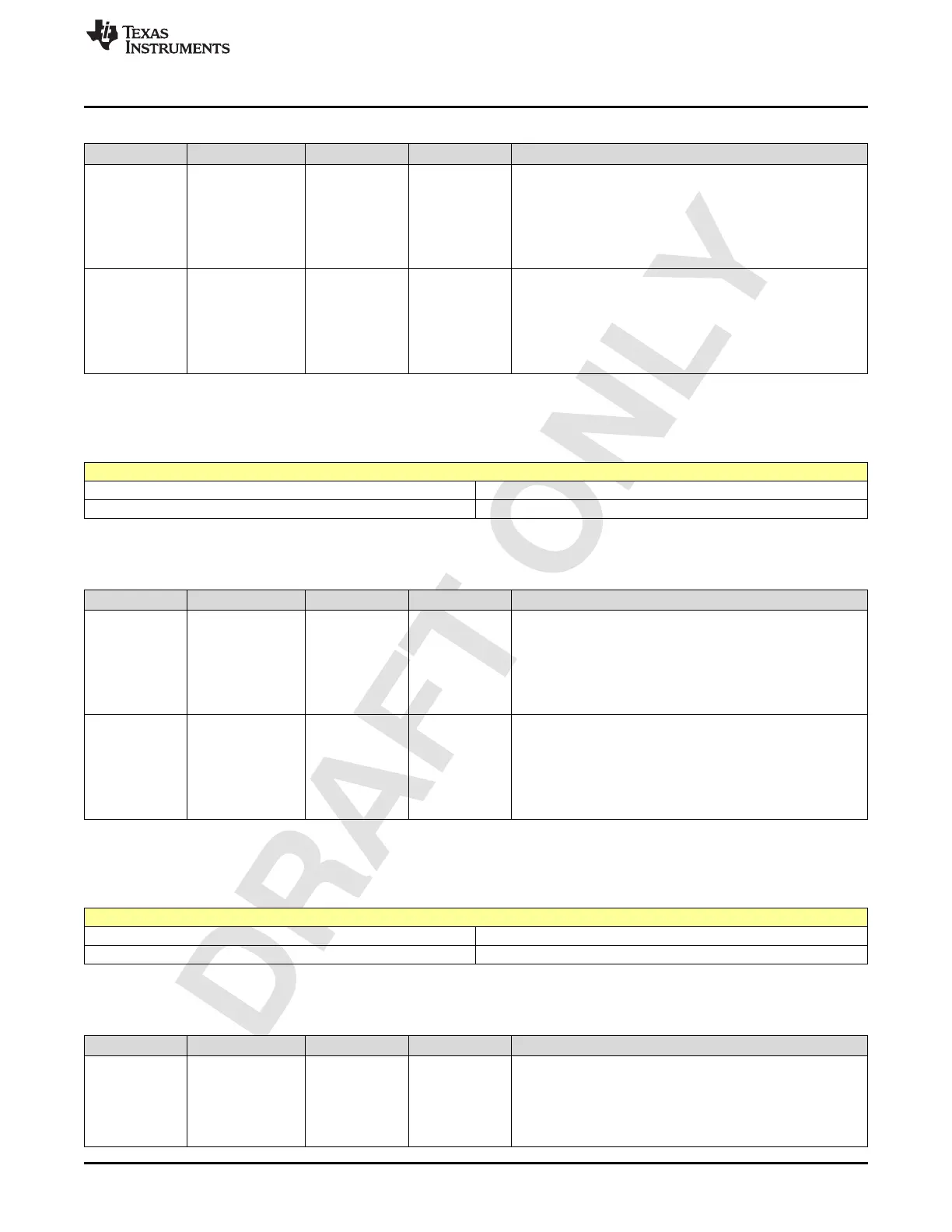

2.3.133 Register 158h (offset = 158h) [reset = 0h]

Figure 2-174. Register 158h

7 6 5 4 3 2 1 0

SERDESAB_LOS_INDICATOR_MASK SERDESAB_LOS_INDICATOR_CLEAR

R/W-0h R/W-0h

LEGEND: R/W = Read/Write; W = Write only; -n = value after reset

Table 2-177. Register 158 Field Descriptions

Bit Field Type Reset Description

7-4

SERDESAB_LOS_

INDICATOR_MAS

K

R/W 0h

register to mask SerdesAB SRX1, SRX2, SRX3 and SRX4

LOS indicator register bits

[3] = mask SRX4 LOS indicator

[2] = mask SRX3 LOS indicator

[1] = mask SRX2 LOS indicator

[0] = mask SRX1 LOS indicator

Loading...

Loading...