DAC JESD Register Map

www.ti.com

264

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

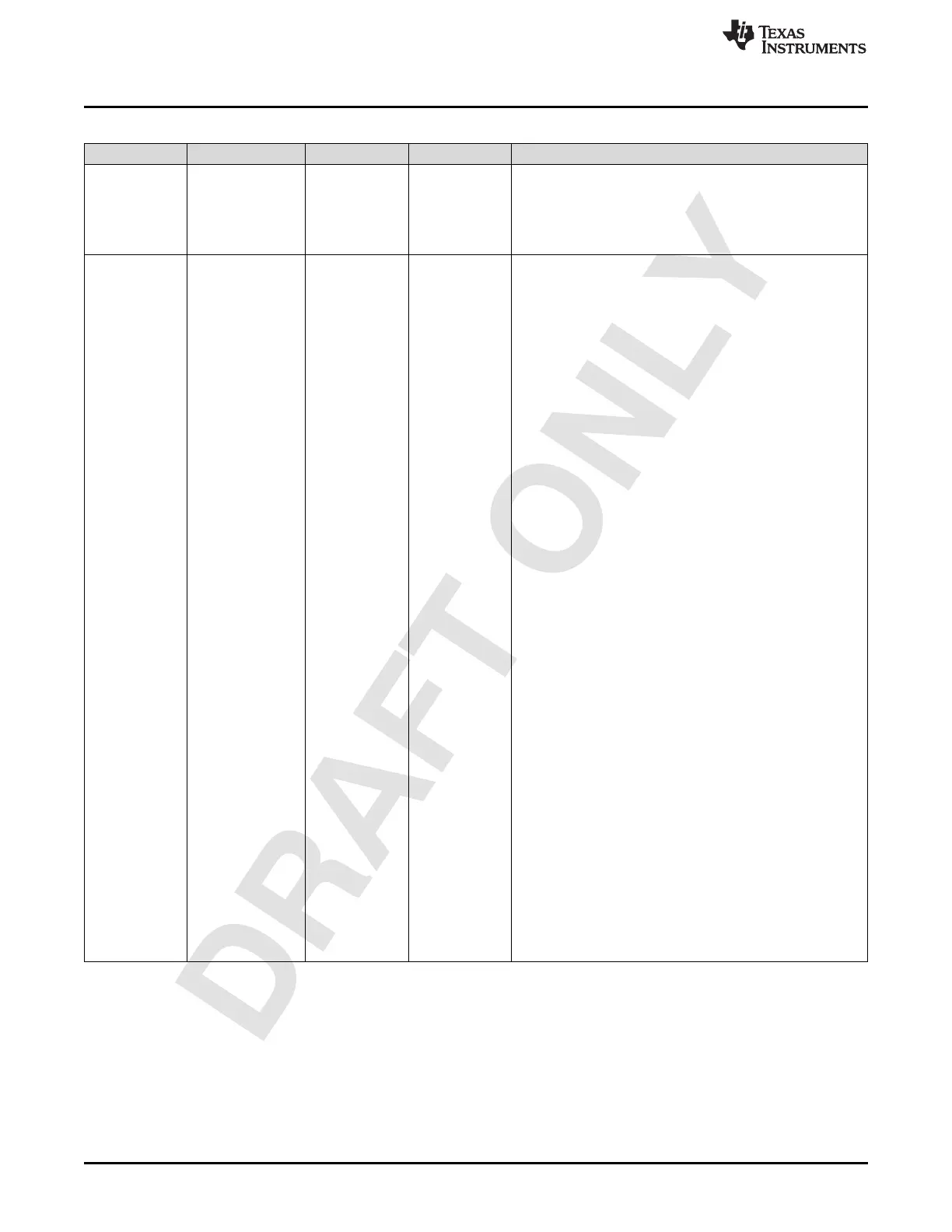

Table 2-237. Register 23 Field Descriptions

Bit Field Type Reset Description

7-6

LINK1_JESD_SAM

PLE_MODE

R/W 1h

Defines the number of parallel samples to be given out in

duc_clk to tx_top from lanes[2:3]/[6:7]

0 : DB,S=1

1 : SB,S=1

2 : SB,S=2

3 : SB,S=4

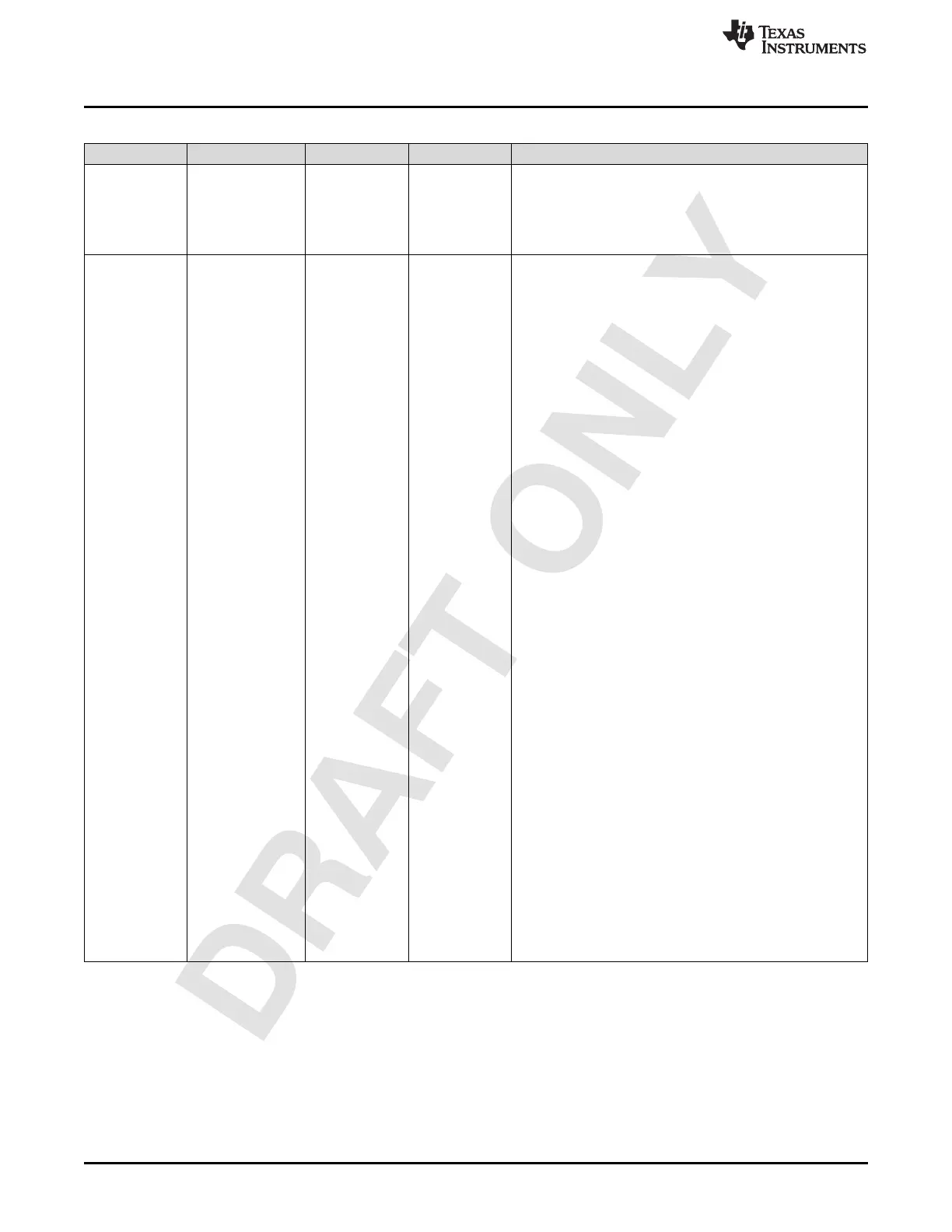

5-0

LINK1_JESD_MOD

E

R/W 5h

Defines the LMFSHd mode for path for lanes[2:3]/[6:7] path

0 : 24410

1 : 14810

2 : 14610

3 : 24610

4 : 1-4-12-1-0

5 : 44210

6 : 12820

7 : 48410

8 : 28810

9 : 28610

10 : 48610

11 : 2-8-12-1-0

12 : 24820

13 : 48310

14 : 24310

15 : 44310

16 : 1-8-12-1-0

17 : 1-8-16-1-0

18 : 42111

19 : 42220

20 : NA

21 : NA

22 : 22210

23 : 12310

24 : 22310

25 : 12410

26 : 12610

27 : 48820

28 : 4-16-8-1-0

29 : 2-16-12-1-0

30 : 4-16-12-1-0

31 : 2-16-16-1-0

32 : 1-16-24-1-0

33 : 1-8-24-1-0

34 : 2-16-24-1-0

35 : 12620

36 : 24620

37 : 48620

38 : 22840

39 : 44840

40 : NA

41 : NA

42 : NA

43 : NA

44 : NA

45 : NA

46 : NA

47 : NA

48 : NA

Loading...

Loading...