JESD_SUBCHIP Register Map

www.ti.com

158

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

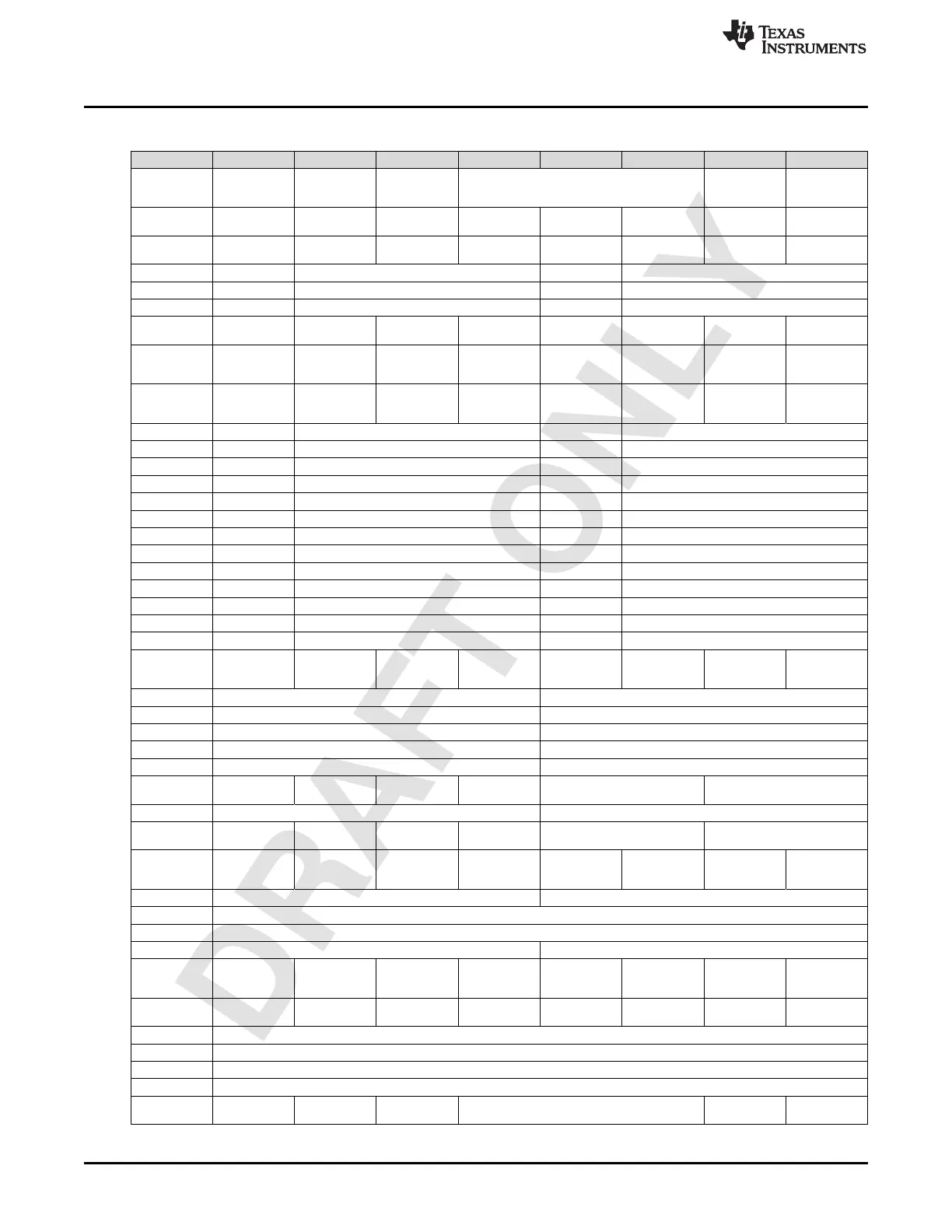

Table 2-44. JESD SubChip Register Map (continued)

ADDRESS (Hex) D7 D6 D5 D4 D3 D2 D1 D0

50h

RX_TX_LOOPB

ACK_FIFO_INIT

_STATE

RX_TX_LOOPBACK_FIFO_OFFSET

RX_TX_LOOPB

ACK_MODE_TX

1

RX_TX_LOOPB

ACK_MODE_TX

0

52h

TXB_B1_Q_DAT

A_NEGATION

TXB_B1_I_DAT

A_NEGATION

TXB_B0_Q_DAT

A_NEGATION

TXB_B0_I_DAT

A_NEGATION

TXA_B1_Q_DAT

A_NEGATION

TXA_B1_I_DAT

A_NEGATION

TXA_B0_Q_DAT

A_NEGATION

TXA_B0_I_DAT

A_NEGATION

53h

TXD_B1_Q_DAT

A_NEGATION

TXD_B1_I_DAT

A_NEGATION

TXD_B0_Q_DAT

A_NEGATION

TXD_B0_I_DAT

A_NEGATION

TXC_B1_Q_DAT

A_NEGATION

TXC_B1_I_DAT

A_NEGATION

TXC_B0_Q_DAT

A_NEGATION

TXC_B0_I_DAT

A_NEGATION

54h ADC_JESD_SYNC_N1_MUX_SEL ADC_JESD_SYNC_N0_MUX_SEL

55h ADC_JESD_SYNC_N3_MUX_SEL ADC_JESD_SYNC_N2_MUX_SEL

56h ADC_JESD_SYNC_N5_MUX_SEL ADC_JESD_SYNC_N4_MUX_SEL

57h

ADC_JESD_SY

NC_N5_INV

ADC_JESD_SY

NC_N4_INV

ADC_JESD_SY

NC_N3_INV

ADC_JESD_SY

NC_N2_INV

ADC_JESD_SY

NC_N1_INV

ADC_JESD_SY

NC_N0_INV

58h

ADC_JESD_SY

NC_N5_SPI_VA

L

ADC_JESD_SY

NC_N4_SPI_VA

L

ADC_JESD_SY

NC_N3_SPI_VA

L

ADC_JESD_SY

NC_N2_SPI_VA

L

ADC_JESD_SY

NC_N1_SPI_VA

L

ADC_JESD_SY

NC_N0_SPI_VA

L

59h

ADC_JESD_SY

NC_N5_SPI_OV

R

ADC_JESD_SY

NC_N4_SPI_OV

R

ADC_JESD_SY

NC_N3_SPI_OV

R

ADC_JESD_SY

NC_N2_SPI_OV

R

ADC_JESD_SY

NC_N1_SPI_OV

R

ADC_JESD_SY

NC_N0_SPI_OV

R

5Ch ADC_JESD_SYNC_N1_REORDER ADC_JESD_SYNC_N0_REORDER

5Dh ADC_JESD_SYNC_N3_REORDER ADC_JESD_SYNC_N2_REORDER

5Eh ADC_JESD_SYNC_N5_REORDER ADC_JESD_SYNC_N4_REORDER

60h MUX_SEL_FOR_TXB_CTRL MUX_SEL_FOR_TXA_CTRL

61h MUX_SEL_FOR_TXD_CTRL MUX_SEL_FOR_TXC_CTRL

68h RXOCTETPATH1_SEL RXOCTETPATH0_SEL

69h RXOCTETPATH3_SEL RXOCTETPATH2_SEL

6Ah RXOCTETPATH5_SEL RXOCTETPATH4_SEL

6Bh RXOCTETPATH7_SEL RXOCTETPATH6_SEL

6Ch RXOCTETPATH1_CLK_SEL RXOCTETPATH0_CLK_SEL

6Dh RXOCTETPATH3_CLK_SEL RXOCTETPATH2_CLK_SEL

6Eh RXOCTETPATH5_CLK_SEL RXOCTETPATH4_CLK_SEL

6Fh RXOCTETPATH7_CLK_SEL RXOCTETPATH6_CLK_SEL

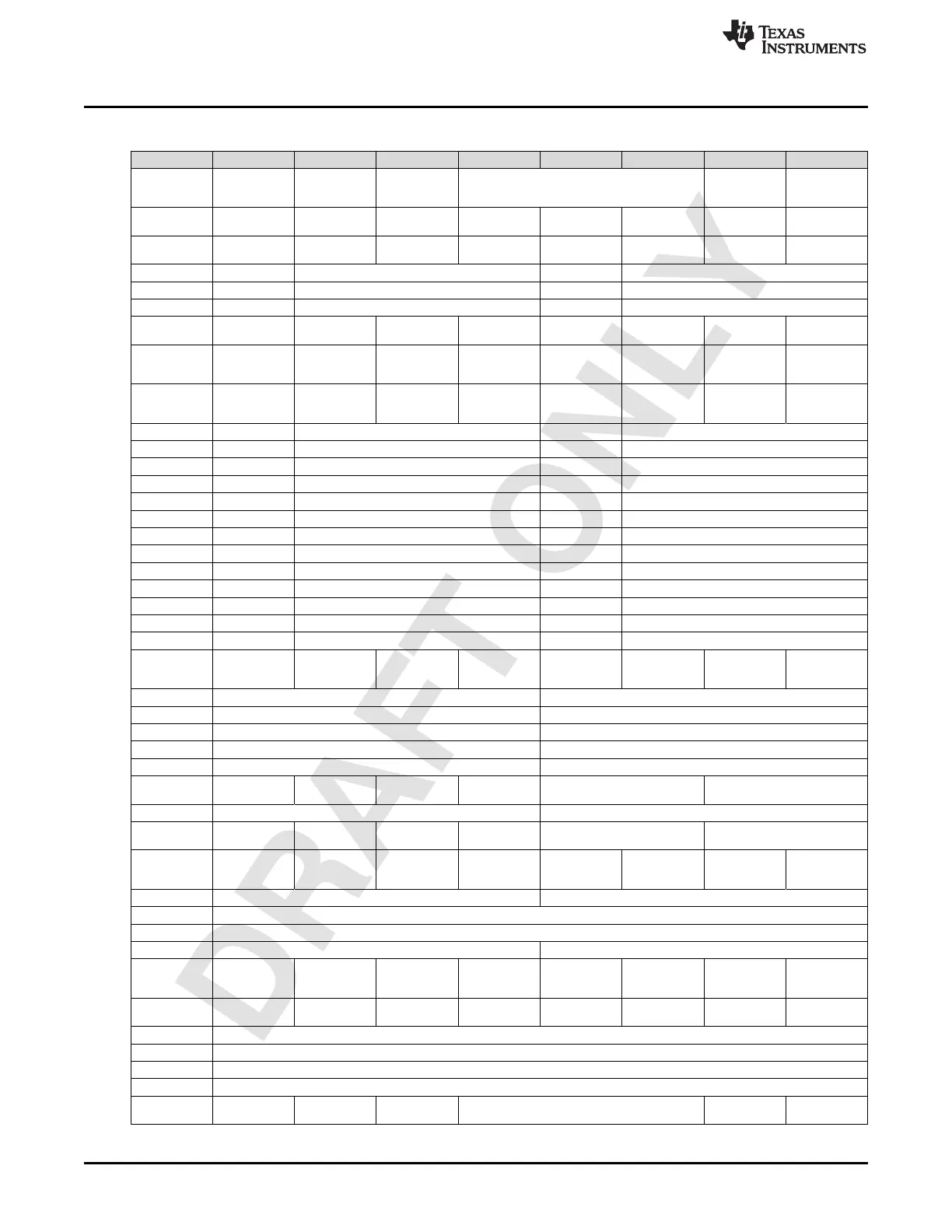

78h

ADC_DATA_GA

TING_DIS_FBC

D

ADC_DATA_GA

TING_DIS_FBA

B

ADC_DATA_GA

TING_DIS_RXD

ADC_DATA_GA

TING_DIS_RXC

ADC_DATA_GA

TING_DIS_RXB

ADC_DATA_GA

TING_DIS_RXA

79h BIT_MASKDIS_RXB BIT_MASKDIS_RXA

7Ah BIT_MASKDIS_RXD BIT_MASKDIS_RXC

7Bh BIT_MASKDIS_FBCD BIT_MASKDIS_FBAB

7Ch LP_RX_ON_B_SEL_2R1F_AB_MASK LP_RX_ON_A_SEL_2R1F_AB_MASK

7Dh LP_RX_ON_D_SEL_2R1F_AB_MASK LP_RX_ON_C_SEL_2R1F_AB_MASK

7Eh

LP_FB_ON_C_SEL_2R1F_AB_MAS

K

LP_FB_ON_A_SEL_2R1F_AB_MAS

K

81h LP_RX_ON_D_SEL_2R1F_CD_MASK LP_RX_ON_C_SEL_2R1F_CD_MASK

82h

LP_FB_ON_C_SEL_2R1F_CD_MA

SK

LP_FB_ON_A_SEL_2R1F_CD_MAS

K

90h

CFG_CNT_FRE

ERUN_EN

CFG_CLK_CYC

LE_CNT_EN

CFG_COMPARA

TOR_MODULE_

EN

91h CFG_SLOW_CLK_SEL CFG_FAST_CLK_SEL

92h LOAD_SLOW_CLK_CNT_SEED_VAL[7:0]

93h LOAD_SLOW_CLK_CNT_SEED_VAL[15:8]

94h CFG_CLK_COMP_SLOW_CNT_OBS_SEL CFG_CLK_COMP_FAST_CNT_OBS_SEL

95h

CFG_CLK_COM

PARATOR_INST

_SEL

97h

CLK_OBS_DON

E_INTR

98h FAST_CLK_CNT[7:0]

99h FAST_CLK_CNT[15:8]

9Ah SLOW_CLK_CNT[7:0]

9Bh SLOW_CLK_CNT[15:8]

9Ch

RX_CLK_LFSR_

SEED_LOAD

RX_CLK_SYSR

EF_VAL

RX_CLK_SYSR

EF_SEL

RX_CLK_SYSREF_DELAY

RX_CLK_DITHE

RED_MODE_EN

RX_CLK_DISAB

LE

Loading...

Loading...