www.ti.com

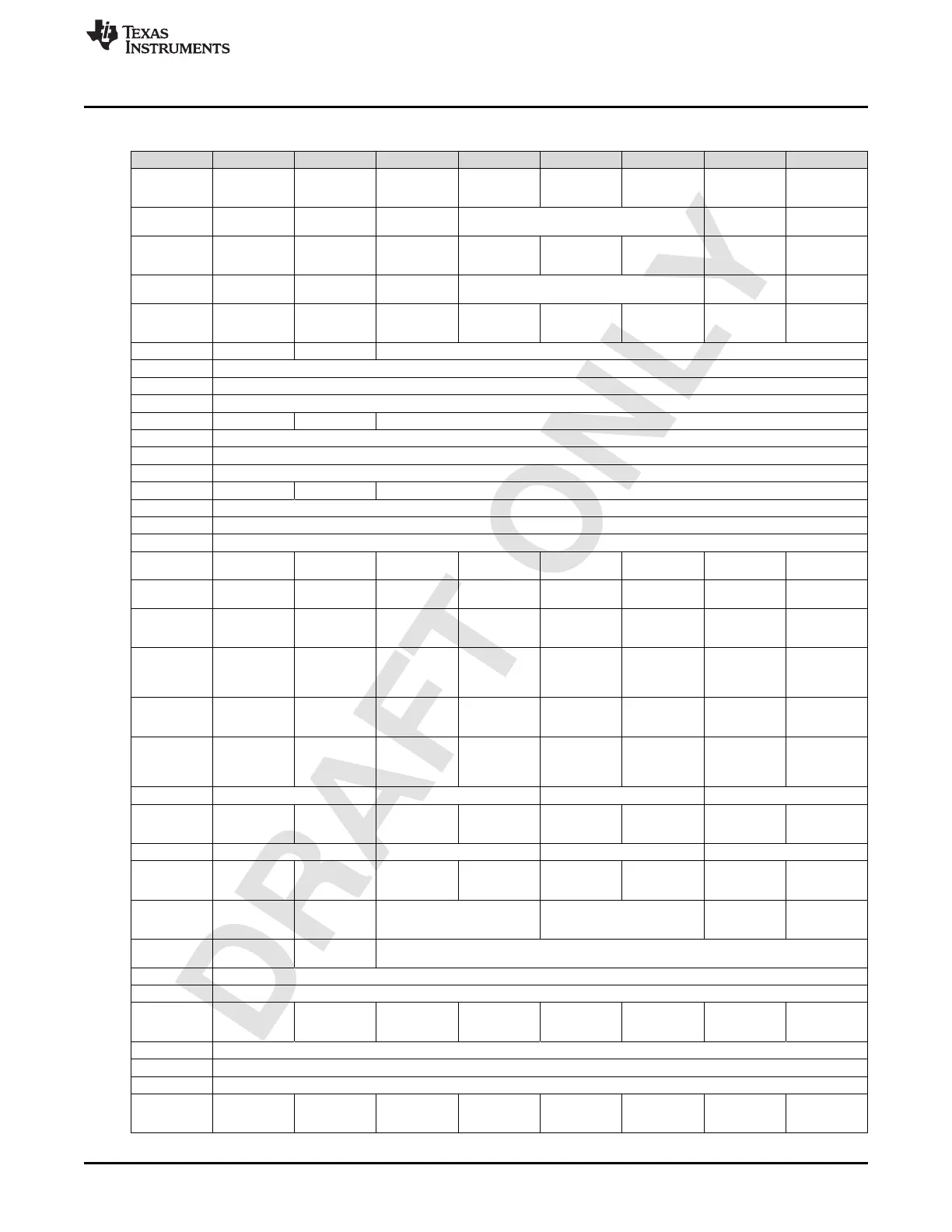

JESD_SUBCHIP Register Map

159

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-44. JESD SubChip Register Map (continued)

ADDRESS (Hex) D7 D6 D5 D4 D3 D2 D1 D0

9Dh

RX_CLK_DIV4_

COMMON_PHA

SE_DISABLE

RX_CLK_DIV4_

PHASE4_DISAB

LE

RX_CLK_DIV4_

PHASE3_DISAB

LE

RX_CLK_DIV4_

PHASE2_DISAB

LE

RX_CLK_DIV4_

PHASE1_DISAB

LE

RX_CLK_DIV4_

PHASE0_DISAB

LE

RX_CLK_DIV4_

MULTIPHASE_D

ISABLE

9Eh

FB_CLK_LFSR_

SEED_LOAD

FB_CLK_SYSRE

F_VAL

FB_CLK_SYSRE

F_SEL

FB_CLK_SYSREF_DELAY

FB_CLK_DITHE

RED_MODE_EN

FB_CLK_DISAB

LE

9Fh

TX_OR_FB_CLK

_MUX

FB_CLK_DIV4_

COMMON_PHA

SE_DISABLE

FB_CLK_DIV4_

PHASE4_DISAB

LE

FB_CLK_DIV4_

PHASE3_DISAB

LE

FB_CLK_DIV4_

PHASE2_DISAB

LE

FB_CLK_DIV4_

PHASE1_DISAB

LE

FB_CLK_DIV4_

PHASE0_DISAB

LE

FB_CLK_DIV4_

MULTIPHASE_D

ISABLE

A0h

TX_CLK_LFSR_

SEED_LOAD

TX_CLK_SYSRE

F_VAL

TX_CLK_SYSRE

F_SEL

TX_CLK_SYSREF_DELAY

TX_CLK_DITHE

RED_MODE_EN

TX_CLK_DISAB

LE

A1h

TX_CLK_DIV4_

COMMON_PHA

SE_DISABLE

TX_CLK_DIV4_

PHASE4_DISAB

LE

TX_CLK_DIV4_

PHASE3_DISAB

LE

TX_CLK_DIV4_

PHASE2_DISAB

LE

TX_CLK_DIV4_

PHASE1_DISAB

LE

TX_CLK_DIV4_

PHASE0_DISAB

LE

TX_CLK_DIV4_

MULTIPHASE_D

ISABLE

A4h RX_CLK_DIV_VAL_ACC_THRESH

A5h RX_CLK_LFSR_SEED_VAL[7:0]

A6h RX_CLK_LFSR_SEED_VAL[15:8]

A7h RX_CLK_LFSR_SEED_VAL[23:16]

A8h FB_CLK_DIV_VAL_ACC_THRESH

A9h FB_CLK_LFSR_SEED_VAL[7:0]

AAh FB_CLK_LFSR_SEED_VAL[15:8]

ABh FB_CLK_LFSR_SEED_VAL[23:16]

ACh TX_CLK_DIV_VAL_ACC_THRESH

ADh TX_CLK_LFSR_SEED_VAL[7:0]

AEh TX_CLK_LFSR_SEED_VAL[15:8]

AFh TX_CLK_LFSR_SEED_VAL[23:16]

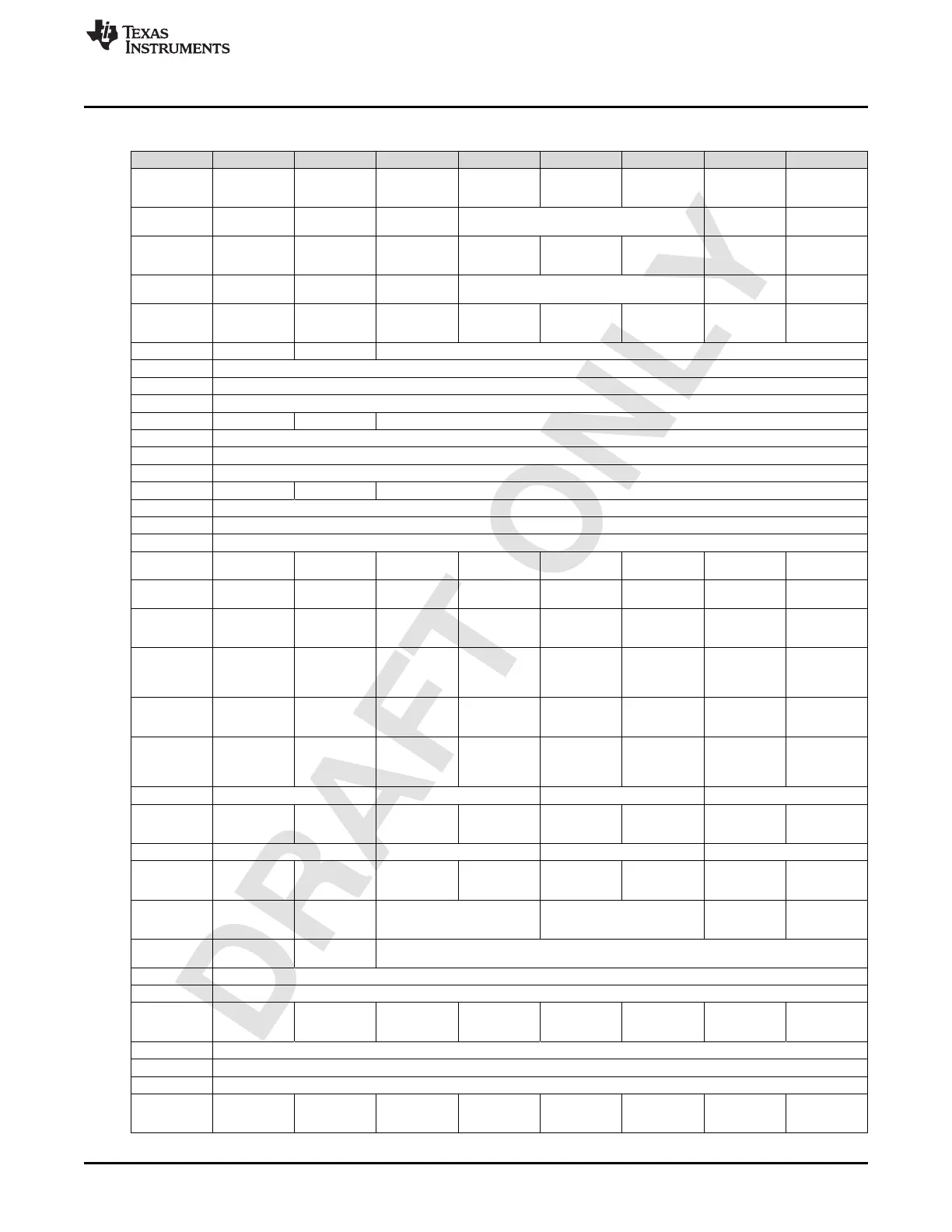

B0h

IQ_SWAP_RXD

_P23

IQ_SWAP_RXD

_P01

IQ_SWAP_RXC

_P23

IQ_SWAP_RXC

_P01

IQ_SWAP_RXB_

P23

IQ_SWAP_RXB_

P01

IQ_SWAP_RXA_

P23

IQ_SWAP_RXA_

P01

B1h

IQ_SWAP_FBC

D_P23

IQ_SWAP_FBC

D_P01

IQ_SWAP_FBAB

_P23

IQ_SWAP_FBAB

_P01

B4h

TDD_FB_ON_C

_2R1F_AB_MAS

K

TDD_FB_ON_A_

2R1F_AB_MASK

TDD_RX_ON_D

_2R1F_AB_MAS

K

TDD_RX_ON_C

_2R1F_AB_MAS

K

TDD_RX_ON_B

_2R1F_AB_MAS

K

TDD_RX_ON_A

_2R1F_AB_MAS

K

B5h

TDD_FB_DYN_

SWITCH_PRIOR

ITYSWAP_2R1F

_AB

TDD_RX_PRIOR

ITY_DIS_2R1F_

AB

B6h

TDD_FB_ON_C

_2R1F_CD_MAS

K

TDD_FB_ON_A_

2R1F_CD_MAS

K

TDD_RX_ON_D

_2R1F_CD_MAS

K

TDD_RX_ON_C

_2R1F_CD_MAS

K

TDD_RX_ON_B

_2R1F_CD_MAS

K

TDD_RX_ON_A

_2R1F_CD_MAS

K

B7h

TDD_FB_DYN_

SWITCH_PRIOR

ITYSWAP_2R1F

_CD

TDD_RX_PRIOR

ITY_DIS_2R1F_

CD

BCh TDD_TX_ON_D_2T_AB_MUX_SEL TDD_TX_ON_C_2T_AB_MUX_SEL TDD_TX_ON_B_2T_AB_MUX_SEL TDD_TX_ON_A_2T_AB_MUX_SEL

BDh

TDD_TX_ON_D

_2T_AB_LINK1_

MASK

TDD_TX_ON_C

_2T_AB_LINK1_

MASK

TDD_TX_ON_B_

2T_AB_LINK1_

MASK

TDD_TX_ON_A_

2T_AB_LINK1_

MASK

TDD_TX_ON_D

_2T_AB_LINK0_

MASK

TDD_TX_ON_C

_2T_AB_LINK0_

MASK

TDD_TX_ON_B_

2T_AB_LINK0_

MASK

TDD_TX_ON_A_

2T_AB_LINK0_

MASK

BEh TDD_TX_ON_D_2T_CD_MUX_SEL TDD_TX_ON_C_2T_CD_MUX_SEL TDD_TX_ON_B_2T_CD_MUX_SEL TDD_TX_ON_A_2T_CD_MUX_SEL

BFh

TDD_TX_ON_D

_2T_CD_LINK1_

MASK

TDD_TX_ON_C

_2T_CD_LINK1_

MASK

TDD_TX_ON_B_

2T_CD_LINK1_

MASK

TDD_TX_ON_A_

2T_CD_LINK1_

MASK

TDD_TX_ON_D

_2T_CD_LINK0_

MASK

TDD_TX_ON_C

_2T_CD_LINK0_

MASK

TDD_TX_ON_B_

2T_CD_LINK0_

MASK

TDD_TX_ON_A_

2T_CD_LINK0_

MASK

C0h

APB_CLK_SYS

REF_VAL

APB_CLK_SYS

REF_SEL

APB_CLK_SYSREF_DELAY2 APB_CLK_SYSREF_DELAY

APB_CLK_DITH

ERED_MODE_E

N

APB_CLK_DISA

BLE

C1h

APB_CLK_DIV_

FACTOR_LOAD

APB_CLK_DIV_

FACTOR_ODD

APB_CLK_DIV_FACTOR

C2h APB_CLK_PARALLEL_LOAD_VAL[7:0]

C3h APB_CLK_PARALLEL_LOAD_VAL[15:8]

C4h

APB_CLK_LFSR

_LOAD

APB_CLK_LFSR

_CODE_OVR_V

AL

APB_CLK_FRO

M_MCU_CLK_E

N

C5h APB_CLK_LFSR_SEED_VAL[7:0]

C6h APB_CLK_LFSR_SEED_VAL[15:8]

C7h APB_CLK_LFSR_SEED_VAL[23:16]

C8h

DAC_JESD_SY

NC_N3_SPI_OV

R

DAC_JESD_SY

NC_N3_SPI_VA

L

DAC_JESD_SY

NC_N2_SPI_OV

R

DAC_JESD_SY

NC_N2_SPI_VA

L

DAC_JESD_SY

NC_N1_SPI_OV

R

DAC_JESD_SY

NC_N1_SPI_VA

L

DAC_JESD_SY

NC_N0_SPI_OV

R

DAC_JESD_SY

NC_N0_SPI_VA

L

Loading...

Loading...