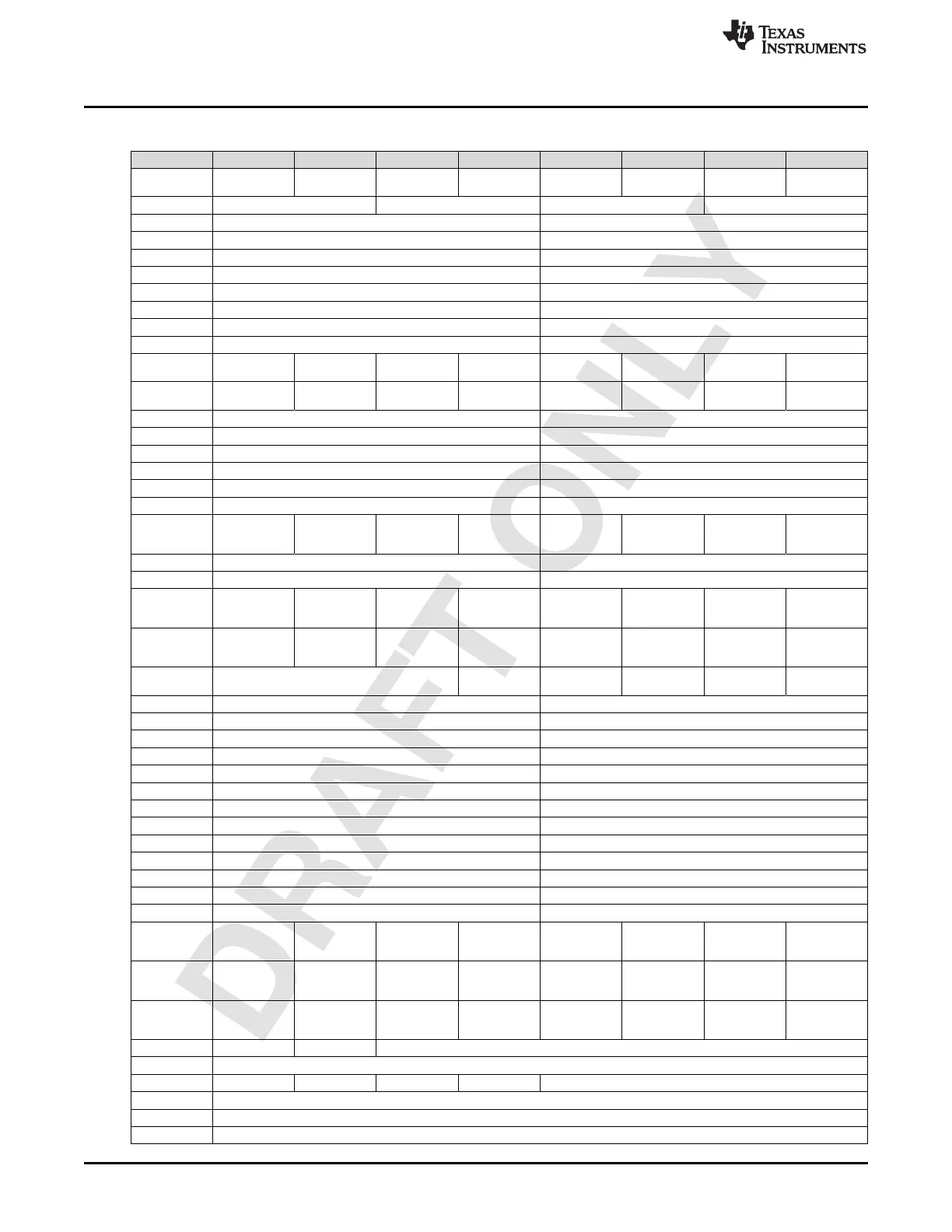

JESD_SUBCHIP Register Map

www.ti.com

160

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-44. JESD SubChip Register Map (continued)

ADDRESS (Hex) D7 D6 D5 D4 D3 D2 D1 D0

C9h

DAC_JESD_SY

NC_N3_INV

DAC_JESD_SY

NC_N2_INV

DAC_JESD_SY

NC_N1_INV

DAC_JESD_SY

NC_N0_INV

CAh DAC_JESD_SYNC_N3_MUX_SEL DAC_JESD_SYNC_N2_MUX_SEL DAC_JESD_SYNC_N1_MUX_SEL DAC_JESD_SYNC_N0_MUX_SEL

CCh MUX_SEL_FOR_TXA_B0_Q MUX_SEL_FOR_TXA_B0_I

CDh MUX_SEL_FOR_TXA_B1_Q MUX_SEL_FOR_TXA_B1_I

CEh MUX_SEL_FOR_TXB_B0_Q MUX_SEL_FOR_TXB_B0_I

CFh MUX_SEL_FOR_TXB_B1_Q MUX_SEL_FOR_TXB_B1_I

D0h MUX_SEL_FOR_TXC_B0_Q MUX_SEL_FOR_TXC_B0_I

D1h MUX_SEL_FOR_TXC_B1_Q MUX_SEL_FOR_TXC_B1_I

D2h MUX_SEL_FOR_TXD_B0_Q MUX_SEL_FOR_TXD_B0_I

D3h MUX_SEL_FOR_TXD_B1_Q MUX_SEL_FOR_TXD_B1_I

D4h

IQ_SWAP_TXD_

B1

IQ_SWAP_TXD_

B0

IQ_SWAP_TXC_

B1

IQ_SWAP_TXC_

B0

IQ_SWAP_TXB_

B1

IQ_SWAP_TXB_

B0

IQ_SWAP_TXA_

B1

IQ_SWAP_TXA_

B0

155h

TXD_DAC_CLK_

EN_OVR

TXC_DAC_CLK_

EN_OVR

TXB_DAC_CLK_

EN_OVR

TXA_DAC_CLK_

EN_OVR

156h TXB_DAC_CLK_EN_VAL TXA_DAC_CLK_EN_VAL

157h TXD_DAC_CLK_EN_VAL TXC_DAC_CLK_EN_VAL

158h SERDESAB_LOS_INDICATOR_MASK SERDESAB_LOS_INDICATOR_CLEAR

159h SERDESAB_PHY_READY_MASK SERDESAB_PHY_READY_CLEAR

15Ah SERDESCD_LOS_INDICATOR_MASK SERDESCD_LOS_INDICATOR_CLEAR

15Bh SERDESCD_PHY_READY_MASK SERDESCD_PHY_READY_CLEAR

15Ch

SERDESCD_PL

L_LOSS_OF_LO

CK_MASK

SERDESCD_PL

L_LOSS_OF_LO

CK_CLEAR

SERDESAB_PL

L_LOSS_OF_LO

CK_MASK

SERDESAB_PL

L_LOSS_OF_LO

CK_CLEAR

15Dh SERDESAB_PHY_READY SERDESAB_LOS_INDICATOR

15Eh SERDESCD_PHY_READY SERDESCD_LOS_INDICATOR

15Fh

SERDESCD_PL

L_LOSS_OF_LO

CK

SERDESAB_PL

L_LOSS_OF_LO

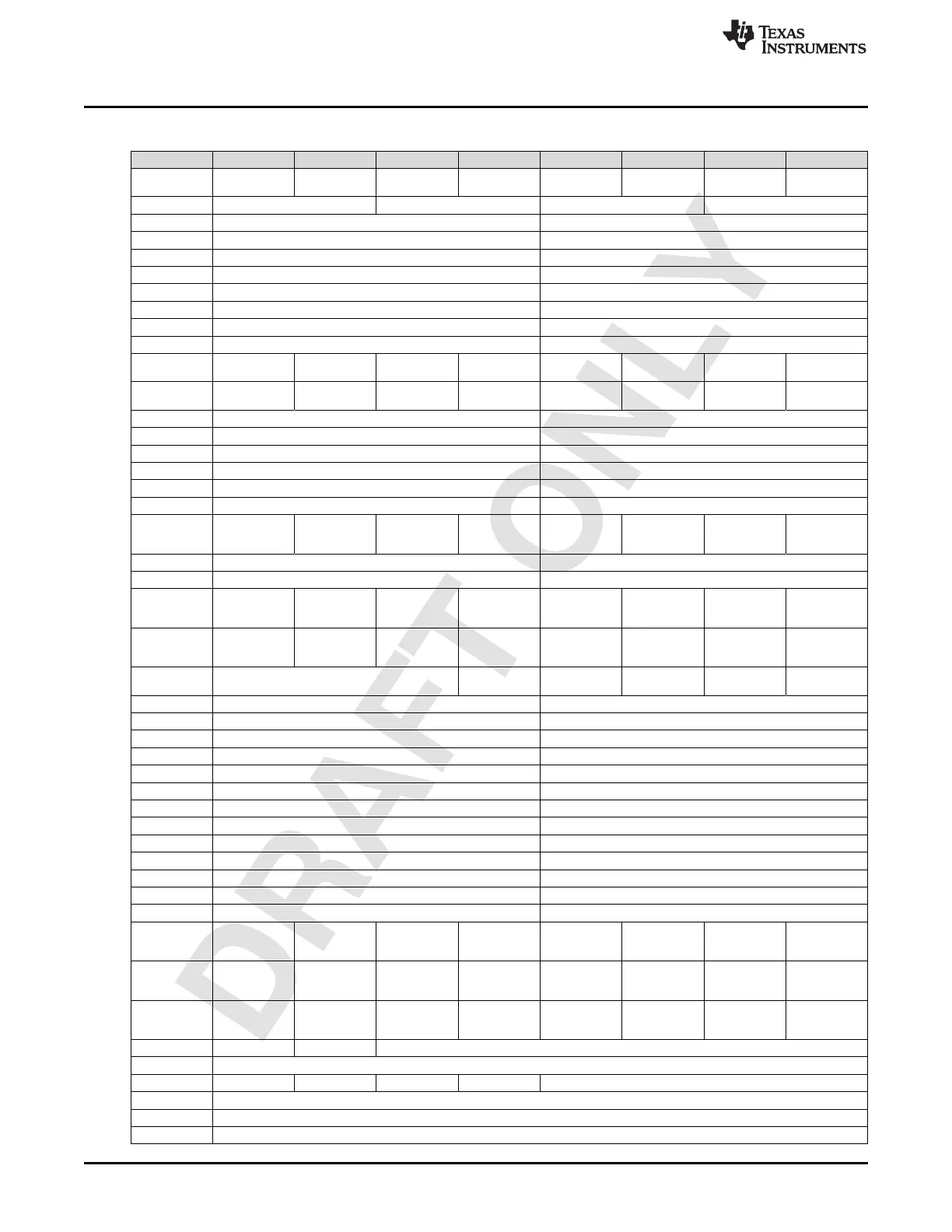

CK

160h

DBG_DDC_AFIF

O_DBG_LOGIC_

EN

DBG_FBCD_AFI

FO_DBG_CFG_

CLR

DBG_FBAB_AFI

FO_DBG_CFG_

CLR

DBG_RXD_AFIF

O_DBG_CFG_C

LR

DBG_RXC_AFIF

O_DBG_CFG_C

LR

DBG_RXB_AFIF

O_DBG_CFG_C

LR

DBG_RXA_AFIF

O_DBG_CFG_C

LR

161h

DBG_FIFO_SEL

DBG_CFG_FIFO

_PTR_SAMPLE

162h DBG_FIFO_SAMPLED_WR_PTR DBG_FIFO_SAMPLED_RD_PTR

164h DBG_RXB_ASYNC_FIFO_ALARM_CLR DBG_RXA_ASYNC_FIFO_ALARM_CLR

165h DBG_RXD_ASYNC_FIFO_ALARM_CLR DBG_RXC_ASYNC_FIFO_ALARM_CLR

166h DBG_FBCD_ASYNC_FIFO_ALARM_CLR DBG_FBAB_ASYNC_FIFO_ALARM_CLR

168h DBG_RXB_ASYNC_FIFO_ALARM_MASK DBG_RXA_ASYNC_FIFO_ALARM_MASK

169h DBG_RXD_ASYNC_FIFO_ALARM_MASK DBG_RXC_ASYNC_FIFO_ALARM_MASK

16Ah DBG_FBCD_ASYNC_FIFO_ALARM_MASK DBG_FBAB_ASYNC_FIFO_ALARM_MASK

16Ch DBG_RXB_ASYNC_FIFO_ALARM DBG_RXA_ASYNC_FIFO_ALARM

16Dh DBG_RXD_ASYNC_FIFO_ALARM DBG_RXC_ASYNC_FIFO_ALARM

16Eh DBG_FBCD_ASYNC_FIFO_ALARM DBG_FBAB_ASYNC_FIFO_ALARM

170h DBG_RXB_AFIFO_SYSREF_SPACING DBG_RXA_AFIFO_SYSREF_SPACING

171h DBG_RXD_AFIFO_SYSREF_SPACING DBG_RXC_AFIFO_SYSREF_SPACING

172h DBG_FBCD_AFIFO_SYSREF_SPACING DBG_FBAB_AFIFO_SYSREF_SPACING

174h

DBG_RXB_AFIF

O_RD_CLK_TO

GGLE_STICKY

DBG_RXB_AFIF

O_WR_CLK_TO

GGLE_STICKY

DBG_RXB_AFIF

O_SYS_REF_R

D_STICKY

DBG_RXB_AFIF

O_SYS_REF_W

R_STICKY

DBG_RXA_AFIF

O_RD_CLK_TO

GGLE_STICKY

DBG_RXA_AFIF

O_WR_CLK_TO

GGLE_STICKY

DBG_RXA_AFIF

O_SYS_REF_R

D_STICKY

DBG_RXA_AFIF

O_SYS_REF_W

R_STICKY

175h

DBG_RXD_AFIF

O_RD_CLK_TO

GGLE_STICKY

DBG_RXD_AFIF

O_WR_CLK_TO

GGLE_STICKY

DBG_RXD_AFIF

O_SYS_REF_R

D_STICKY

DBG_RXD_AFIF

O_SYS_REF_W

R_STICKY

DBG_RXC_AFIF

O_RD_CLK_TO

GGLE_STICKY

DBG_RXC_AFIF

O_WR_CLK_TO

GGLE_STICKY

DBG_RXC_AFIF

O_SYS_REF_R

D_STICKY

DBG_RXC_AFIF

O_SYS_REF_W

R_STICKY

176h

DBG_FBCD_AFI

FO_RD_CLK_T

OGGLE_STICKY

DBG_FBCD_AFI

FO_WR_CLK_T

OGGLE_STICKY

DBG_FBCD_AFI

FO_SYS_REF_

RD_STICKY

DBG_FBCD_AFI

FO_SYS_REF_

WR_STICKY

DBG_FBAB_AFI

FO_RD_CLK_T

OGGLE_STICKY

DBG_FBAB_AFI

FO_WR_CLK_T

OGGLE_STICKY

DBG_FBAB_AFI

FO_SYS_REF_

RD_STICKY

DBG_FBAB_AFI

FO_SYS_REF_

WR_STICKY

180h ADC_SYNC_N_FROM_PIN

181h ADC_SYNC_N_POST_MUX

182h DAC_SYNC_N_TO_PIN

183h DAC_SYNC_N_PRE_MUX

188h DBG_RX_READ_OUT_REG1[7:0]

189h DBG_RX_READ_OUT_REG1[15:8]

Loading...

Loading...