www.ti.com

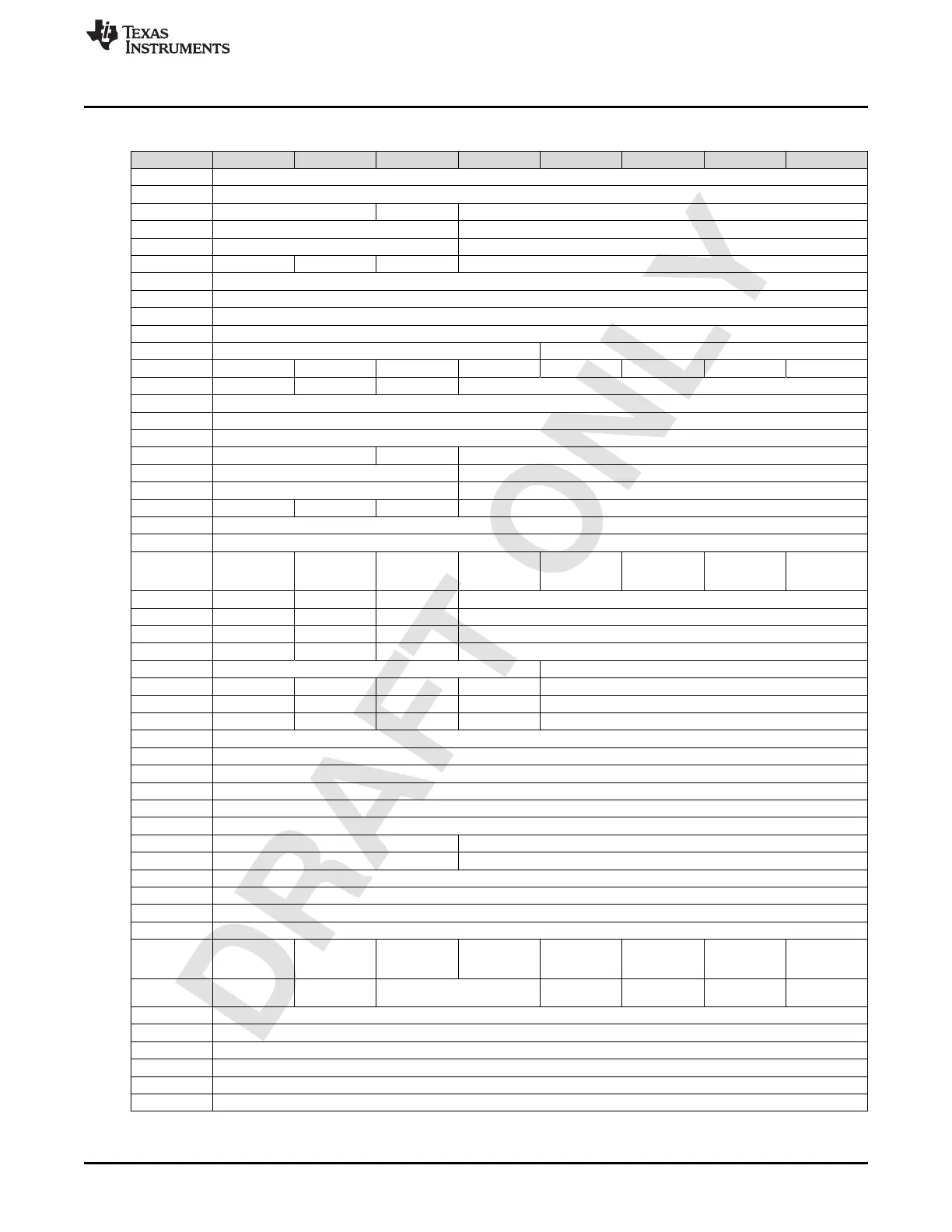

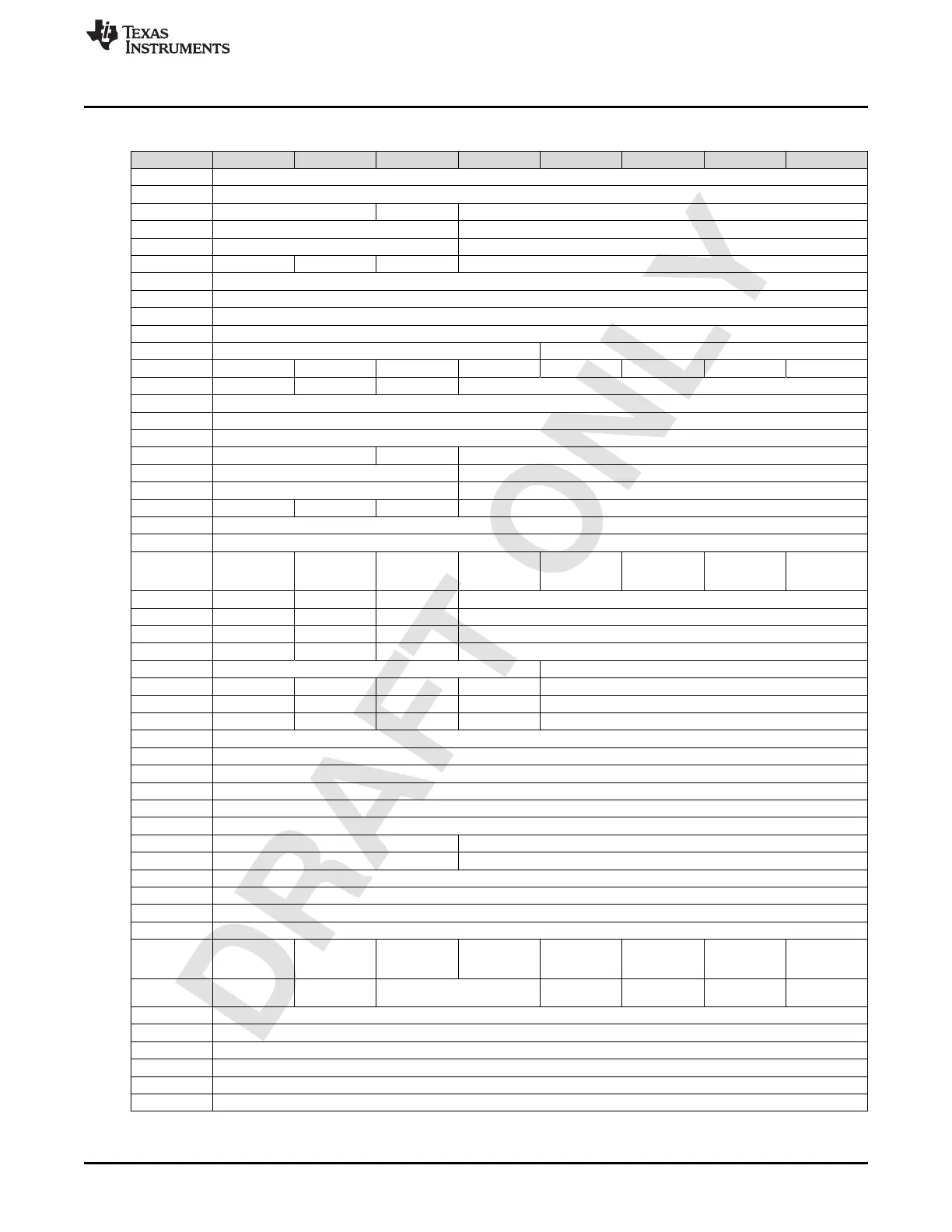

DAC JESD Register Map

257

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-233. DAC JESD Register Map (continued)

ADDRESS (Hex) D7 D6 D5 D4 D3 D2 D1 D0

49h LINK0_ILA_K_M1

4Ah LINK0_ILA_M_M1

4Bh LINK0_CS LINK0_ILA_N_M1

4Ch LINK0_SUBCLASSV LINK0_ILA_NPRIME_M1

4Dh LINK0_JESDV LINK0_ILA_S_M1

4Eh LINK0_ILA_HD LINK0_CF

4Fh LINK0_RES1

50h LINK0_RES2

51h COMMA_ALIGN_DLY_THRESH

52h LINK1_DID

53h LINK1_BID LINK1_ADJCNT

54h LINK1_ADJDIR LINK1_PHADJ

55h LINK1_SCR LINK1_ILA_L_M1

56h LINK1_ILA_F_M1

57h LINK1_ILA_K_M1

58h LINK1_ILA_M_M1

59h LINK1_CS LINK1_ILA_N_M1

5Ah LINK1_SUBCLASSV LINK1_ILA_NPRIME_M1

5Bh LINK1_JESDV LINK1_ILA_S_M1

5Ch LINK1_ILA_HD LINK1_CF

5Dh LINK1_RES1

5Eh LINK1_RES2

5Fh

LINK1_ILA_CON

FIG_OVERRIDE

LINK1_CTRL_C

ONFIG_OVERRI

DE

LINK0_ILA_CON

FIG_OVERRIDE

60h LID0

61h LID1

62h LID2

63h LID3

64h JESD_CLEAR_DATA LANE_ENA

65h K_COUNTER_THRESH

66h V_COUNTER_THRESH

67h I_COUNTER_THRESH

68h LINK0_RBD_M1[7:0]

69h LINK0_RBD_M1[15:8]

6Ah LINK1_RBD_M1[7:0]

6Bh LINK1_RBD_M1[15:8]

6Ch LINK0_K_M1

6Dh LINK1_K_M1

6Eh LINK0_BUFFER_READ_PTR_OFFSET LINK0_BUFFER_DEPTH

6Fh LINK1_BUFFER_READ_PTR_OFFSET LINK1_BUFFER_DEPTH

70h LINK0_INIT_O_COUNTER

71h LINK0_INIT_F_COUNTER

72h LINK1_INIT_O_COUNTER

73h LINK1_INIT_F_COUNTER

74h

LINK1_AUTOLO

AD_JESD_ERR

CNT

LINK0_AUTOLO

AD_JESD_ERR

CNT

LINK1_SYNC_E

RROR_CNT_CL

R

LINK0_SYNC_E

RROR_CNT_CL

R

75h

MATCH_CTRL

MATCH_SPECIF

IC

JESD_TEST_SEQ

DISABLE_ERR_

REPORT

MP_LINK_ENA

NO_LANE_SYN

C

MIN_LATENCY_

ENA

76h MATCH_DATA

77h SYNC_REQUEST_PULSE_EXPANSION_COUNT

78h LINK0_SYNC_REQUEST_ENA

79h LINK1_SYNC_REQUEST_ENA

7Ah LINK0_ERROR_ENA

7Bh LINK1_ERROR_ENA

Loading...

Loading...