DAC JESD Register Map

www.ti.com

258

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

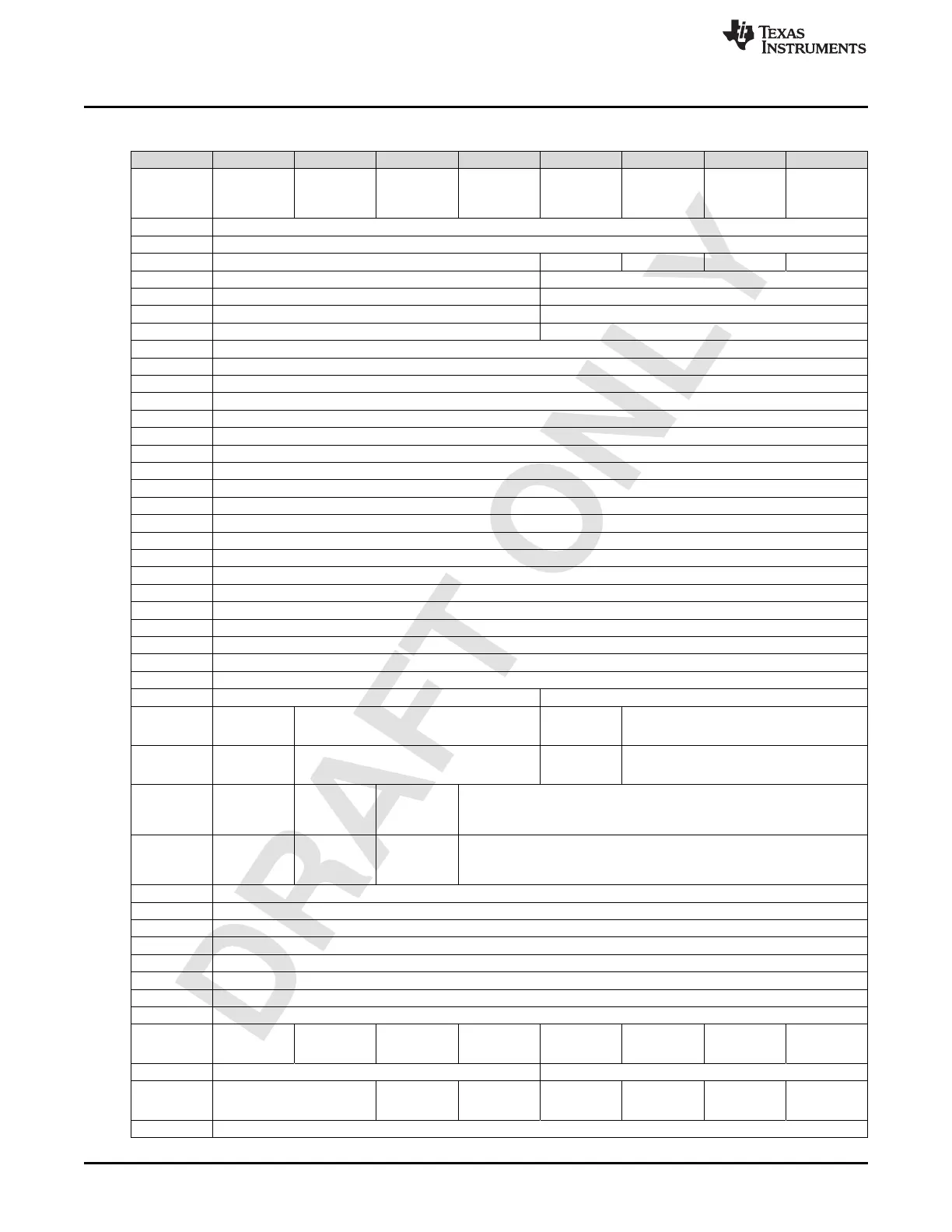

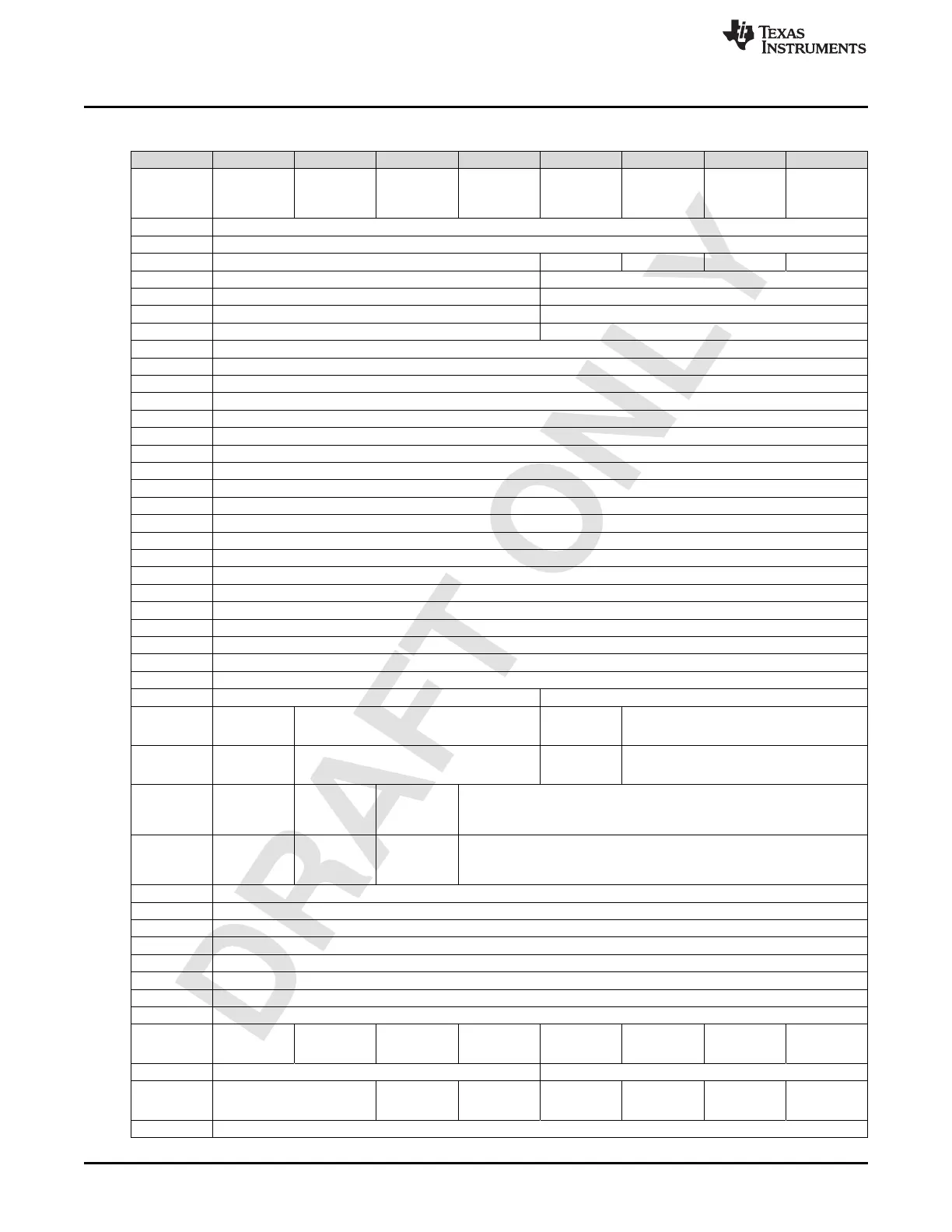

Table 2-233. DAC JESD Register Map (continued)

ADDRESS (Hex) D7 D6 D5 D4 D3 D2 D1 D0

7Ch

LINK1_FRAME_

SYNC_ERR_CN

T_CLR

LINK0_FRAME_

SYNC_ERR_CN

T_CLR

LINK1_FRAME_

SYNC_ERR_EN

A

LINK0_FRAME_

SYNC_ERR_EN

A

LINK1_FRAME_

SYNC_ERR_SY

NC_REQUEST_

ENA

LINK0_FRAME_

SYNC_ERR_SY

NC_REQUEST_

ENA

7Dh LINK0_LANE_ERROR_CNT_CLR

7Eh LINK1_LANE_ERROR_CNT_CLR

7Fh FRAME_SYNC_ERR_CNT_THRESH

80h FRAME_ALIGN_ERR_CNT_THRESH MULTIFRAME_ALIGN_ERR_CNT_THRESH

81h RBD_BUF_OVERFLOW_ERR_CNT_THRESH LINK_CONFIG_ERR_CNT_THRESH

82h CODE_SYNC_ERR_CNT_THRESH RBD_BUF_MISMATCH_ERR_CNT_THRESH

83h DEC_8B10B_DISP_ERR_CNT_THRESH DEC_8B10B_CODE_ERR_CNT_THRESH

84h LANE0_SYNC_ERR_CNT

85h LANE1_SYNC_ERR_CNT

86h LANE2_SYNC_ERR_CNT

87h LANE3_SYNC_ERR_CNT

88h LANE0_F_COUNTER_ANY_LANE_READY[7:0]

89h LANE0_F_COUNTER_ANY_LANE_READY[15:8]

8Ah LANE1_F_COUNTER_ANY_LANE_READY[7:0]

8Bh LANE1_F_COUNTER_ANY_LANE_READY[15:8]

8Ch LANE2_F_COUNTER_ANY_LANE_READY[7:0]

8Dh LANE2_F_COUNTER_ANY_LANE_READY[15:8]

8Eh LANE3_F_COUNTER_ANY_LANE_READY[7:0]

8Fh LANE3_F_COUNTER_ANY_LANE_READY[15:8]

90h LANE0_F_COUNTER_ALL_LANES_READY[7:0]

91h LANE0_F_COUNTER_ALL_LANES_READY[15:8]

92h LANE1_F_COUNTER_ALL_LANES_READY[7:0]

93h LANE1_F_COUNTER_ALL_LANES_READY[15:8]

94h LANE2_F_COUNTER_ALL_LANES_READY[7:0]

95h LANE2_F_COUNTER_ALL_LANES_READY[15:8]

96h LANE3_F_COUNTER_ALL_LANES_READY[7:0]

97h LANE3_F_COUNTER_ALL_LANES_READY[15:8]

98h LINK1_SYSREF_CNT_ON_RELEASE_OPPORTUNITY LINK0_SYSREF_CNT_ON_RELEASE_OPPORTUNITY

99h

LINK0_MAPPER

_CNT_MAX_OV

R

LINK0_MAPPER_CNT_MAX_VAL

LINK0_MAPPER

_SYSREF_CNT_

OVR

LINK0_MAPPER_SYSREF_CNT_VAL

9Ah

LINK1_MAPPER

_CNT_MAX_OV

R

LINK1_MAPPER_CNT_MAX_VAL

LINK1_MAPPER

_SYSREF_CNT_

OVR

LINK1_MAPPER_SYSREF_CNT_VAL

9Ch

LINK0_RELEAS

E_OPPORTUNI

TY_PIPE_DLY_

OVR

LINK0_MAPPER

_RESET

LINK0_RELEASE_OPPORTUNITY_PIPE_DLY_VAL

9Dh

LINK1_RELEAS

E_OPPORTUNI

TY_PIPE_DLY_

OVR

LINK1_MAPPER

_RESET

LINK1_RELEASE_OPPORTUNITY_PIPE_DLY_VAL

A0h JESD_SH_STATE

A1h JESD_SH_STATE_PREV

A2h JESD_CS_STATE

A3h JESD_CS_STATE_PREV

A4h JESD_FS_STATE

A5h JESD_FS_STATE_PREV

A6h JESD_BUF_STATE

A7h JESD_BUF_STATE_PREV

ACh

EMB_ALIGN_PA

TT_SEL

LINK1_EMB_ALI

GN_LOCK_RES

ET_DISABLE

LINK0_EMB_ALI

GN_LOCK_RES

ET_DISABLE

LINK1_EMB_ALI

GN_RESET

LINK0_EMB_ALI

GN_RESET

ADh EMB_ALIGN_INVALID_THRESH EMB_ALIGN_VALID_THRESH

AEh

JESDC_ENCODING_MODE

JESDC_CRC_M

ODE

JESDC_80B_M

ODE_EN

DATA_BITS_RE

ORDER_AFTER

_CRC

DATA_BYTES_

REORDER_AFT

ER_CRC

DATA_BITS_RE

ORDER_BEFOR

E_CRC

DATA_BYTES_

REORDER_BEF

ORE_CRC

B0h JESDC_CMD_DATA[7:0]

Loading...

Loading...