www.ti.com

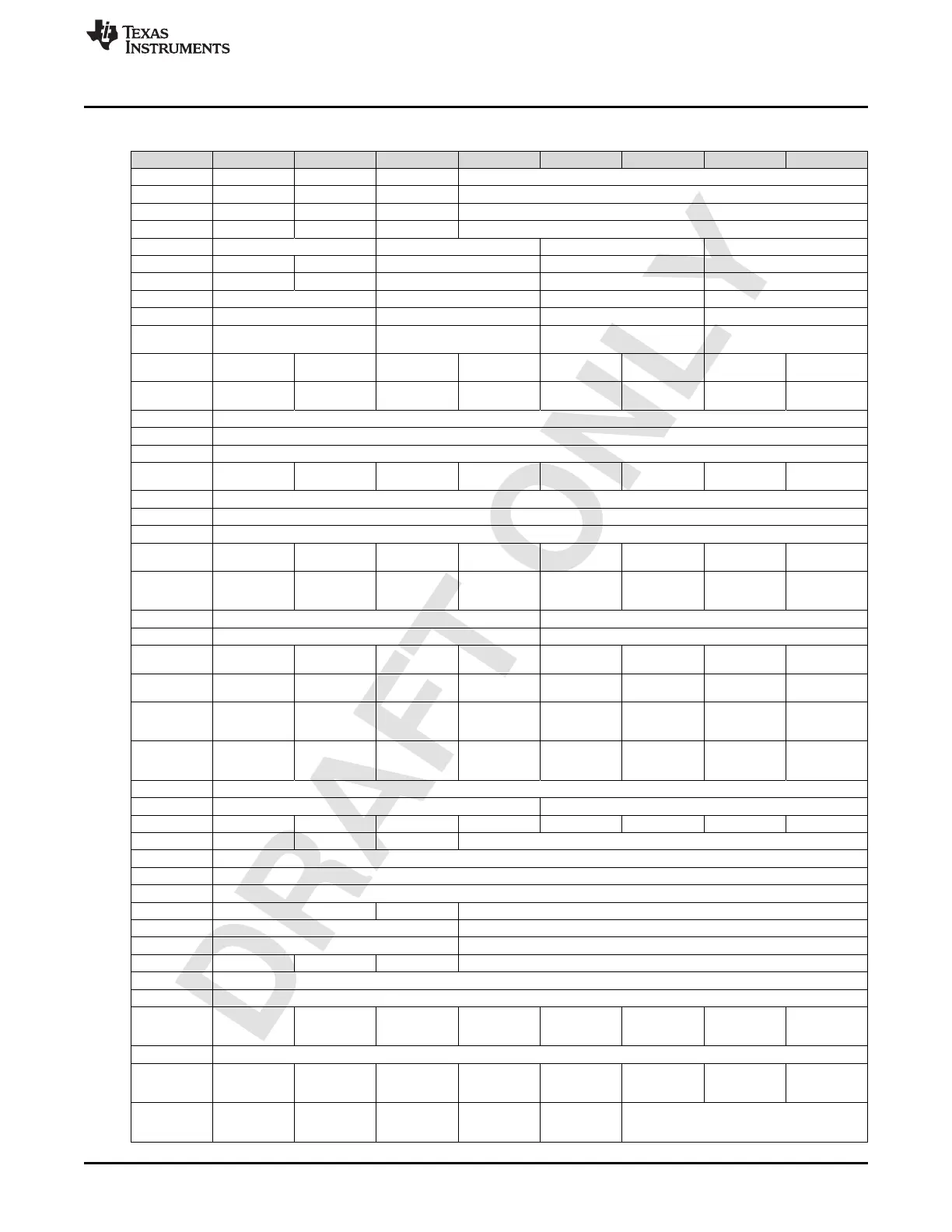

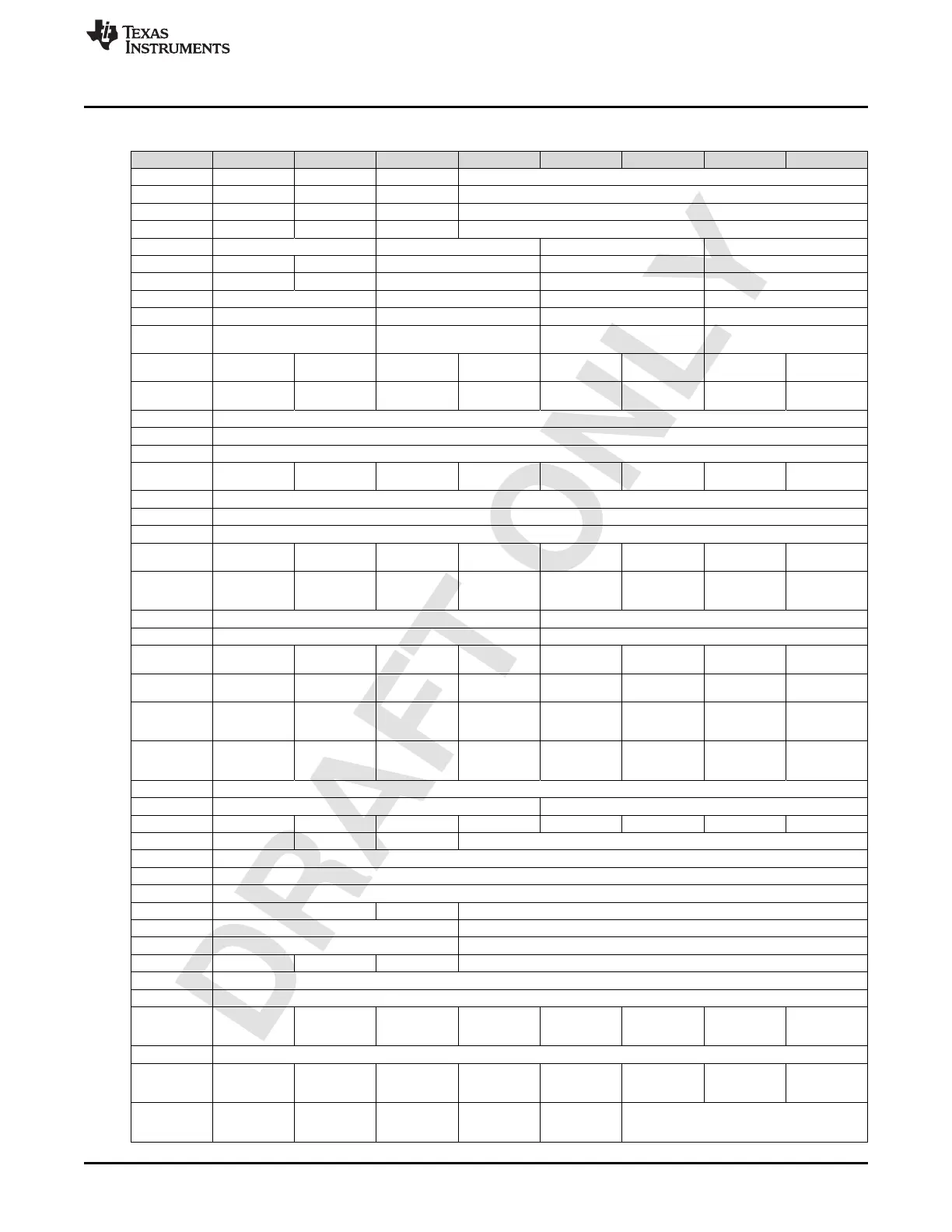

ADC JESD Register Map

371

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-501. adc_jesd Register Map (continued)

ADDRESS (Hex) D7 D6 D5 D4 D3 D2 D1 D0

4Eh 0 0 0 JESD_CLK_RX2_DIV_M

4Fh 0 0 0 JESD_CLK_RX2_DIV_N_M1

50h 0 0 0 JESD_CLK_FB_DIV_M

51h 0 0 0 JESD_CLK_FB_DIV_N_M1

54h CTRL_RX2_ROOT_CLK_P2 CTRL_RX2_ROOT_CLK_P0 CTRL_RX1_ROOT_CLK_P2 CTRL_RX1_ROOT_CLK_P0

55h 0 0 CTRL_FB_ROOT_CLK_P3 CTRL_FB_ROOT_CLK_P1 CTRL_FB_ROOT_CLK_P0

56h 0 0 CTRL_DDC_RD_CLK_FB CTRL_DDC_RD_CLK_RX2 CTRL_DDC_RD_CLK_RX1

58h CTRL_JESD_CLK_RX2_P2 CTRL_JESD_CLK_RX2_P0 CTRL_JESD_CLK_RX1_P2 CTRL_JESD_CLK_RX1_P0

59h CTRL_JESD_CLK_DIV2_RX1_P0 CTRL_JESD_CLK_FB_P3 CTRL_JESD_CLK_FB_P1 CTRL_JESD_CLK_FB_P0

5Ah

CTRL_JESD_CLK_RX1_P0_MSF_R

D

CTRL_JESD_CLK_DIV2_FB_P3 CTRL_JESD_CLK_DIV2_FB_P1 CTRL_JESD_CLK_DIV2_RX2_P2

5Ch 0 0 0

JESD_CLK_DIV

2_DITHER_EN

JESD_CLK_DIT

HER_EN

DDC_RD_CLK_

DITHER_EN

FB_ROOT_CLK

_DITHER_EN

RX_ROOT_CLK

_DITHER_EN

5Dh 0 0 0 0 0 0

FB_ADC_CLK_S

YSREF_MUX

RX_ADC_CLK_

SYSREF_MUX

60h CFG_RX_LFSR_SEED_VAL[7:0]

61h CFG_RX_LFSR_SEED_VAL[15:8]

62h CFG_RX_LFSR_SEED_VAL[23:16]

63h 0 0 0 0 0 0 0

CFG_RX_LFSR_

LOAD

64h CFG_FB_LFSR_SEED_VAL[7:0]

65h CFG_FB_LFSR_SEED_VAL[15:8]

66h CFG_FB_LFSR_SEED_VAL[23:16]

67h 0 0 0 0 0 0 0

CFG_FB_LFSR_

LOAD

68h 0 0 0 0 0 0 0

SERDES_INPUT

_ORDER_FLIP_

DISABLE

69h SERDES_FIFO_READ_DLY_LANE1 SERDES_FIFO_READ_DLY_LANE0

6Ah SERDES_FIFO_READ_DLY_LANE3 SERDES_FIFO_READ_DLY_LANE2

6Ch 0 0 0 0

LANE3_GEARB

OX_INIT_STATE

LANE2_GEARB

OX_INIT_STATE

LANE1_GEARB

OX_INIT_STATE

LANE0_GEARB

OX_INIT_STATE

6Dh 0 0 0 0 0

LINK2_INIT_STA

TE

LINK1_INIT_STA

TE

LINK0_INIT_STA

TE

6Eh 0 0 0 0

LANE3_SERDE

S_FIFO_INIT_S

TATE

LANE2_SERDE

S_FIFO_INIT_S

TATE

LANE1_SERDE

S_FIFO_INIT_S

TATE

LANE0_SERDE

S_FIFO_INIT_S

TATE

6Fh 0 0 0 0 0

INIT_STATE_SE

RDESFIFO_SPI

_OVR

INIT_STATE_GE

ARBOX_SPI_OV

R 0

74h LINK0_DID

75h LINK0_ADJCNT LINK0_BID

76h 0 LINK0_ADJDIR LINK0_PHADJ 0 0 0 0 0

77h LINK0_SCR 0 0 LINK0_ILA_L_M1

78h LINK0_ILA_F_M1

79h LINK0_ILA_K_M1

7Ah LINK0_ILA_M_M1

7Bh LINK0_CS 0 LINK0_ILA_N_M1

7Ch LINK0_SUBCLASSV LINK0_ILA_NPRIME_M1

7Dh LINK0_JESDV LINK0_ILA_S_M1

7Eh LINK0_ILA_HD 0 0 LINK0_CF

7Fh LINK0_RES1

80h LINK0_RES2

83h 0 0 0 0 0 0 0

LINK0_JESD_IL

A_CONFIG_OV

ERRIDE

84h LINK0_K_M1

85h 0 0 0 0

LINK0_ENABLE

_F_CHAR_ON_

MFEND

LINK0_DISABLE

_F_CHAR

LINK0_DISABLE

_A_CHAR

LINK0_NO_LAN

E_SYNC

86h 0 0 0 0

LINK0_SYNC_F

_CTR_INCR_OV

R_EN

LINK0_SYNC_F_CTR_INCR_OVR_VAL

Loading...

Loading...