ADC JESD Register Map

www.ti.com

374

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

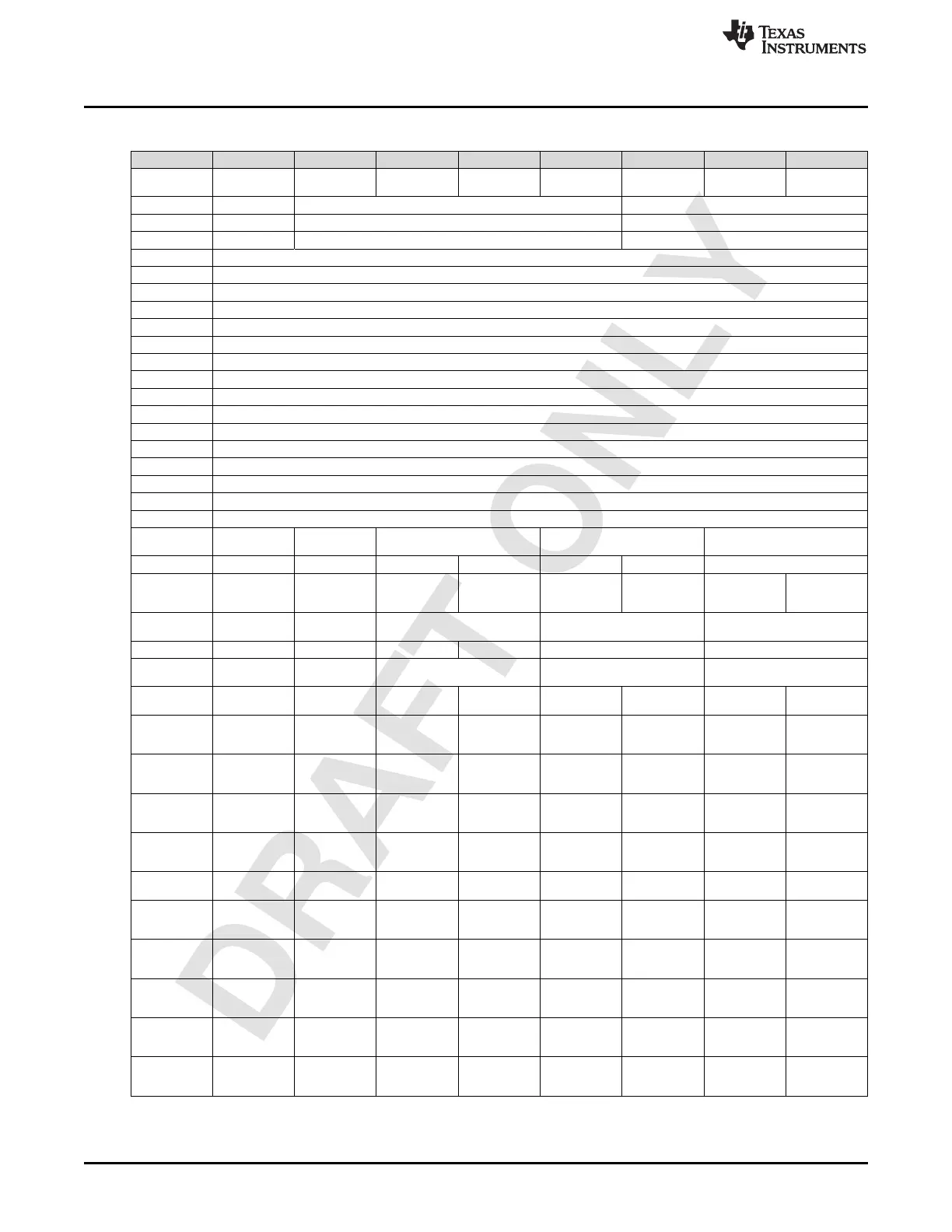

Table 2-501. adc_jesd Register Map (continued)

ADDRESS (Hex) D7 D6 D5 D4 D3 D2 D1 D0

108h 0 0 0 0 0 0

HOLD_JESD_S

YNC_ERR

HOLD_JESD_ST

ATE

109h 0 RX1_JESD_RAMPTEST_INCR RX1_JESD_TEST_SIG_GEN_MODE

10Ah 0 RX2_JESD_RAMPTEST_INCR RX2_JESD_TEST_SIG_GEN_MODE

10Bh 0 FB_JESD_RAMPTEST_INCR FB_JESD_TEST_SIG_GEN_MODE

10Ch JESD_SHORT_TEST_PATTERN_INPUT0[7:0]

10Dh JESD_SHORT_TEST_PATTERN_INPUT0[15:8]

10Eh JESD_SHORT_TEST_PATTERN_INPUT1[7:0]

10Fh JESD_SHORT_TEST_PATTERN_INPUT1[15:8]

110h JESD_SHORT_TEST_PATTERN_INPUT2[7:0]

111h JESD_SHORT_TEST_PATTERN_INPUT2[15:8]

112h JESD_SHORT_TEST_PATTERN_INPUT3[7:0]

113h JESD_SHORT_TEST_PATTERN_INPUT3[15:8]

114h JESD_SHORT_TEST_PATTERN_INPUT4[7:0]

115h JESD_SHORT_TEST_PATTERN_INPUT4[15:8]

116h JESD_SHORT_TEST_PATTERN_INPUT5[7:0]

117h JESD_SHORT_TEST_PATTERN_INPUT5[15:8]

118h JESD_SHORT_TEST_PATTERN_INPUT6[7:0]

119h JESD_SHORT_TEST_PATTERN_INPUT6[15:8]

11Ah JESD_SHORT_TEST_PATTERN_INPUT7[7:0]

11Bh JESD_SHORT_TEST_PATTERN_INPUT7[15:8]

11Ch 0 0

CTRL_FB_MAPPER_CLK_GATING

CTRL_RX2_MAPPER_CLK_GATIN

G

CTRL_RX1_MAPPER_CLK_GATIN

G

11Dh 0 0 0 0 0 0 CTRL_RX3_RX4_CLK_GATING

11Eh 0 0 0 0 0 0 0

EN_SERDES_FI

FO_DATA_GATI

NG

120h 0 0

CTRL_RX3_RX4_MSF_SIG_INVALI

D

CTRL_RX2_MSF_SIG_INVALID CTRL_RX1_MSF_SIG_INVALID

121h 0 0 0 0 CTRL_FB2_MSF_SIG_INVALID CTRL_FB1_MSF_SIG_INVALID

122h 0 0

CTRL_TDD_FB_MAPPER_SIG_INV

ALID

CTRL_TDD_RX2_MAPPER_SIG_IN

VALID

CTRL_TDD_RX1_MAPPER_SIG_IN

VALID

124h

CLEAR_JESD_C

LK_FB_P0

CLEAR_JESD_C

LK_RX2_P2

CLEAR_JESD_C

LK_RX2_P0

CLEAR_JESD_C

LK_RX1_P2

CLEAR_JESD_C

LK_RX1_P0

CLEAR_DDC_R

D_CLK_FB

CLEAR_DDC_R

D_CLK_RX2

CLEAR_DDC_R

D_CLK_RX1

125h

CLEAR_JESD_C

LK_RX2_P0_MS

F_RD

CLEAR_JESD_C

LK_RX1_P0_MS

F_RD

CLEAR_JESD_C

LK_DIV2_FB_P3

CLEAR_JESD_C

LK_DIV2_FB_P1

CLEAR_JESD_C

LK_DIV2_RX2_P

2

CLEAR_JESD_C

LK_DIV2_RX1_P

0

CLEAR_JESD_C

LK_FB_P3

CLEAR_JESD_C

LK_FB_P1

126h 0 0 0

CLEAR_SERDE

S_TXBCLK3

CLEAR_SERDE

S_TXBCLK2

CLEAR_SERDE

S_TXBCLK1

CLEAR_SERDE

S_TXBCLK0

CLEAR_JESD_C

LK_FB_P0_MSF

_RD

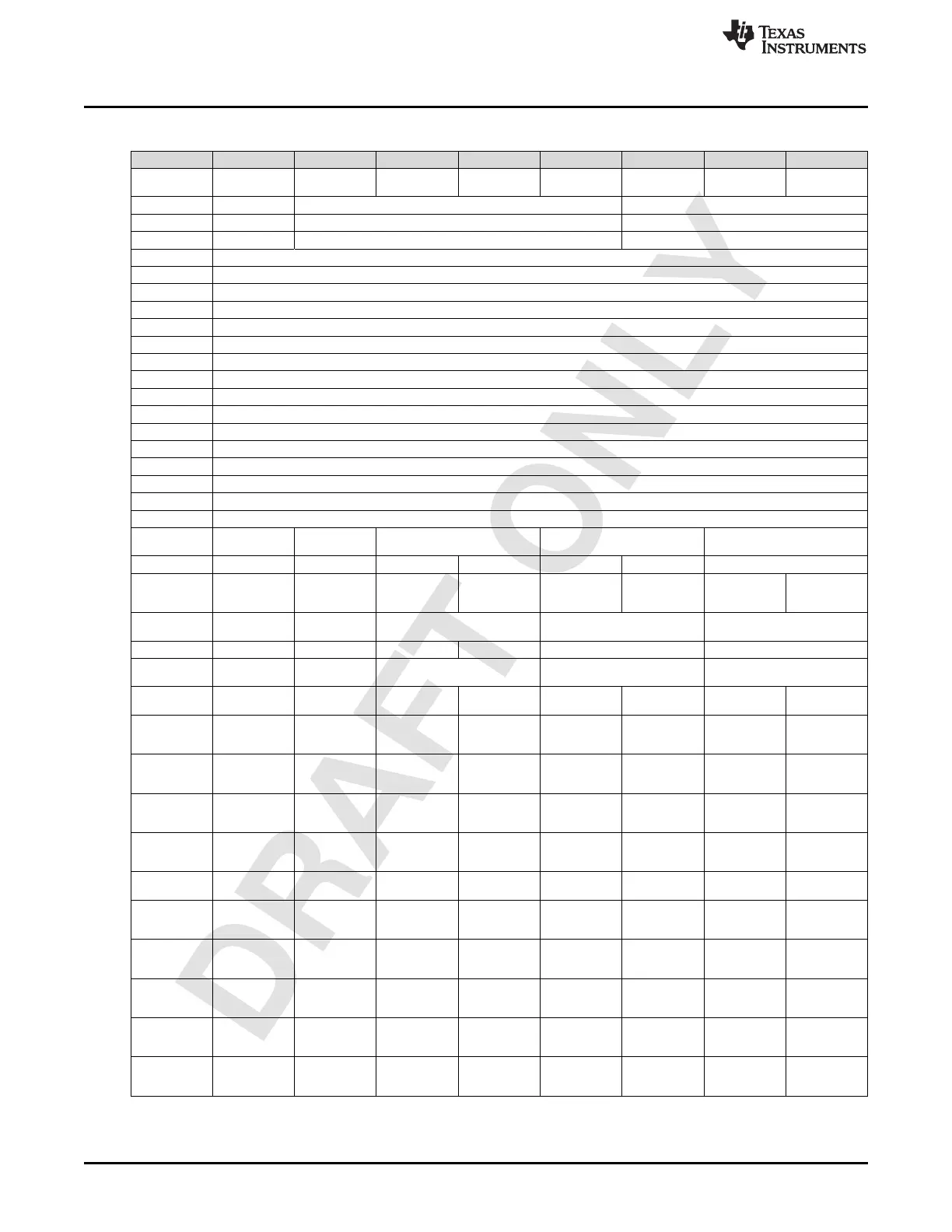

128h

CLEAR_JESD_S

YSREF_FB_P0

CLEAR_JESD_S

YSREF_RX2_P2

CLEAR_JESD_S

YSREF_RX2_P0

CLEAR_JESD_S

YSREF_RX1_P2

CLEAR_JESD_S

YSREF_RX1_P0

CLEAR_DDC_R

D_SYSREF_FB

CLEAR_DDC_R

D_SYSREF_RX

2

CLEAR_DDC_R

D_SYSREF_RX

1

129h

CLEAR_JESD_S

YSREF_RX2_P0

_MSF_RD

CLEAR_JESD_S

YSREF_RX1_P0

_MSF_RD

CLEAR_JESD_S

YSREF_DIV2_F

B_P3

CLEAR_JESD_S

YSREF_DIV2_F

B_P1

CLEAR_JESD_S

YSREF_DIV2_R

X2_P2

CLEAR_JESD_S

YSREF_DIV2_R

X1_P0

CLEAR_JESD_S

YSREF_FB_P3

CLEAR_JESD_S

YSREF_FB_P1

12Ch

MONITOR_JES

D_CLK_FB_P0

MONITOR_JES

D_CLK_RX2_P2

MONITOR_JES

D_CLK_RX2_P0

MONITOR_JES

D_CLK_RX1_P2

MONITOR_JES

D_CLK_RX1_P0

MONITOR_DDC

_RD_CLK_FB

MONITOR_DDC

_RD_CLK_RX2

MONITOR_DDC

_RD_CLK_RX1

12Dh

MONITOR_JES

D_CLK_RX2_P0

_MSF_RD

MONITOR_JES

D_CLK_RX1_P0

_MSF_RD

MONITOR_JES

D_CLK_DIV2_F

B_P3

MONITOR_JES

D_CLK_DIV2_F

B_P1

MONITOR_JES

D_CLK_DIV2_R

X2_P2

MONITOR_JES

D_CLK_DIV2_R

X1_P0

MONITOR_JES

D_CLK_FB_P3

MONITOR_JES

D_CLK_FB_P1

12Eh 0 0 0

MONITOR_SER

DES_TXBCLK3

MONITOR_SER

DES_TXBCLK2

MONITOR_SER

DES_TXBCLK1

MONITOR_SER

DES_TXBCLK0

MONITOR_JES

D_CLK_FB_P0_

MSF_RD

130h

MONITOR_JES

D_SYSREF_FB_

P0

MONITOR_JES

D_SYSREF_RX

2_P2

MONITOR_JES

D_SYSREF_RX

2_P0

MONITOR_JES

D_SYSREF_RX

1_P2

MONITOR_JES

D_SYSREF_RX

1_P0

MONITOR_DDC

_RD_SYSREF_F

B

MONITOR_DDC

_RD_SYSREF_

RX2

MONITOR_DDC

_RD_SYSREF_

RX1

131h

MONITOR_JES

D_SYSREF_RX

2_P0_MSF_RD

MONITOR_JES

D_SYSREF_RX

1_P0_MSF_RD

MONITOR_JES

D_SYSREF_DIV

2_FB_P3

MONITOR_JES

D_SYSREF_DIV

2_FB_P1

MONITOR_JES

D_SYSREF_DIV

2_RX2_P2

MONITOR_JES

D_SYSREF_DIV

2_RX1_P0

MONITOR_JES

D_SYSREF_FB_

P3

MONITOR_JES

D_SYSREF_FB_

P1

132h 0 0 0 0 0 0 0

MONITOR_JES

D_SYSREF_FB_

P0_MSF_RD

Loading...

Loading...