www.ti.com

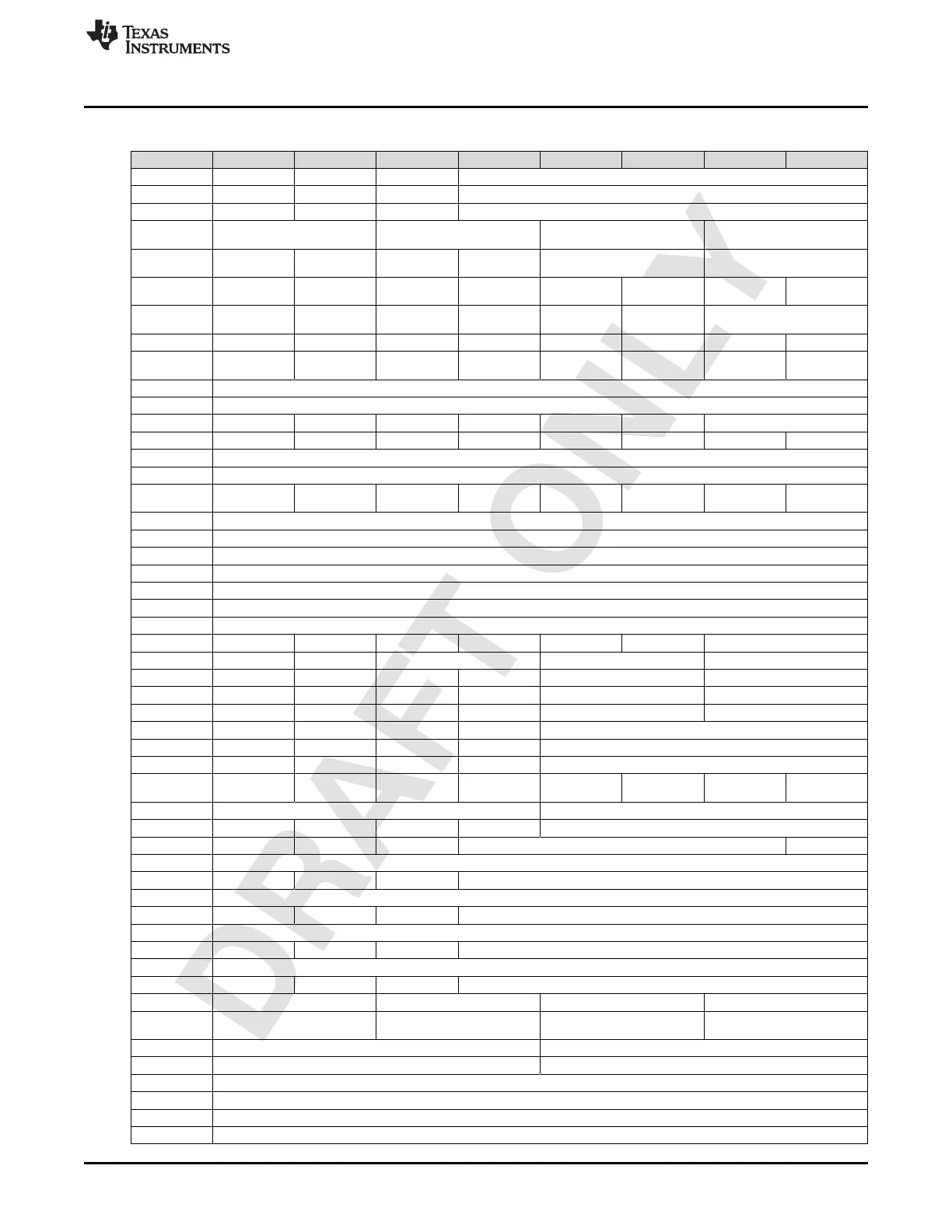

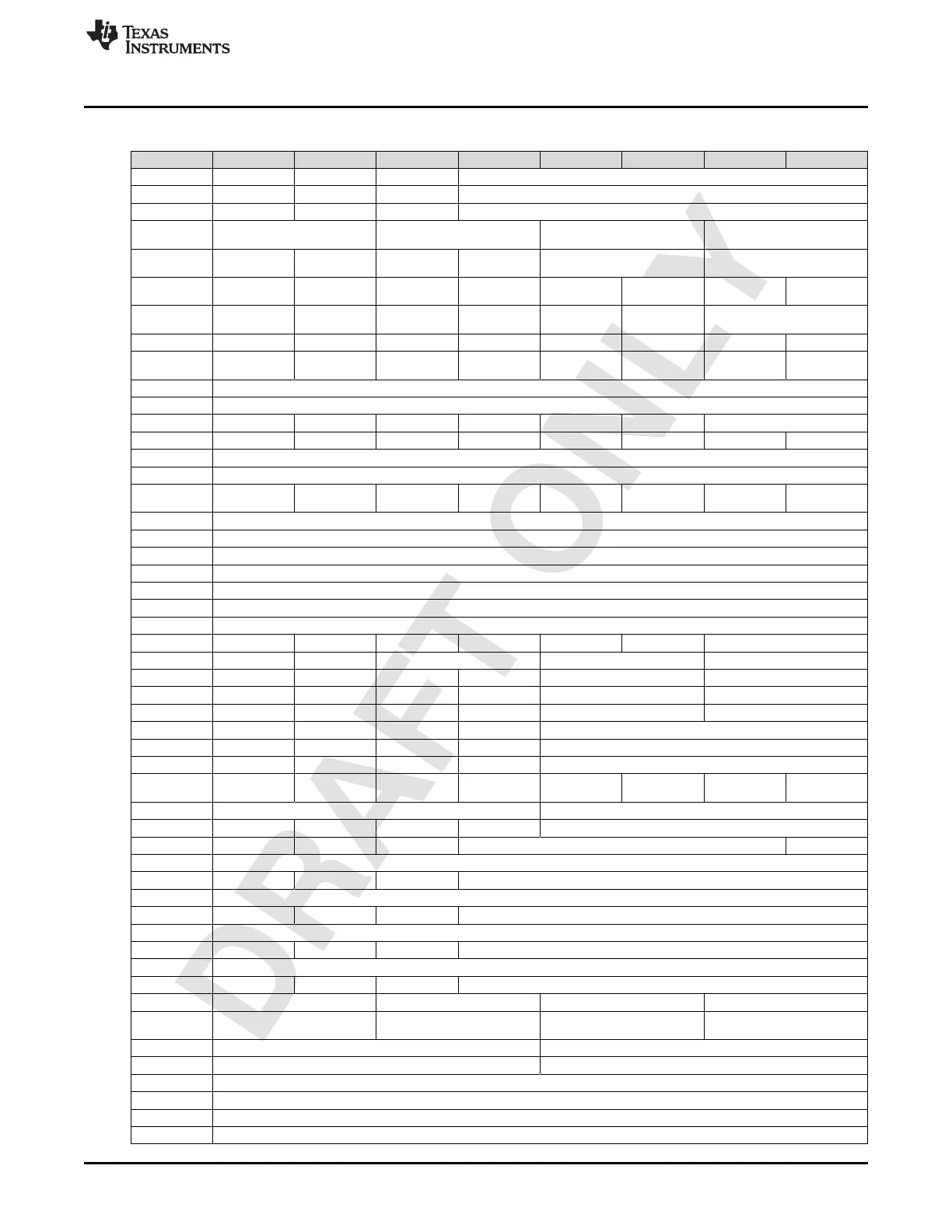

ADC JESD Register Map

373

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-501. adc_jesd Register Map (continued)

ADDRESS (Hex) D7 D6 D5 D4 D3 D2 D1 D0

BDh 0 0 0 LID1

BEh 0 0 0 LID2

BFh 0 0 0 LID3

C0h

LINK1_SYNC_FIFO_S2_TO_S1_OF

FSET

LINK1_SYNC_FIFO_S1_TO_S2_OF

FSET

LINK0_SYNC_FIFO_S2_TO_S1_OF

FSET

LINK0_SYNC_FIFO_S1_TO_S2_OF

FSET

C1h 0 0 0 0

LINK2_SYNC_FIFO_S2_TO_S1_OF

FSET

LINK2_SYNC_FIFO_S1_TO_S2_OF

FSET

C8h 0 0 0 0 0 0 0

SYNC_HEADER

_FLIP

C9h 0 0 0 0

JESDC_ENCODI

NG_80B_66BZ

JESDC_CRC_M

ODE

JESDC_ENCODING_MODE

CAh 0 0 0 0 0 0 0 SCR_64B_EN

CBh 0 0 0 0 0 0

reserved

SCR_64B_BIT_

SWAP_DISABLE

CCh JESDC_CMD[7:0]

CDh JESDC_CMD[15:8]

CEh 0 0 0 0 0 0 JESDC_CMD[17:16]

CFh 0 0 0 0 0 0 0 FEC_MASK_EN

D0h INIT_PRBS_SEED[7:0]

D1h INIT_PRBS_SEED[15:8]

D2h 0 0 0 0 0 0 0

INIT_PRBS_SEE

D[16]

D4h SCR_64B_INITVAL[7:0]

D5h SCR_64B_INITVAL[15:8]

D6h SCR_64B_INITVAL[23:16]

D7h SCR_64B_INITVAL[31:24]

D8h SCR_64B_INITVAL[39:32]

D9h SCR_64B_INITVAL[47:40]

DAh SCR_64B_INITVAL[55:48]

DBh 0 0 0 0 0 0 SCR_64B_INITVAL[57:56]

E0h 0 0 SAMPLE_DROP_MODE_FB SAMPLE_DROP_MODE_RX2 SAMPLE_DROP_MODE_RX1

E1h 0 0 0 0 RXA_SD_CLK_DIV_N_M1 RXA_SD_CLK_DIV_M

E2h 0 0 0 0 RXB_SD_CLK_DIV_N_M1 RXB_SD_CLK_DIV_M

E3h 0 0 0 0 FBAB_SD_CLK_DIV_N_M1 FBAB_SD_CLK_DIV_M

F0h 0 0 0 0 ALARMS_SERDES_FIFO_ERRORS_CLEAR

F1h 0 0 0 0 ALARMS_SERDES_FIFO_ERRORS_MASK

F2h 0 0 0 0 SERDES_FIFO_ERROR_DIFF2_MASK

F3h 0 0 0 0 0 0 0

SERDES_FIFO_

PTR_SAMPLE

F4h ALARMS_SERDES_FIFO_ERRORS_UNMASKED ALARMS_SERDES_FIFO_ERRORS

F5h 0 0 0 0 SERDES_FIFO_WR_PTR_SAMPLE

F6h 0 0 0 SERDES_FIFO_RD_PTR_SAMPLE 0

F8h JESD_INTERNAL_CTR_ON_SYNC_DEASSERT0[7:0]

F9h 0 0 0 JESD_INTERNAL_CTR_ON_SYNC_DEASSERT0[12:8]

FAh JESD_INTERNAL_CTR_ON_SYNC_DEASSERT1[7:0]

FBh 0 0 0 JESD_INTERNAL_CTR_ON_SYNC_DEASSERT1[12:8]

FCh JESD_INTERNAL_CTR_ON_SYNC_DEASSERT2[7:0]

FDh 0 0 0 JESD_INTERNAL_CTR_ON_SYNC_DEASSERT2[12:8]

FEh JESD_INTERNAL_CTR_ON_SYNC_DEASSERT3[7:0]

FFh 0 0 0 JESD_INTERNAL_CTR_ON_SYNC_DEASSERT3[12:8]

100h JESD_SYNC_STATE_LANE3 JESD_SYNC_STATE_LANE2 JESD_SYNC_STATE_LANE1 JESD_SYNC_STATE_LANE0

101h

JESD_PREV_SYNC_STATE_LANE

3

JESD_PREV_SYNC_STATE_LANE

2

JESD_PREV_SYNC_STATE_LANE

1

JESD_PREV_SYNC_STATE_LANE

0

102h JESD_MISC_STATUS_LANE1 JESD_MISC_STATUS_LANE0

103h JESD_MISC_STATUS_LANE3 JESD_MISC_STATUS_LANE2

104h JESD_SYNC_ERR_CNT_LANE0

105h JESD_SYNC_ERR_CNT_LANE1

106h JESD_SYNC_ERR_CNT_LANE2

107h JESD_SYNC_ERR_CNT_LANE3

Loading...

Loading...