www.ti.com

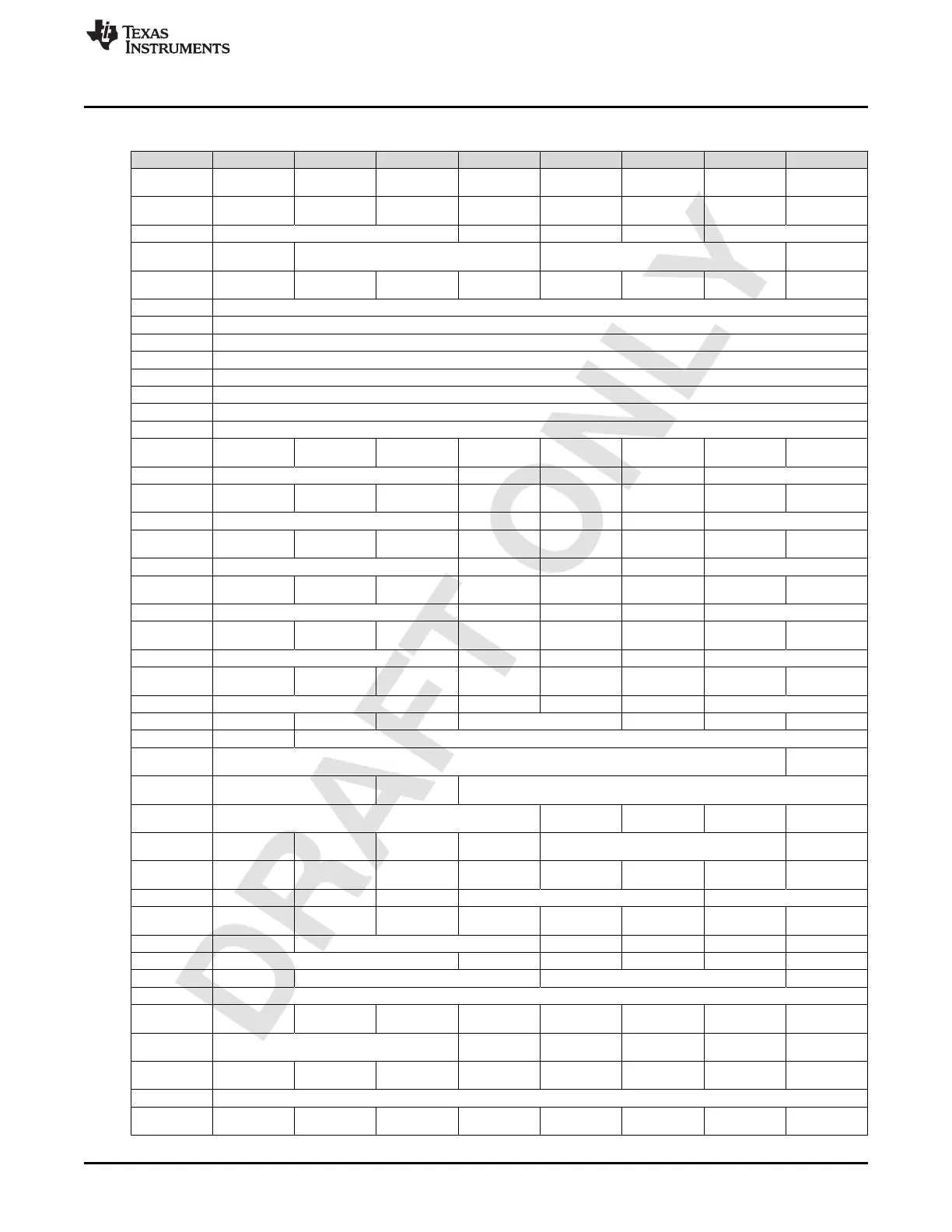

SERDES Register Map

465

SBAU337–May 2020

Submit Documentation Feedback

Copyright © 2020, Texas Instruments Incorporated

Serial Interface Register Maps

Table 2-720. Serdes Register Map (continued)

ADDRESS (Hex) D7 D6 D5 D4 D3 D2 D1 D0

41FBh

EXRESET_INTP

ADDCAP_CLKP

HASE

41FCh

VGAVDSAT[0]

PU_RX_INTP_L

ANE

41FDh VCASGA5X VGAVDSAT[2:1]

41FEh

RX_AC_COUPL

E_EN

VGAVDCOM1 VGAVDCOM2

41FFh

PU_RX_AGC_L

ANE

RX_CTLE_BIAS

4

RX_INPUT_EN

4876h FREQ_INIT1[7:0]

4877h FREQ_INIT1[15:8]

4878h FREQ_INIT2[7:0]

4879h FREQ_INIT2[15:8]

487Ah FREQ_INIT3[7:0]

487Bh FREQ_INIT3[15:8]

487Ch FREQ_INIT4[7:0]

487Dh FREQ_INIT4[15:8]

49CAh

TX_VREG_IBIA

S_LANE3[0]

49CBh TX_VREG_IBIAS_LANE2 TX_VREG_IBIAS_LANE3[2:1]

49CCh

TX_VREG_IBIA

S_LANE1[0]

49CDh TX_VREG_IBIAS_LANE0 TX_VREG_IBIAS_LANE1[2:1]

49D0h

RX_SLICER_BIA

S_LANE3[0]

49D1h RX_AGCBUFDAC_LANE3 RX_SLICER_BIAS_LANE3[2:1]

49D4h

RX_SLICER_BIA

S_LANE2[0]

49D5h RX_AGCBUFDAC_LANE2 RX_SLICER_BIAS_LANE2[2:1]

49D8h

RX_SLICER_BIA

S_LANE1[0]

49D9h RX_AGCBUFDAC_LANE1 RX_SLICER_BIAS_LANE1[2:1]

49DCh

RX_SLICER_BIA

S_LANE0[0]

49DDh RX_AGCBUFDAC_LANE0 RX_SLICER_BIAS_LANE0[2:1]

49DEh TX_INTP_DIS REFCLK_DIV

49DFh INTP_INIT_EN INTP_INIT_VAL

49E0h

OW_FREQ_ACC_TOP[6:0]

RECOVERED_C

LK_SEL

49E1h

LANE_RCVD_CLK_SRC

OWEN_FREQ_A

CC_TOP

OW_FREQ_ACC_TOP[11:7]

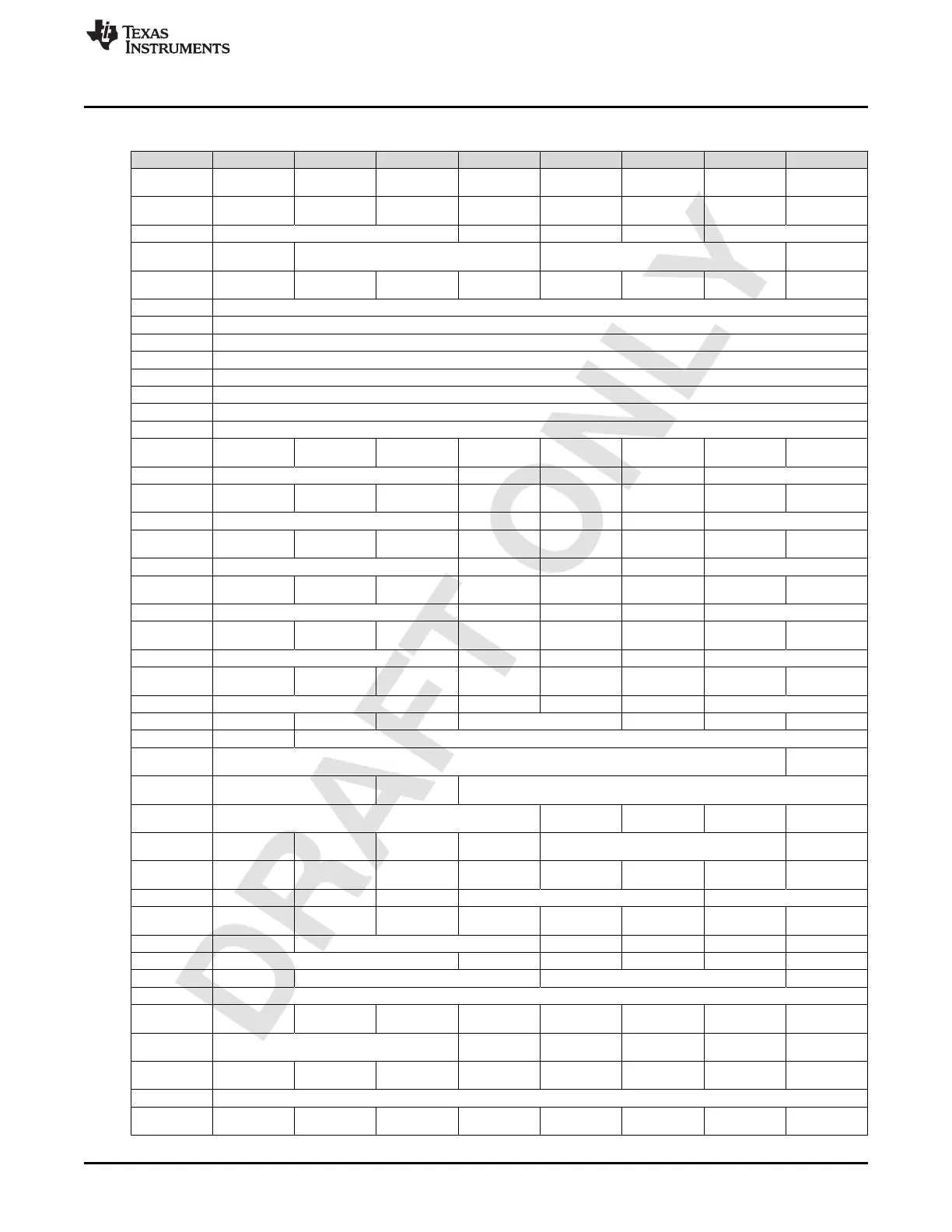

49E2h

VTSTPGROUP_TX[3:0]

ENTTSTPGROU

P_TX

49E3h

PU_TX_DRV_LA

NE0

PU_TX_DRV_LA

NE1

PU_TX_DRV_LA

NE2

PU_TX_DRV_LA

NE3

TEST_MODE_TX

VTSTPGROUP_

TX[4]

49E4h

TX_PLL_BIAS1[

0]

49E5h TX_PLL_BIAS2 TX_PLL_BIAS1[2:1]

49E6h

TX_PLL_VCO_R

ANGE_MSB

49E8h VRVDD_TX

49E9h TX_PLL_VCO_RANGE_LSB

49EAh PU_TX_PLL TX_CHARGE_PUMP_CUR TX_VCO_CURRENT

49EBh TX_PLL_N

49ECh

TX_REFCLK_SE

L

49EDh

TX_PLL_BIAS4

PU_TX_BANDG

AP

PU_RVDD_TX

EN_RVDDVCO_

TX

49EEh

TEST_MUX_SE

L_B[0]

49EFh TEST_MUX_SEL_B[8:1]

49F0h

PU_RX_INTP_L

ANE3

Loading...

Loading...