ADSP-214xx SHARC Processor Hardware Reference A-241

Registers Reference

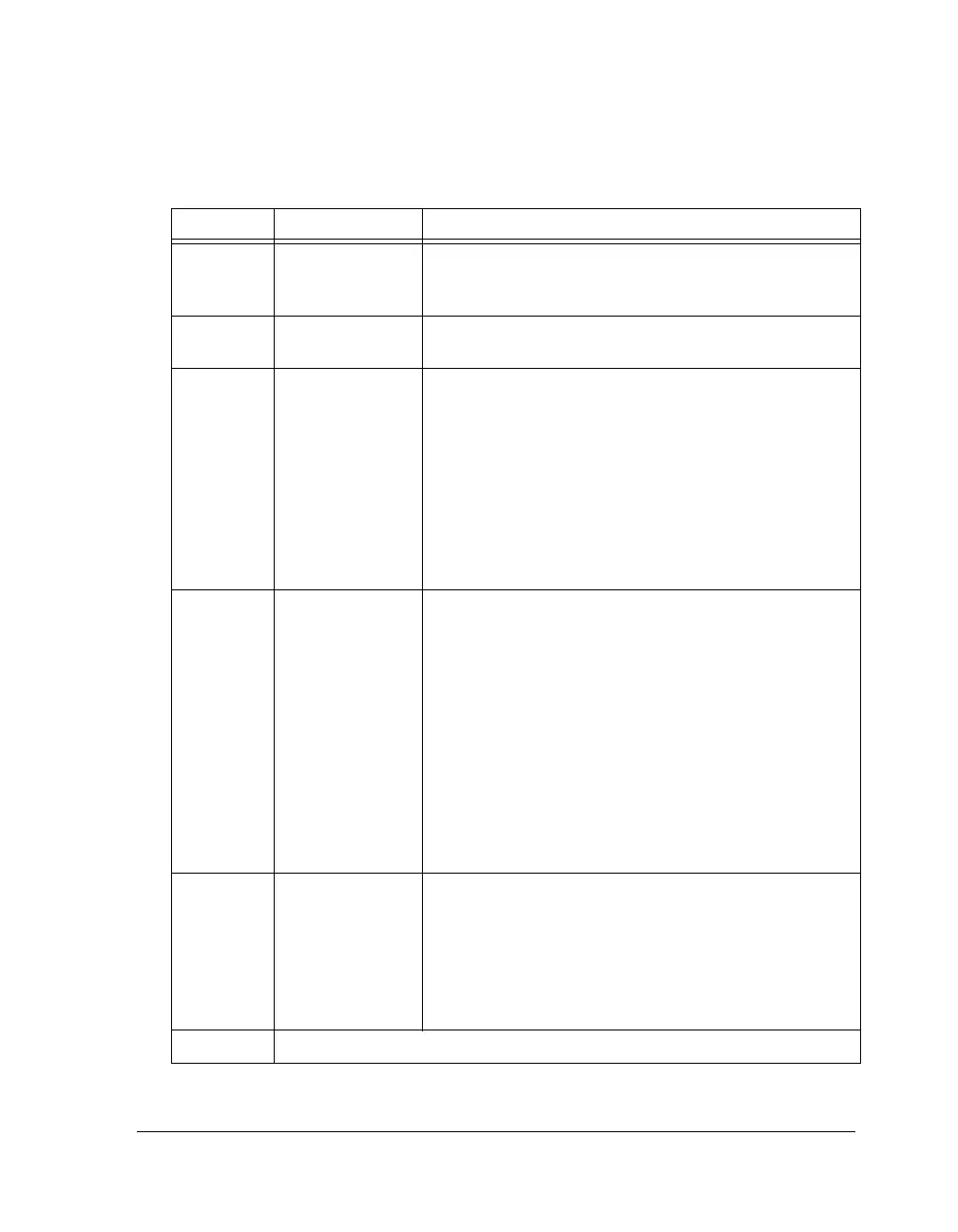

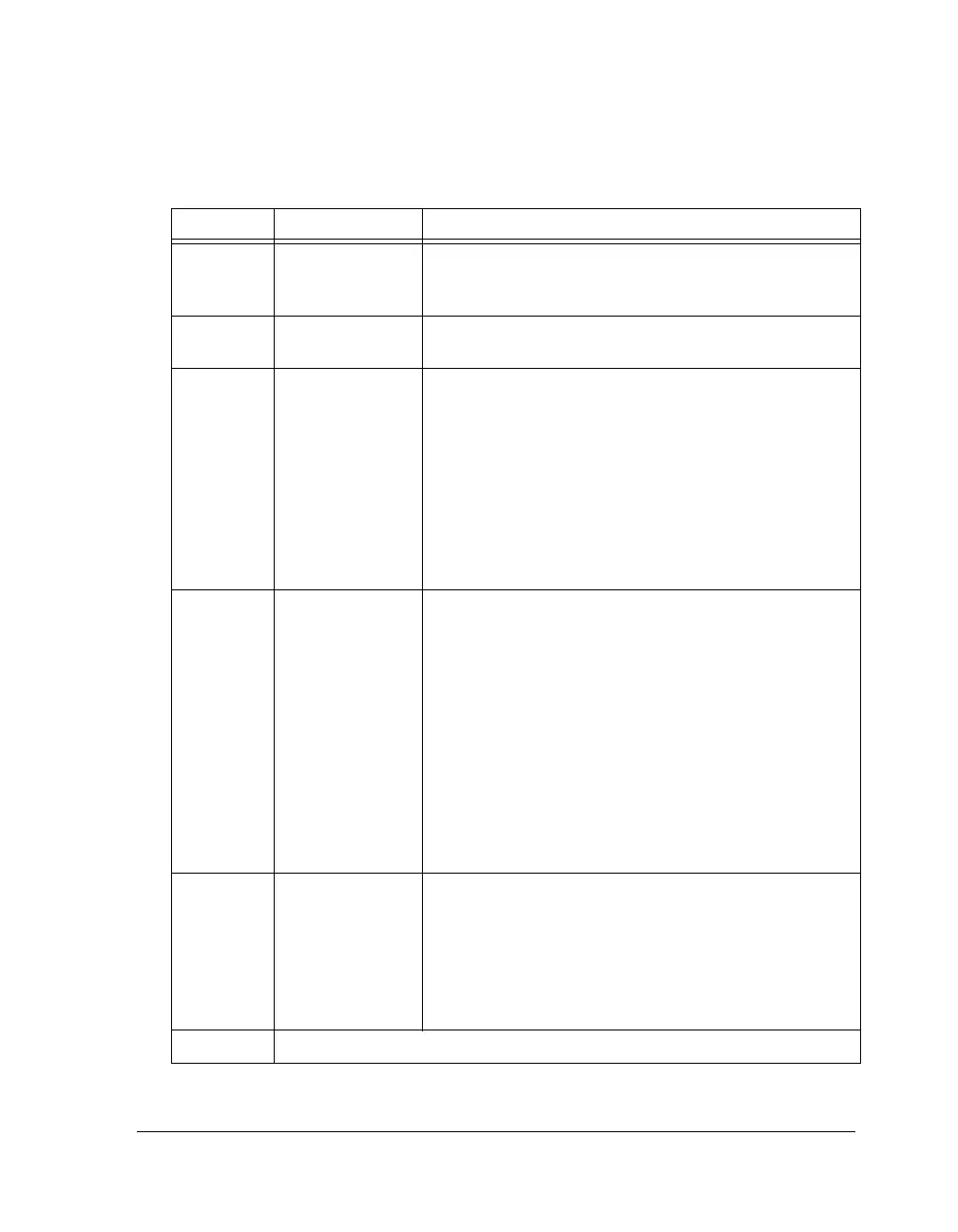

3 (RO) TXS Transmit Data Buffer Status. TXSPI data buffer status.

0 = Empty

1 = Full

4 (W1C) ROVF Reception Error. ROVF is set when data is received with

receive buffer full.

5 (RO) RXS Receive Data Buffer Status. The ROVF flag (bit 4) is when a

new transfer has completed before the previous data is read

from the RXSPI register. This bit indicates that a new word

was received while the receive buffer was full. The ROVF flag

is cleared by a W1C-type software operation. The state of the

GM bit in the SPICTL register determines whether the

RXSPI register is updated with the newly received data or

whether that new data is discarded.

0 = Empty

1 = Full

6 (W1C) TXCOL Transmit Collision Error. When TXCOL is set, it is possible

that corrupt data was transmitted.

The TXCOL flag (bit 6) is set when a write to the TXSPI reg-

ister coincides with the load of the shift register. The write to

TXSPI can be via the software or the DMA. This bit indicates

that corrupt data may have been loaded into the shift register

and transmitted. In this case, the data in TXSPI may not

match what was transmitted. This error can easily be avoided

by proper software control. The TXCOL bit is cleared by a

W1C-type software operation.

Note that this bit is never set when the SPI is configured as a

slave with CPHASE = 0. The collision may occur, but it can-

not be detected.

7 (RO) SPIFE External Transaction Complete. Set (= 1) when the SPI

transaction is complete on the external interface. This bit is

very useful in DMA mode showing that the peripheral has

completed all the external transfers corresponding to the

DMA programmed. For more information, see “Transfer Ini-

tiate Mode” on page 15-13 and “DMA Transfers” on

page 15-21.

31–8 Reserved

Table A-125. SPISTAT Register Bit Descriptions (RO) (Cont’d)

Bit Name Description

Loading...

Loading...