FIR Accelerator

6-32 ADSP-214xx SHARC Processor Hardware Reference

• 32-bit floating-point MAC operation generates 32-bit multiply

results.

• 32-bit fixed-point operation generates 80-bit results.

Partial Sum Register

The partial sum register is useful for floating-point multi-iteration mode.

For a particular channel, the intermediate MAC result is written to the

internal memory’s output buffer. If the same channel is requested again,

the partial result register is updated with the intermediate MAC result via

DMA from the internal memory’s output buffer and added to the current

MAC result after each iteration. This process is repeated until all iterations

are done (the entire soft filter length is processed).

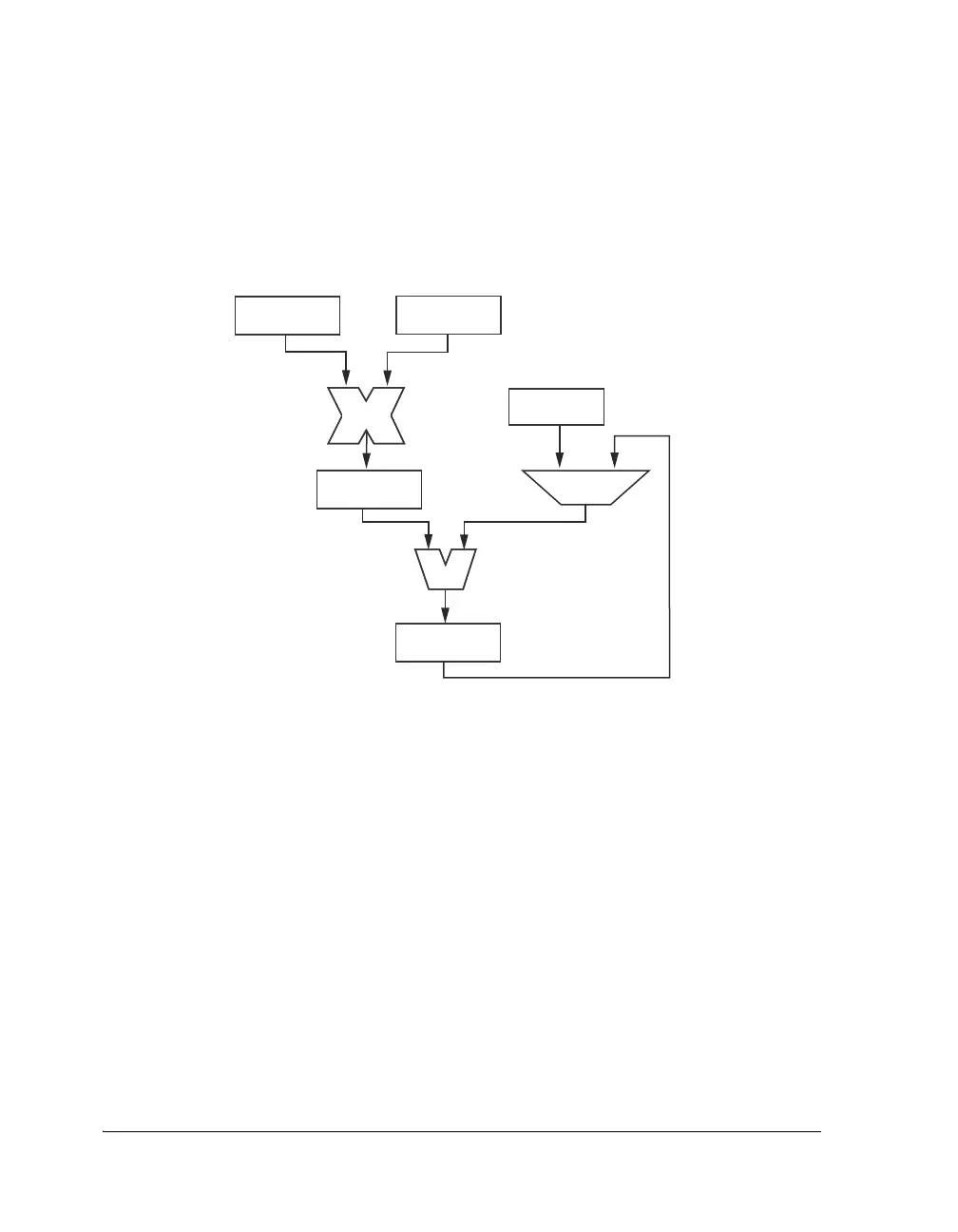

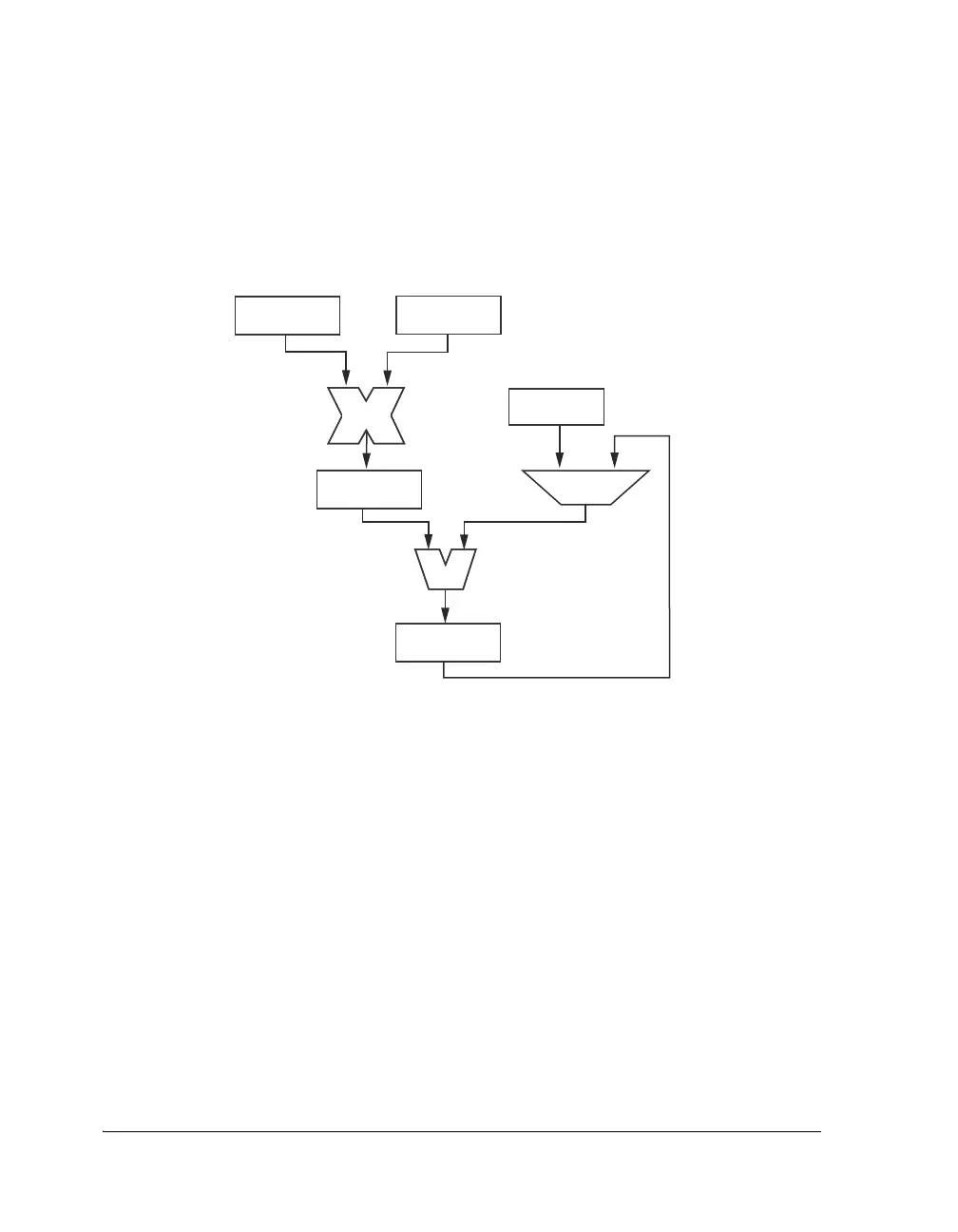

Figure 6-4. FIR MAC Unit

MULT

ADDER

DATA REGISTER

PARTIAL SUM

REGISTER

COEFFICIENT

REGISTER

MULT RESULT

REGISTER

MAC RESULT

REGISTER

MUX

Loading...

Loading...