Operating Modes

16-12 ADSP-214xx SHARC Processor Hardware Reference

is generated on the

TIMERx_O signal. If the PULSE bit is not set, the pulse is

active low.

Pulse Mode

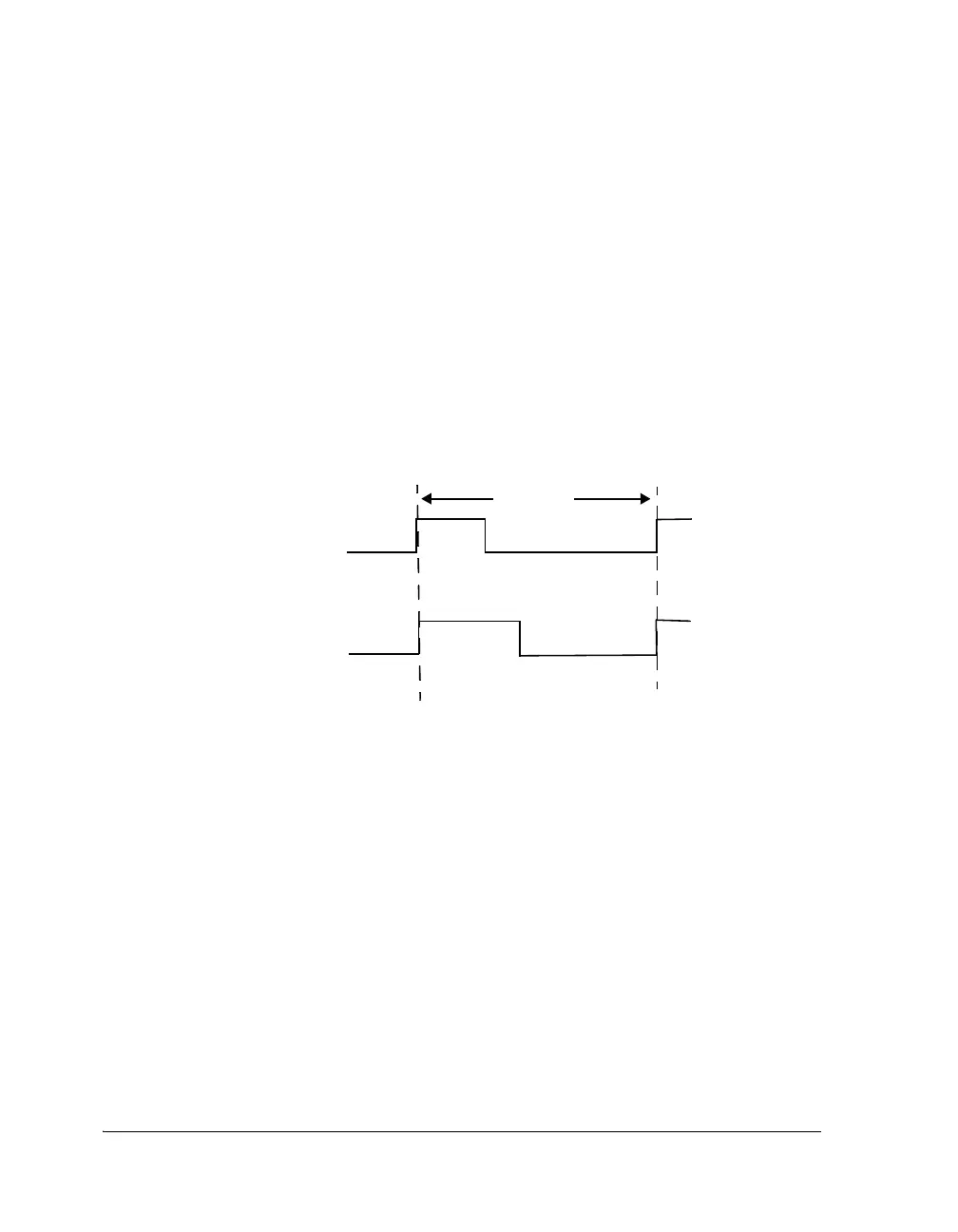

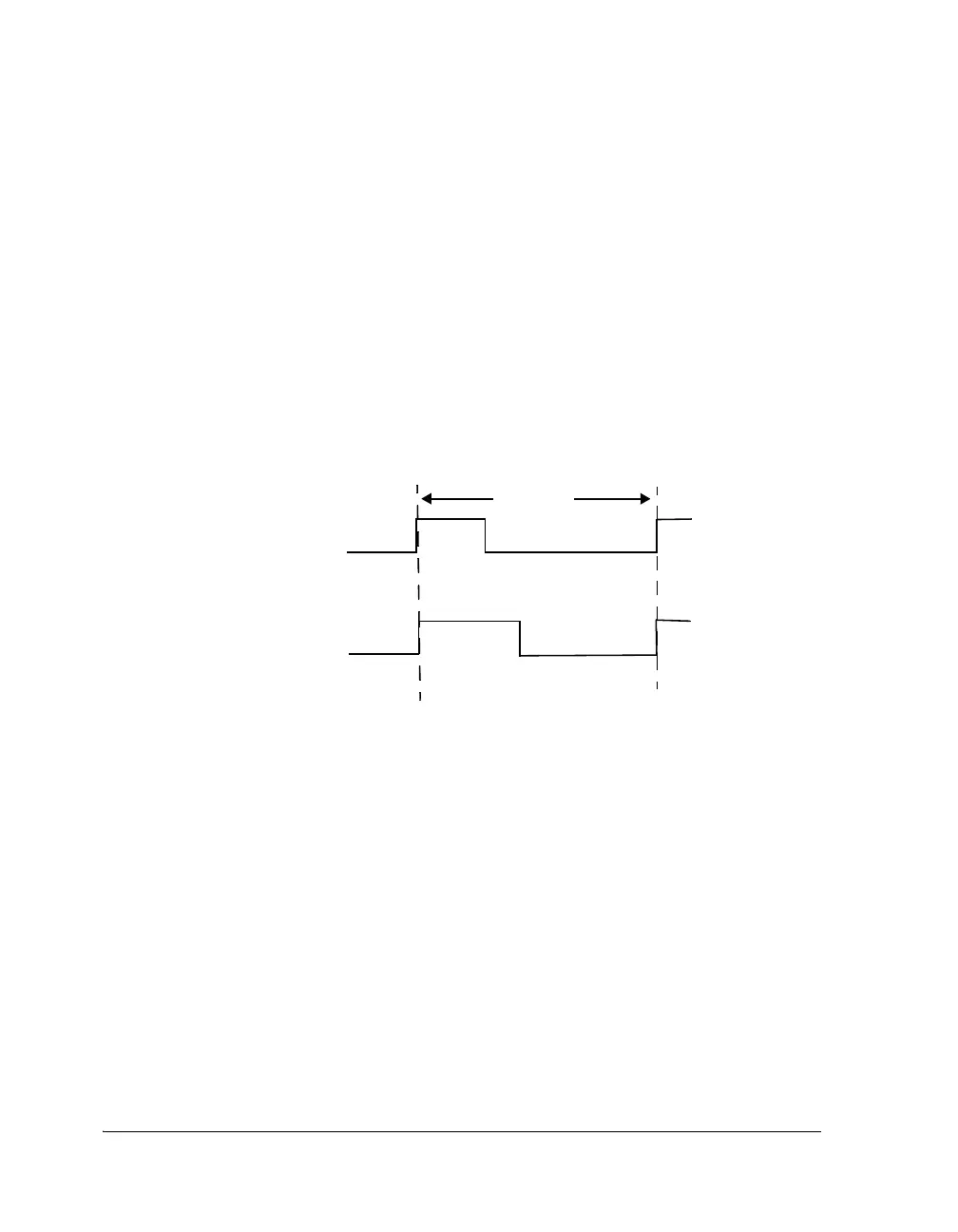

The waveform produced in PWM_OUT mode with PRDCNT = 1 normally

has a fixed assertion time and a programmable deassertion time (via the

TMxW register). When both timers are running synchronously by the same

period settings, the pulses are aligned to the asserting edge as shown in

Figure 16-4. Note that the timer does not support toggling of the PULSE

bit in each period.

Pulse Width Count and Capture Mode (WDTH_CAP)

To enable WDTH_CAP mode, set the TIMODE1–0 bits in the TMxCTL regis-

ter to 10. This configures the

TIMERx signal as an input signal with its

polarity determined by

PULSE. If PULSE is set (= 1), an active high width

pulse waveform is measured at the

TIMER_Ix signal. If PULSE is cleared (=

0), an active low width pulse waveform is measured at the TIMERx_I signal.

The internally-clocked timer is used to determine the period and pulse

width of externally-applied rectangular waveforms. The period and width

Figure 16-4. Timers with Pulses Aligned to Asserting Edge

PULSE = 1

PULSE = 1

TMR0

TMR1

ACTIVE

HIGH

ACTIVE

HIGH

PERIOD 1

TIMER

ENABLE

Loading...

Loading...