Peripheral Registers

A-72 ADSP-214xx SHARC Processor Hardware Reference

Polarity Select Registers (PWMPOLx)

These 16-bit registers, described in Table A-40, control the polarity of the

four PWM groups which can be set to either active high or active low.

Note that bit 1 has priority over bit 0, bit 3 over bit 2 and so on. In paired

mode, it is expected to maintain polarity coherency by setting the same

polarity for both the high and low side of a PWM pair.

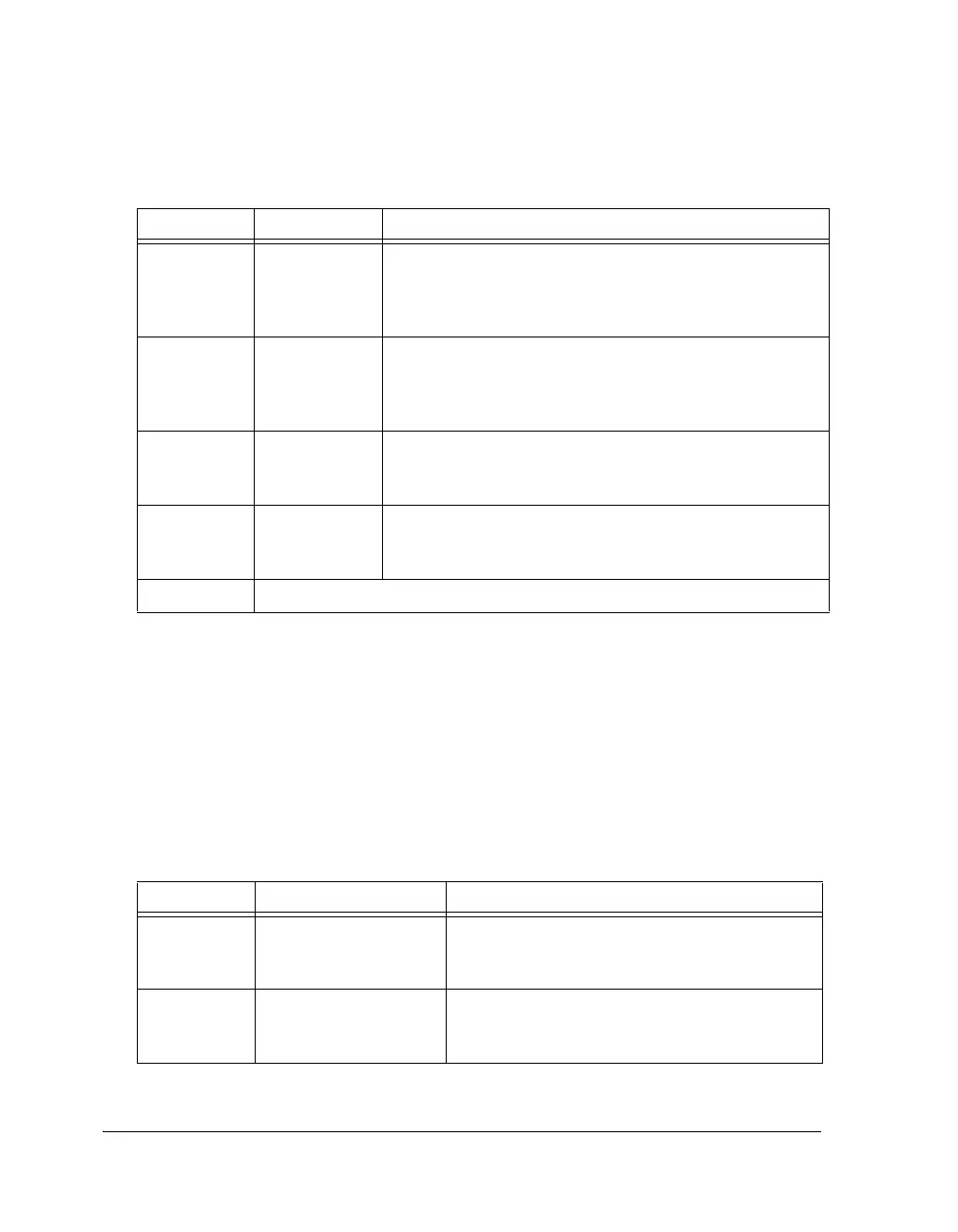

2PWM_AHChannel A High Disable. Enables or disables the channel A

output signal.

0 = Enable

1 = Disable

3PWM_ALChannel A Low Disable. Enables or disables the channel A

output signal.

0 = Enable

1 = Disable

4BHBL_XOVRCrossover Enable for BH/BL Pair.

0 = Disable

1 = Enable

5 AHBL_XOVR Crossover Enable for AH/AL Pair.

0 = Disable

1 = Enable

15–6 Reserved

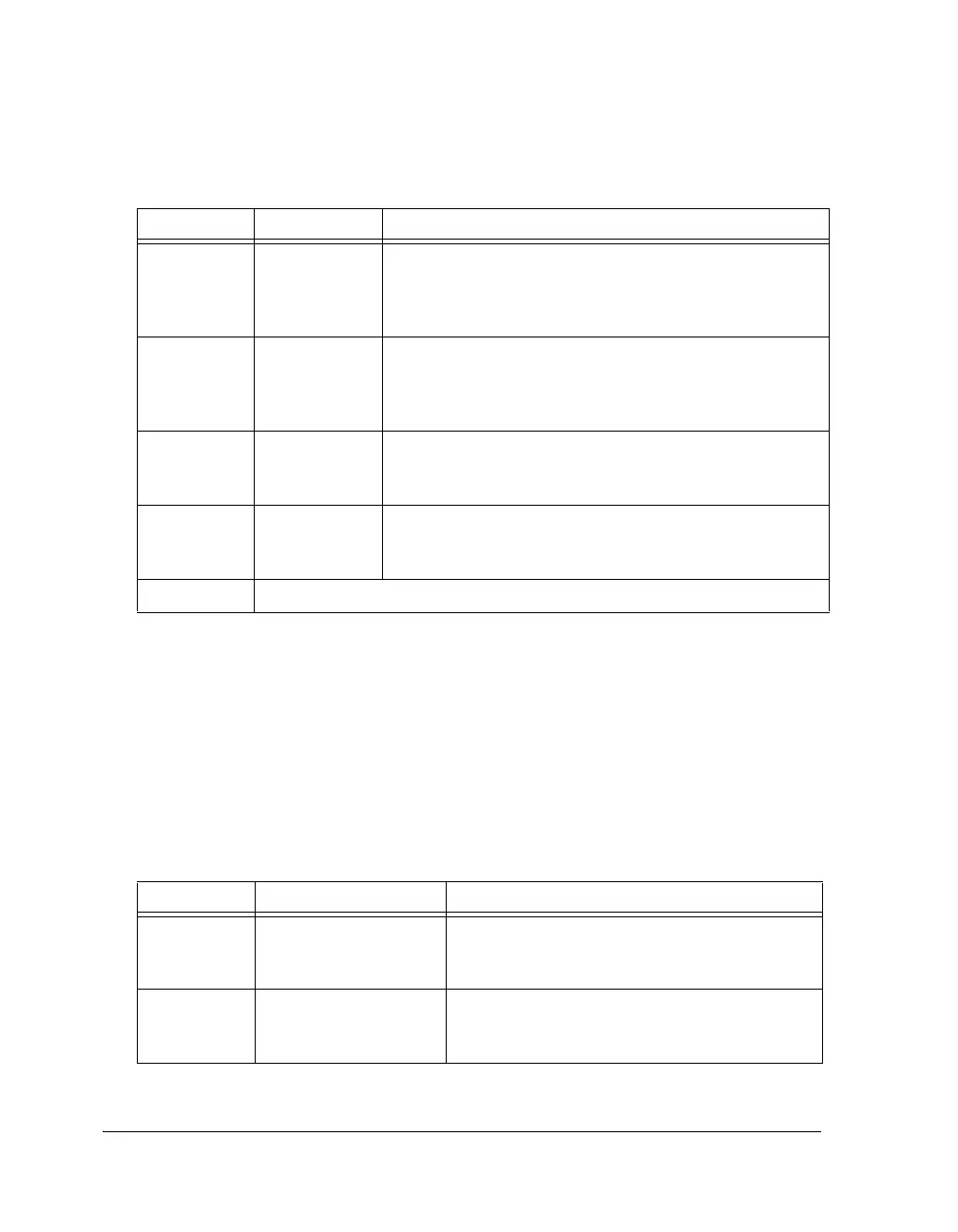

Table A-40. PWMPOLx Register Bit Descriptions (RW)

Bit Name Description

0 PWM_POL1AL Channel AL Polarity 1.

0 = Channel AL polarity 0

1 = Channel AL polarity 1 (default)

1 PWM_POL0AL Channel AL Polarity 0.

0 = Channel AL polarity 0

1 = Channel AL polarity 1 (default)

Table A-39. PWMSEGx Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...