ADSP-214xx SHARC Processor Hardware Reference A-183

Registers Reference

IDP Status Register 1 (DAI_STAT1)

Since the core allows writes to the

IDP_FIFO, the DAI_STAT1 register stores

the different read or writes indexes with a maximum of 8 entries each.

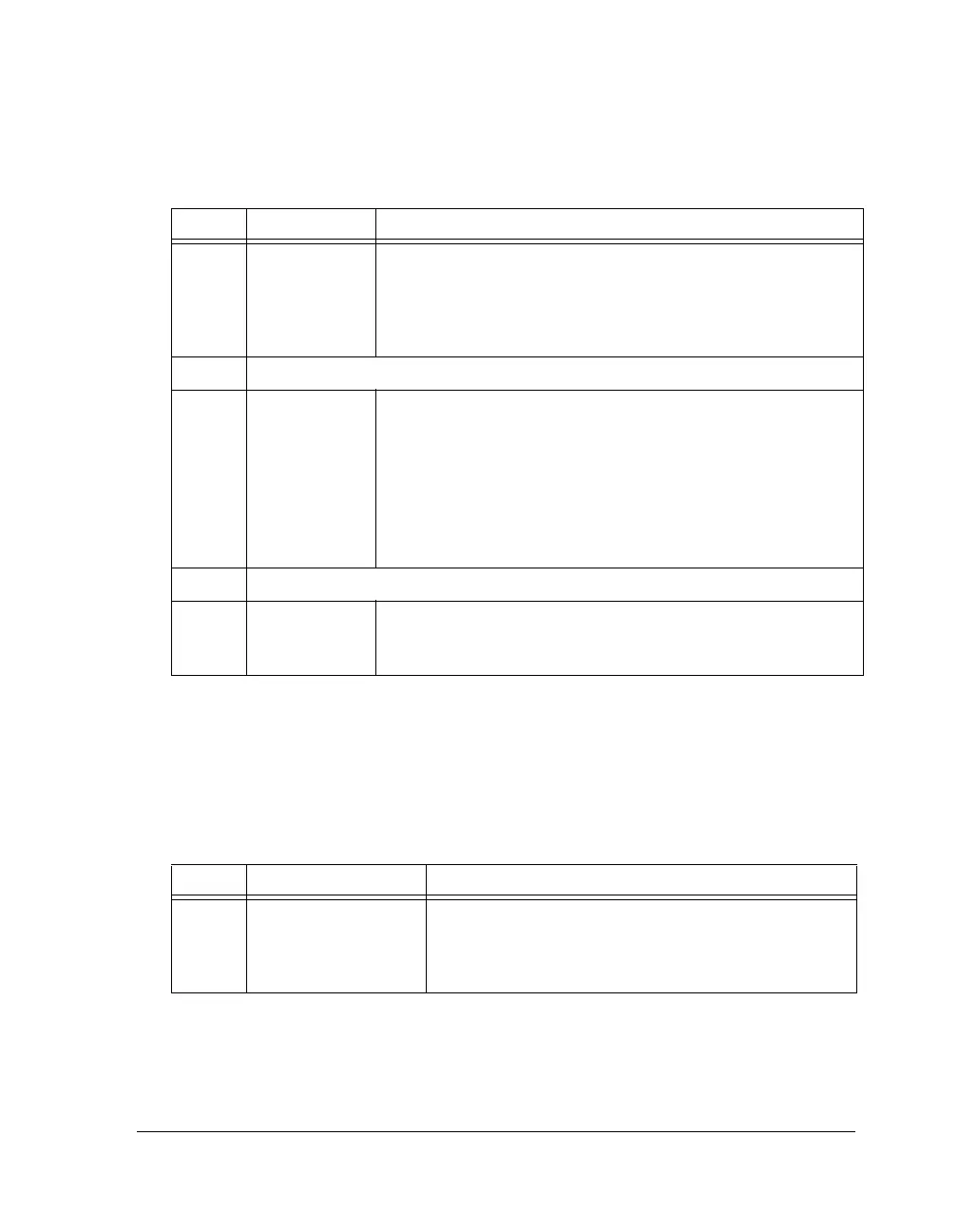

15–8

(Sticky)

SRU_OVFx Sticky Overflow Channel Status. Provides overflow status informa-

tion for each channel (bit 8 for channel 0 through bit 15 for channel

7).

0 = SRU input no overflow

1 = SRU input overflow has occurred

16 Reserved

24–17 IDP_DMAx_ST

AT

Input Data Port DMA Channel Status.

These bits reflect the state of all eight DMA channels. These bits are

set once IDP_DMA_EN is set and remain set until the last data of

that channel is transferred. Even if IDP_DMA_EN is set (=1), this

bit goes low once the required number of data transfers occur. Note

if DMA through some channel is not intended, this bit goes high.

0 = DMA is not active

1 = DMA is active

27–25 Reserved

31–28 IDP_FIFOSZ IDP FIFO Size. Indicates Number of samples in the IDP FIFO.

0000 = IDP FIFO empty

1000 = IDP FIFO full

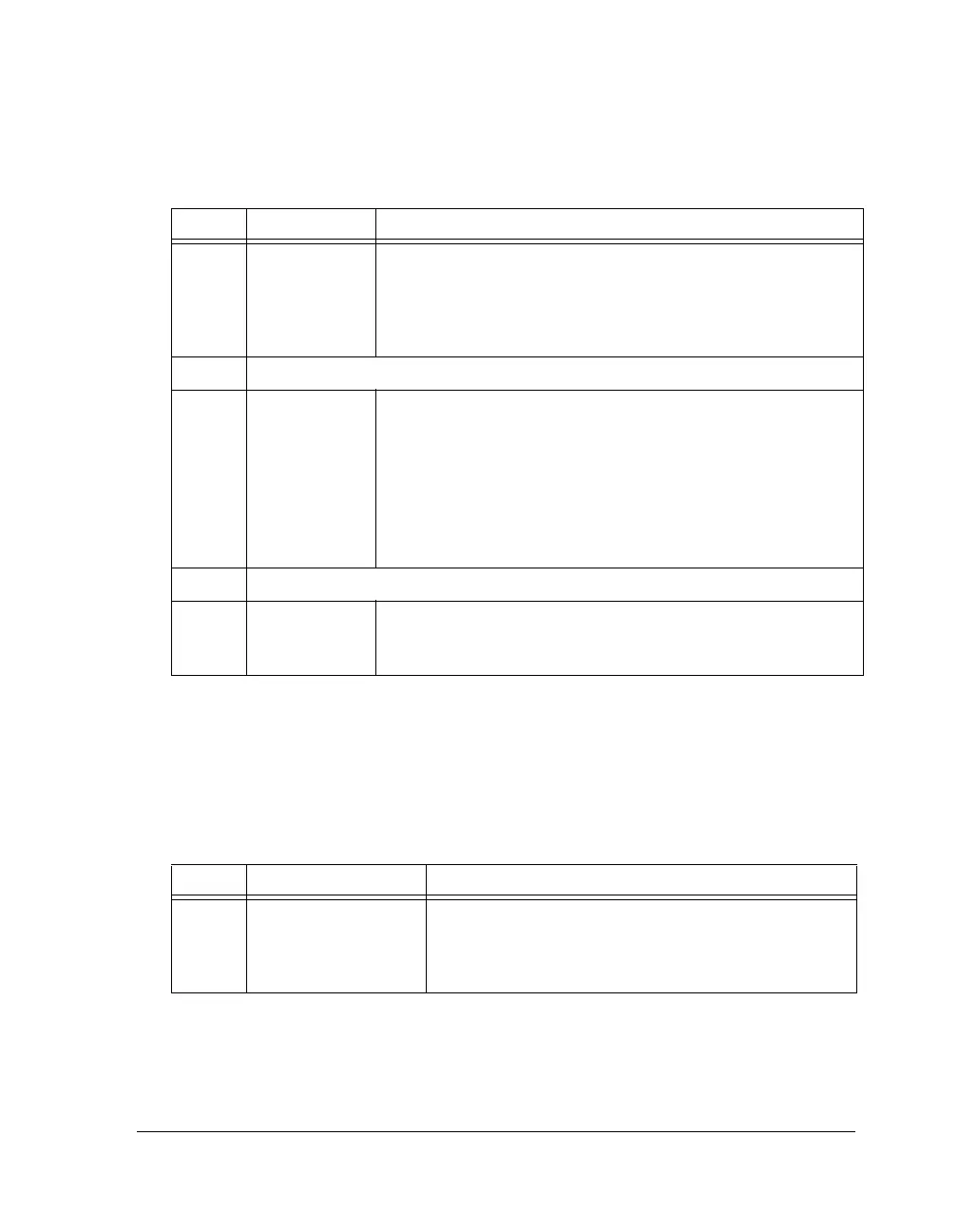

Table A-95. DAI_STAT1 Register Bit Descriptions (RO)

Bit Name Description

3–0 FIFO_WRI Write Index Pointer. Reflects the write index status during

core writes to the IDP_FIFO.

0000 = No write done

1000 = 8 writes done

Table A-94. DAI_STAT0 Register Bit Descriptions (RO) (Cont’d)

Bit Name Description

Loading...

Loading...