External Port Throughput

3-118 ADSP-214xx SHARC Processor Hardware Reference

DDR2 Throughput

The following sections provide information needed to configure the

DDR2 interface for the desired throughput.

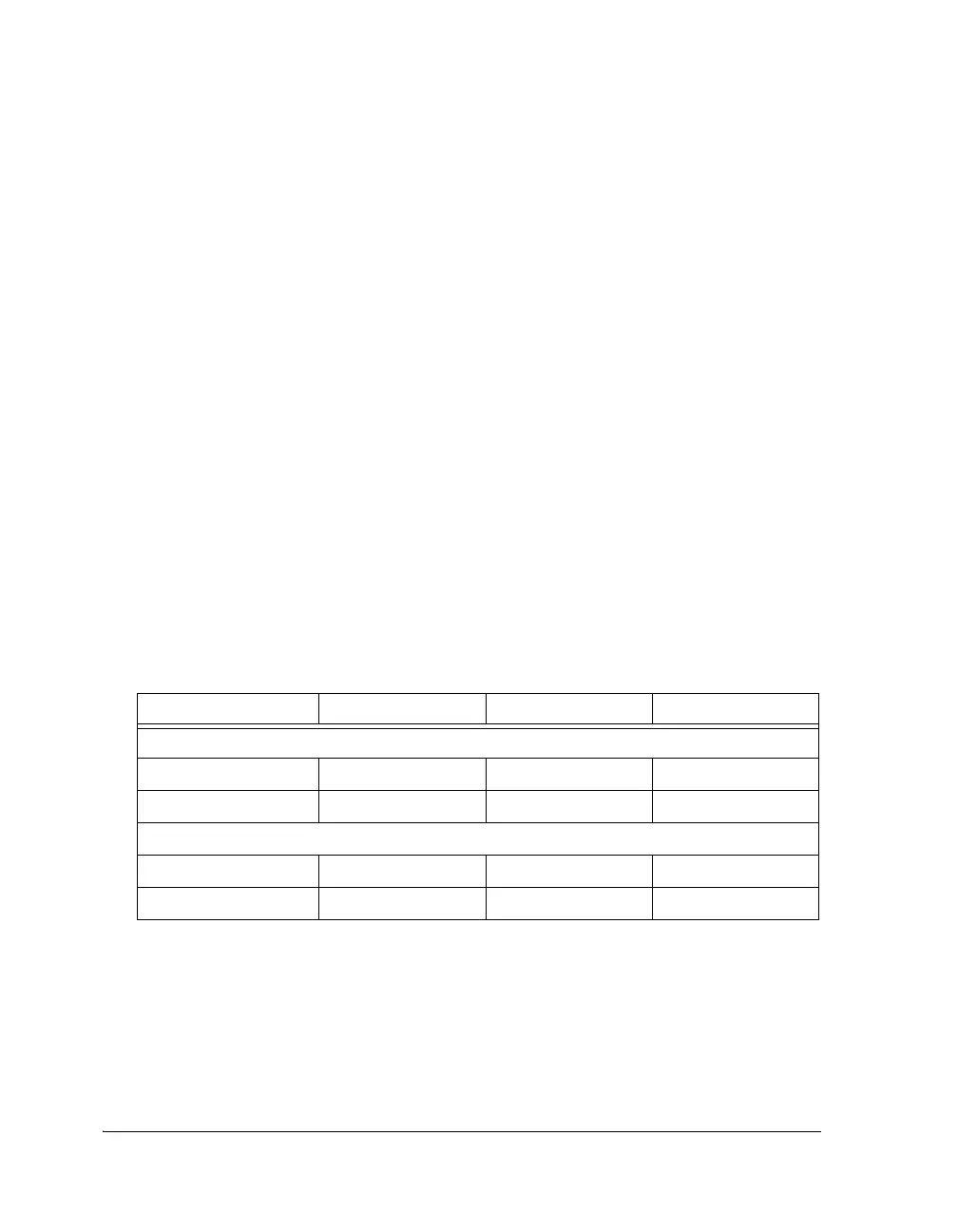

DMA Throughput

Table 3-31 provides approximate throughput information with the pro-

cessor core running at 400 MHz for DMA-driven reads and writes of

external DDR2 memory. The throughput numbers shown are measured

by running chained DMA with four TCBs (with 256 32-bit words per

transfer block).

For the analysis, 16 bit DDR2 is used (t

FAW

=10, t

RRD

=2, t

RTP

=2,

t

MRD

=3, t

RCD

=3, t

WTR

=1, t

RP

=3, t

RAS

=8, CL=4, AL=4, t

WR

=4).

Throughput is calculated by measuring time between the instant when

DMA is enabled and instant when DMA completion ISR is entered.

Core Throughput

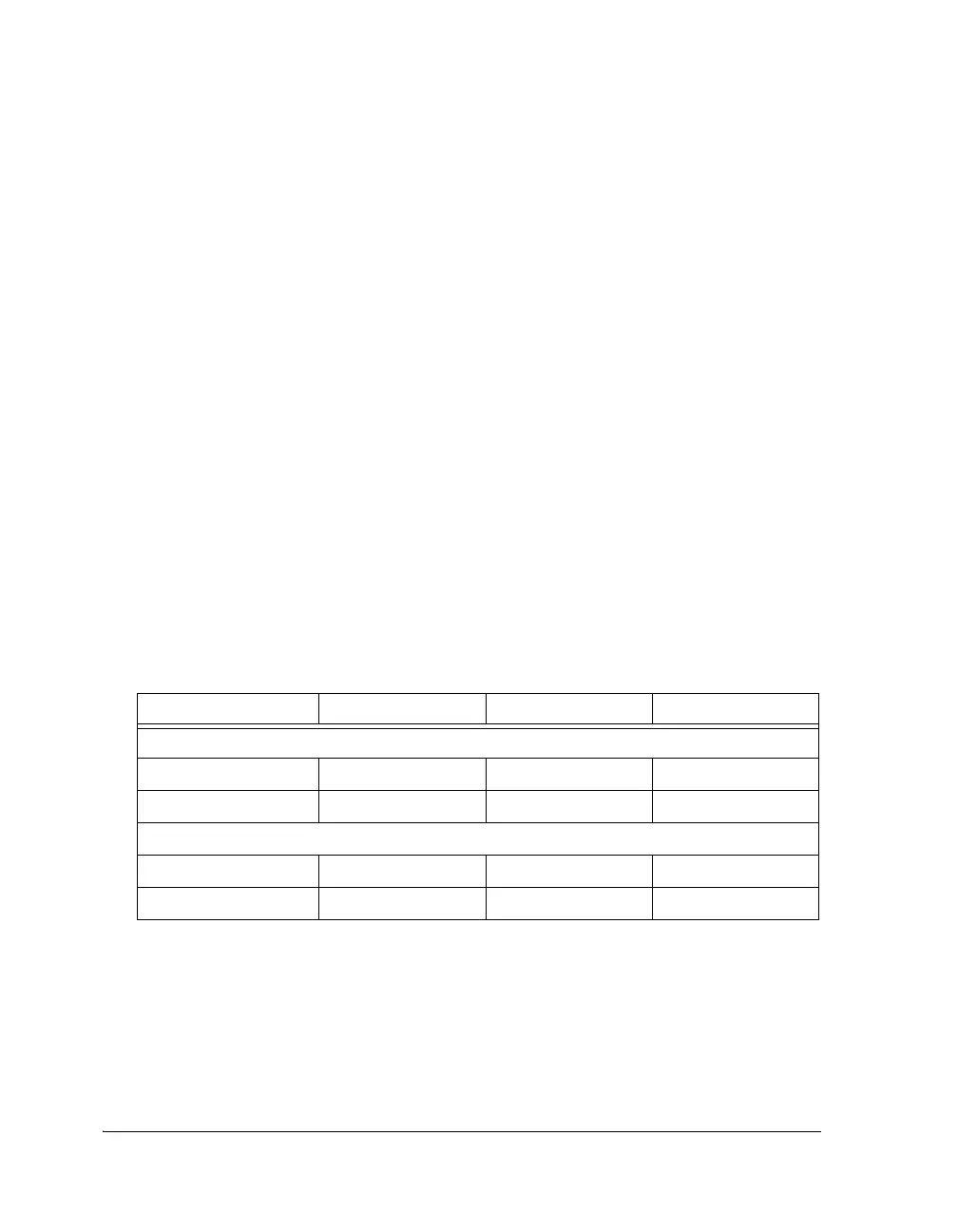

Table 3-32 provides approximate throughput information with the pro-

cessor core running at 400 MHz for core-driven reads and writes of

Table 3-31. DMA Throughput, 400 MHz Core Clock

Operation DDR2 Clock Clock Ratio Throughput

DMA Reads

133 MHz 1:3 473M bytes/sec.

200 MHz 1:2 700M bytes/sec.

DMA Writes

133 MHz 1:3 481M bytes/sec.

200 MHz 1:2 732M bytes/sec.

Loading...

Loading...