ADSP-214xx SHARC Processor Hardware Reference B-7

Peripheral Interrupt Control

Peripherals with Multiple Interrupt Vector

Addresses

The TWI and the UART peripherals have multiple interrupt vector

addresses. Both peripherals are already connected to the P14I (DPI) at

default. However both have another sets of interrupt latches which are not

routed by default. This gives more flexibility to change priority across the

programmable interrupts since the DPI does not support high or low pri-

ority (unlike DAI).

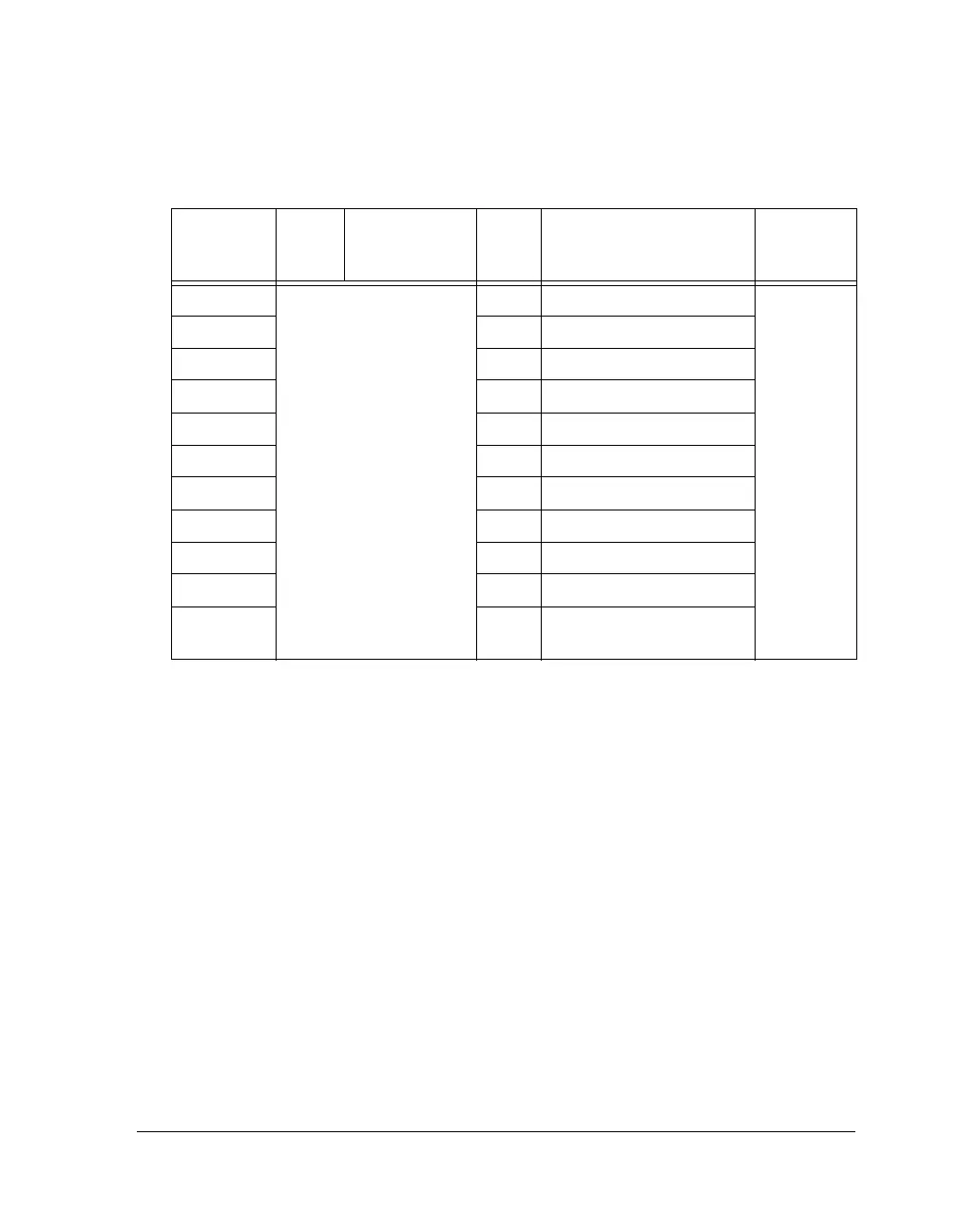

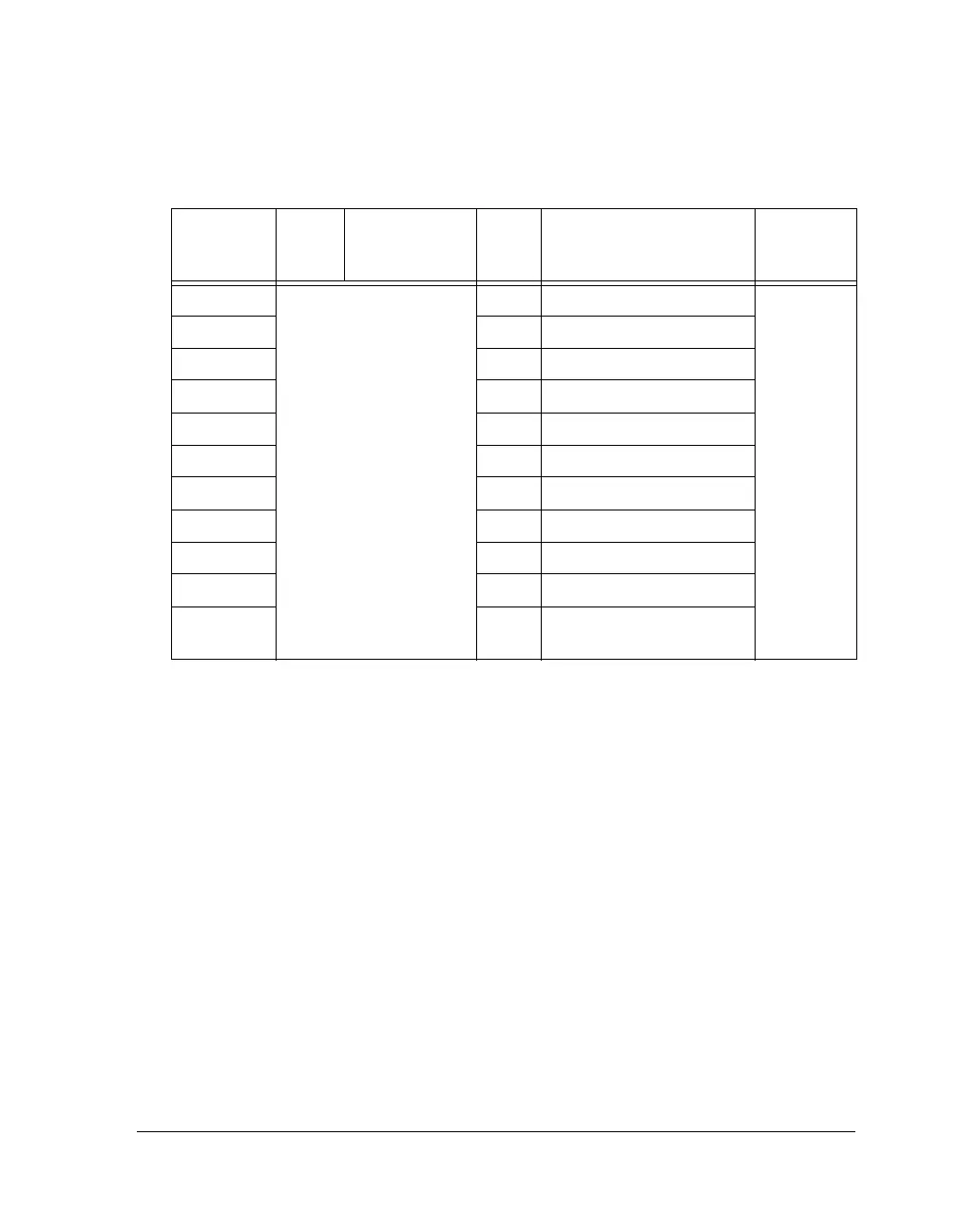

UART0RxI All of these interrupts are

not connected by default.

0x13 UART0 receive interrupt

UART0TxI 0x15 UART0 transmit interrupt

TWII 0x17 Two wire interface interrupt

PWMI 0x18 PWM interrupt

LP0I/RTCI 0x19 Link port 0/RTC interrupt

LP1I 0x1A Link port 1 interrupt

ACC0I 0x1B Accelerator 01 interrupt

ACC1I 0x1C Accelerator 1 interrupt

MLBI 0x1D Media local bus interrupt

Reserved 0x1E Reserved

Logic High

2

0x1F Software option to set IOP

interrupts

1 These interrupts have an option to be unmasked at reset. Therefore, the peripherals that boot

the processor should be allocated these interrupts: (P1I, P9I).

2 Logic high can trigger a software based interrupt on any specific DMA channel (similar to core

SFTxI interrupts).

Table B-2. Peripheral Interrupt Controller Routing Table (Cont’d)

Interrupt

Name

Vecto r

Address

Control Register

(PICR)

Default

Select

Value

Default Function Priority

Loading...

Loading...