Processor Reset

23-4 ADSP-214xx SHARC Processor Hardware Reference

Software Reset

In addition to the hardware reset, there is also support for a software reset,

which is asserted by setting bit 0 of the SYSCTL register.

Running Reset

When running reset is asserted (RESETOUT pin acting as an input and

asserted) and recognized, note the following.

• The core-PLL is NOT reset, and continues to run.

• Internal memory SRAM contents remain unaltered.

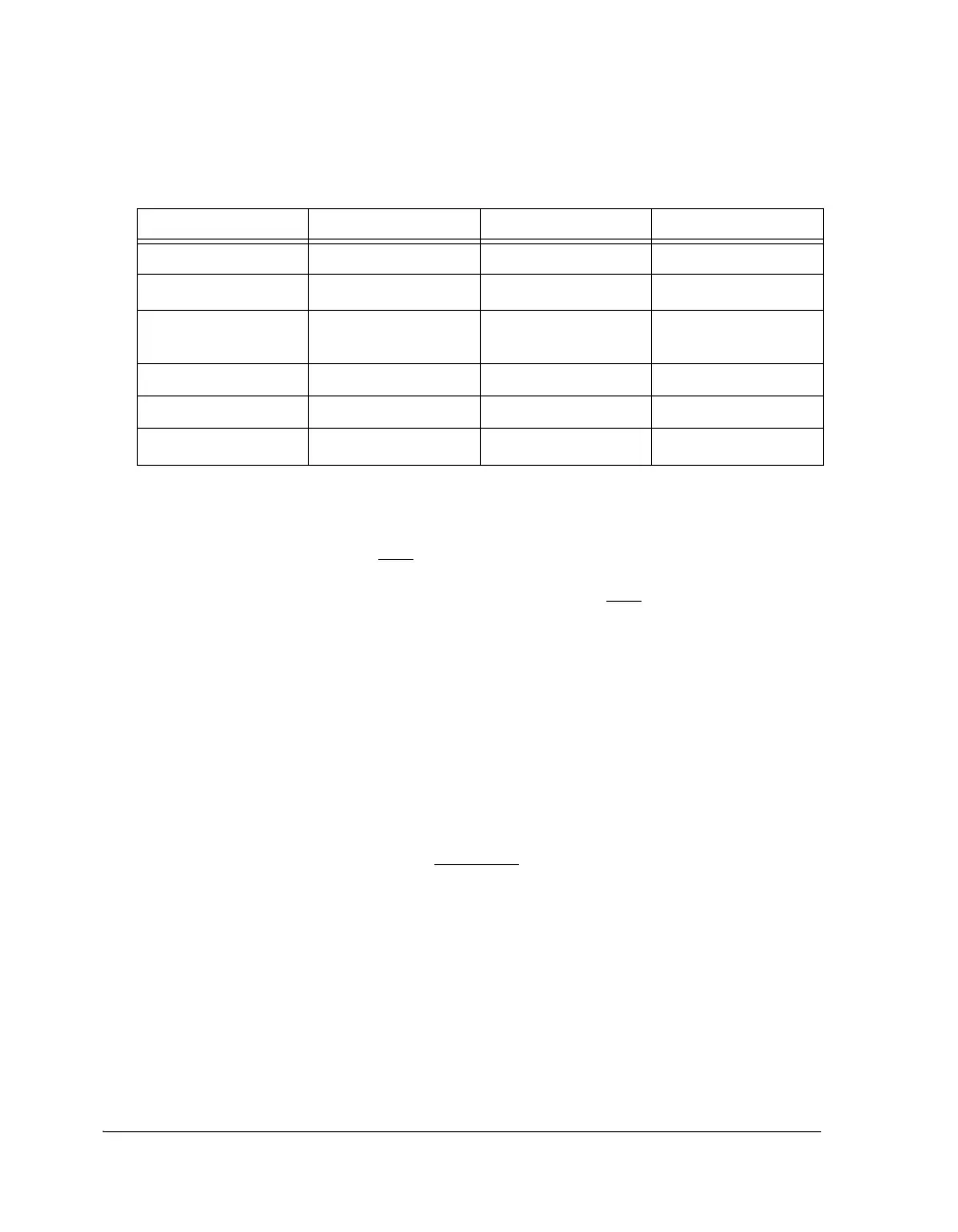

Core Yes Yes Yes

Internal Memory

1

No No No

Peripherals Yes Yes Yes (except

SDRAM/DDR2)

Booting Yes Yes No

Power Management Yes No No

Emulation Unit

2

No No No

1 Internal memory array does not have reset. Only power up/down can change array contents, (or

direct read/write by the core or DMA). However, if data exists in shadow FIFOs then that data

is reset with any of the above resets. The logic outside the memory array is reset by all of the above

three reset types, only the memory array contents remain unchanged.

2 There is an independent reset (

TRST) for the emulation interface. Enhanced Emulation (BTC)

related logic is reset by the three resets types (HW Reset, SW Reset, Running Reset). Further-

more, no other part of the emulator is affected by the reset types.

TRST resets the whole emulator

function, including BTC.

Table 23-1. Reset Function Overview (Cont’d)

Reset Function Hardware Reset Software Reset Running Reset

Loading...

Loading...