System and Power Management Registers

A-6 ADSP-214xx SHARC Processor Hardware Reference

ADSP-2146x Power Management Registers

The registers described in the following sections are specific to the

ADSP-2146x processors.

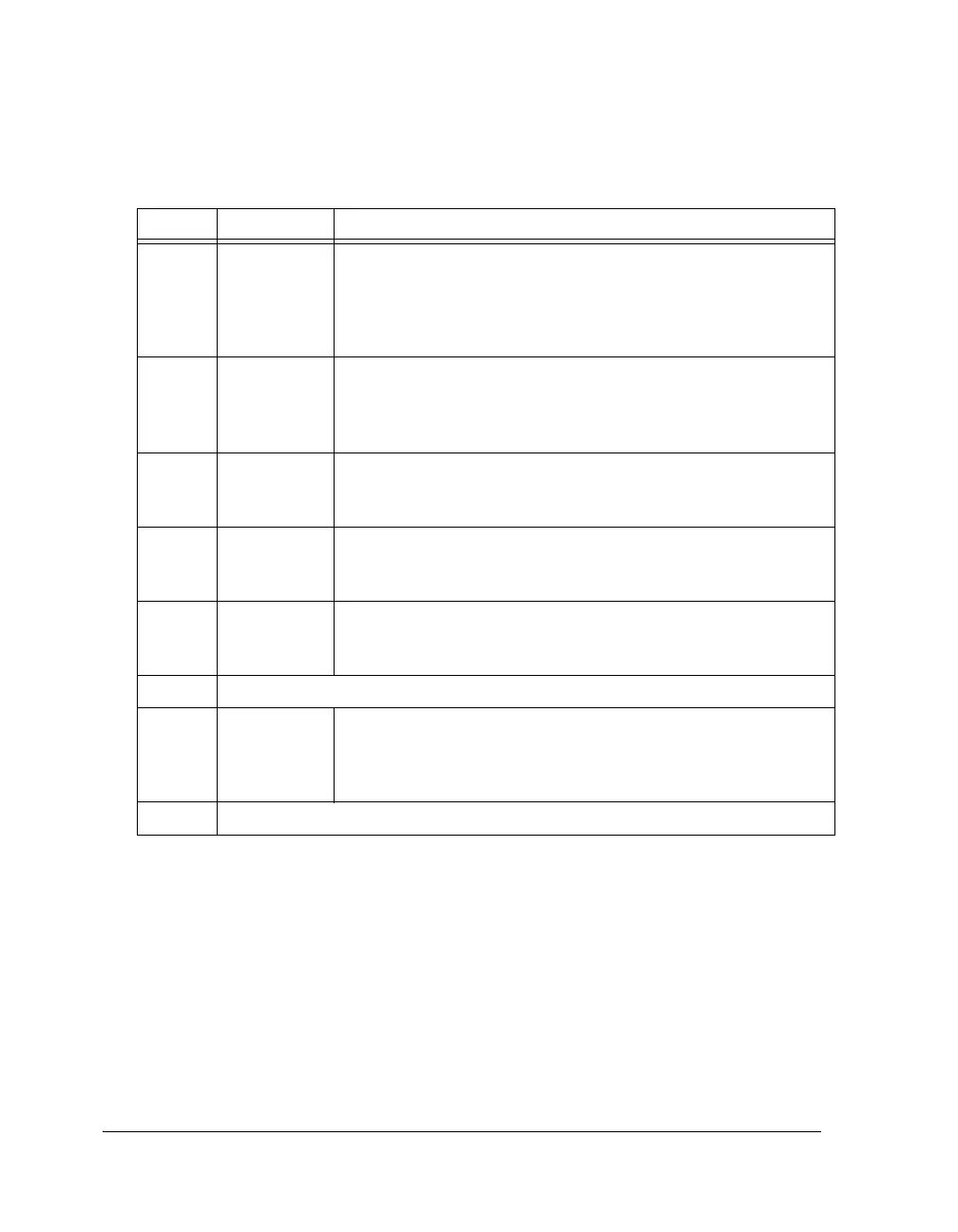

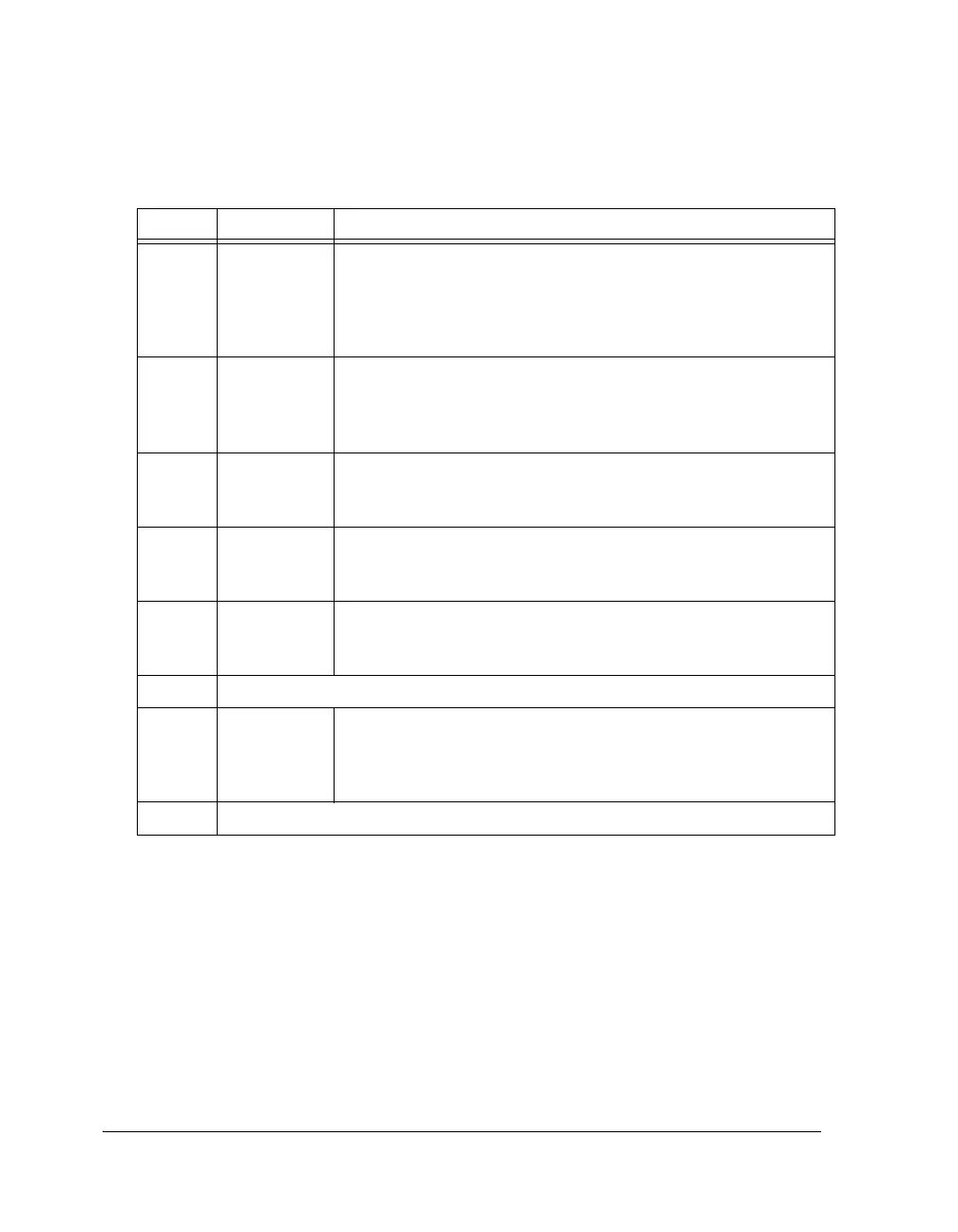

23–21 EPDATA AMI Mode Select.

Selects between multiplexed AMI, Flags, PWM and PDAP interfaces

on the AMI bus.

For detailed programming modes for these bits, see “Multiplexed

External Port Pins” on page 23-30.

24 PWM0EN Pulse Width Modulation Select.

When set (=1), enables PWM3–0. For more information, see “Pin

Multiplexing” on page 23-28. Reserved for ADSP-2147x and

ADSP-2148x.

25 PWM1EN Pulse Width Modulation Select.

When set (=1), enables PWM7–4. For more information, see “Pin

Multiplexing” on page 23-28.

26 PWM2EN Pulse Width Modulation Select.

When set (=1), enables PWM11–8. For more information, see “Pin

Multiplexing” on page 23-28.

27 PWM3EN Pulse Width Modulation Select.

When set (=1), enables PWM15–12. For more information, see “Pin

Multiplexing” on page 23-28.

29–28 Reserved

30 PWMOND-

PIEN

Enable PWM Signals on the DPI Pins. Enables the PWM signals on

DPI pins. When this bit is set (=1), the flags (4–15) which are routed

to the DPI pins can be used as PWM signals. Applicable only for

ADSP-2148x and ADSP-2147x processors.

31 Reserved

Table A-2. SYSCTL Register Bit Descriptions (Cont’d)

Bit Name Description

Loading...

Loading...