ADSP-214xx SHARC Processor Hardware Reference 15-3

Serial Peripheral Interface Ports

• Programmable baud rates, clock polarities, and phases (SPI mode

0–3).

• Master or slave booting from a master SPI device. See “SPI Port

Booting” on page 23-12.

• DMA capability to allow transfer of data without core overhead.

See “DMA Transfers” on page 15-21.

• Internal loopback mode (by connecting

MISO to MOSI).

Note the SPI interface does not support daisy chain operation, where the

MOSI and MISO pins are internally connected through a FIFO, allowing

bypass of data streams.

Pin Descriptions

The SPI protocol uses a 4-wire protocol to enable full-duplex serial com-

munication. Table 15-2 provides detailed pin descriptions and

Figure 15-1 shows the master-slave connections between two devices.

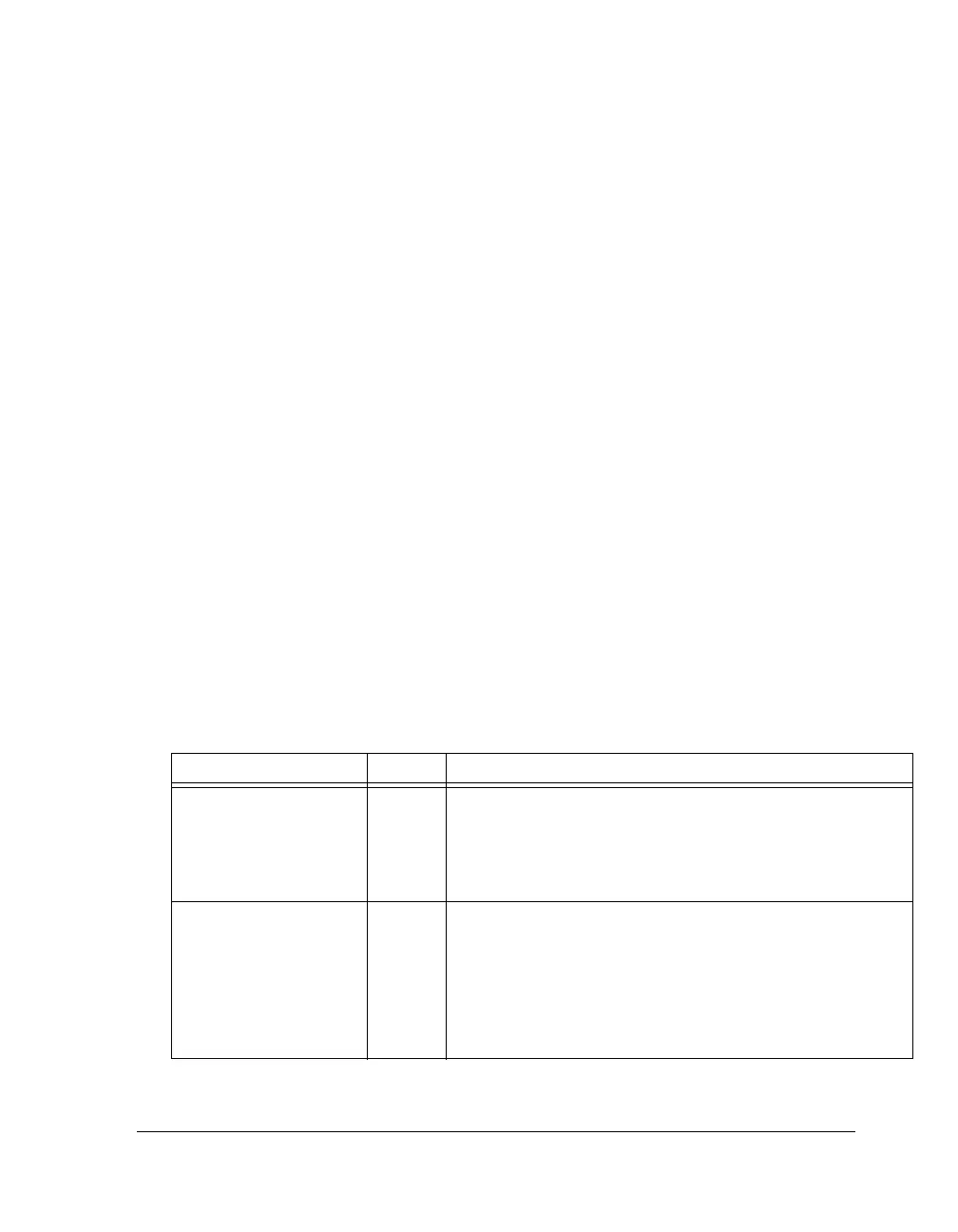

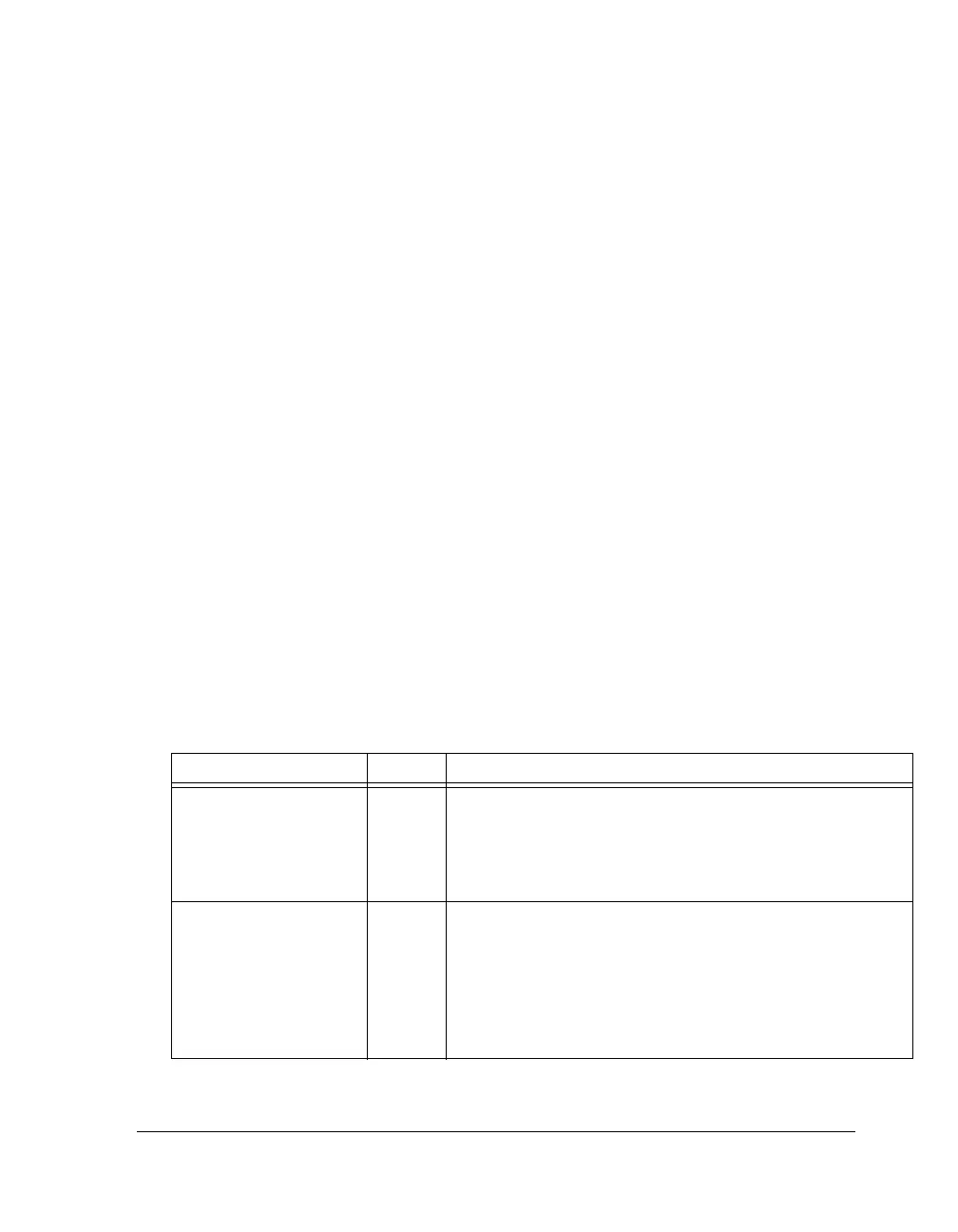

Table 15-2. SPI Pin Descriptions

Internal Node Type Description

SPI_CLK_I/O

SPIB_CLK_I/O

I/O SPI Clock Signal. This control line is clock driven by the master

and regulates the flow of the data bits. The master may transmit

data at a variety of baud rates. The CLK line cycles once for each

bit that is transmitted. It is an output signal if the device is config-

ured as a master; it is an input signal if configured as a slave.

SPI_DS_I

SPIB_DS_I

I SPI Slave Device Select. This is an active-low input signal that is

used to enable slave devices. This signal is like a chip select signal

for the slave devices and is provided by the master device. For a

master device, it can act as an error input signal in a multi-master

environment. In multi-master mode, if the /SPIDS input signal of

a master is asserted (Low) an error has occurred. This means that

another device is also trying to be the master.

Loading...

Loading...