ADSP-214xx SHARC Processor Hardware Reference 15-5

Serial Peripheral Interface Ports

Register Overview

This section provides brief descriptions of the major registers. For com-

plete information see “Serial Peripheral Interface Registers” on

page A-232.

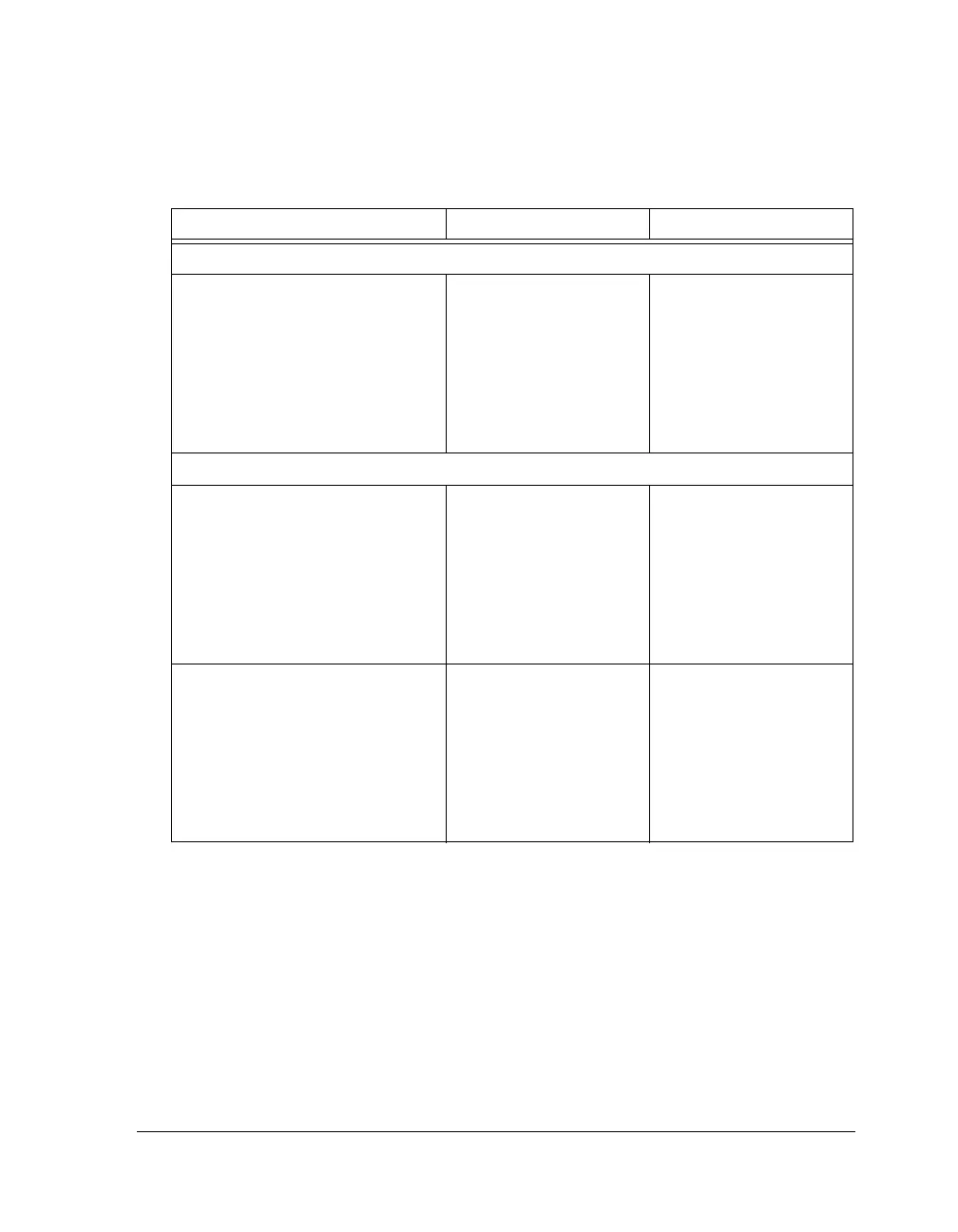

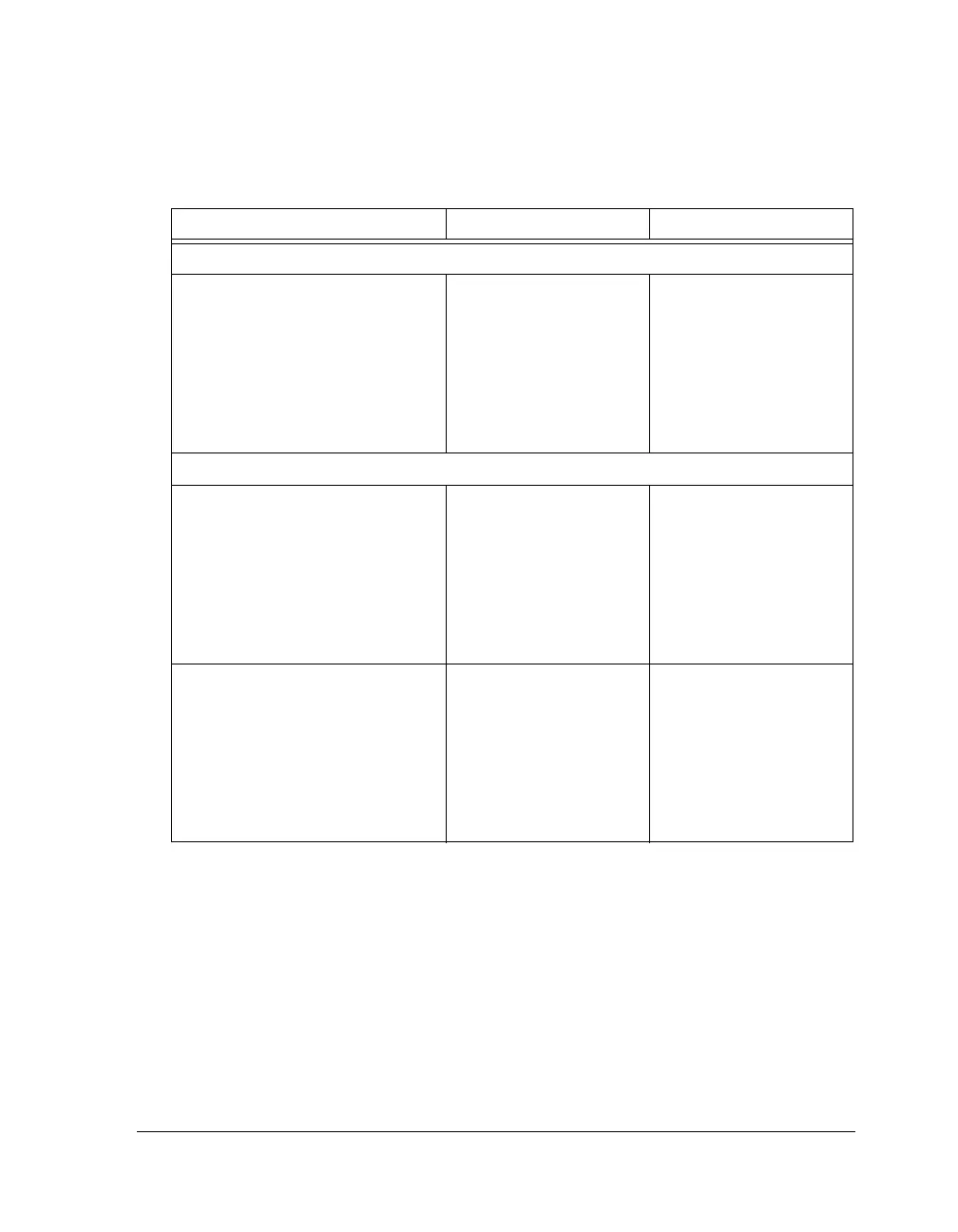

Table 15-3. SPI DPI/SRU2 Signal Connections

Internal Node DPI Group SRU2 Register

Inputs

SPI_CLK_I

SPIB_CLK_I

SPI_DS_I

SPIB_DS_I

SPI_MOSI_I

SPIB_MOSI_I

SPI_MISO_I

SPIB_MISO_I

Group A SRU2_INPUT1–0

Outputs

SPI_CLK_O

SPIB_CLK_O

SPI_MOSI_O

SPIB_MOSI_O

SPI_MISO_O

SPIB_MISO_O

SPI_FLG3–0_O

SPIB_FLG3–0_O

Group B

SPI_CLK_PBEN_O

SPIB_CLK_PBEN_O

SPI_MOSI_PBEN_O

SPIB_MOSI_PBEN_O

SPI_MISO_PBEN_O

SPIB_MISO_PBEN_O

SPI_FLG3–0_PBEN_O

SPIB_FLG3–0_PBEN_O

Group C

Loading...

Loading...