ADSP-214xx SHARC Processor Hardware Reference A-171

Registers Reference

SPORT Active Channel Select Registers (MTxCSy

or MRxCSy)

Each bit, 31–0, set (=1) in one of the four MTxCS0, MTxCS1, MTxCS2, MTxCS3

registers for SPORT0/2/4/6 and

MRxCS0, MRxCS1, MRxCS2, MRxCS3 for

SPORT/1/3/5/7 registers corresponds to the active channel, 127–0, on a

multichannel mode serial port. When these registers activate a channel (by

setting the respective bits in these registers to 1, the serial port transmits or

receives the word in that channel’s position of the data stream. When a

channel’s bit in these registers is cleared (=0), the serial port’s data trans-

mit pin three-states during the channel’s transmit time slot if the serial

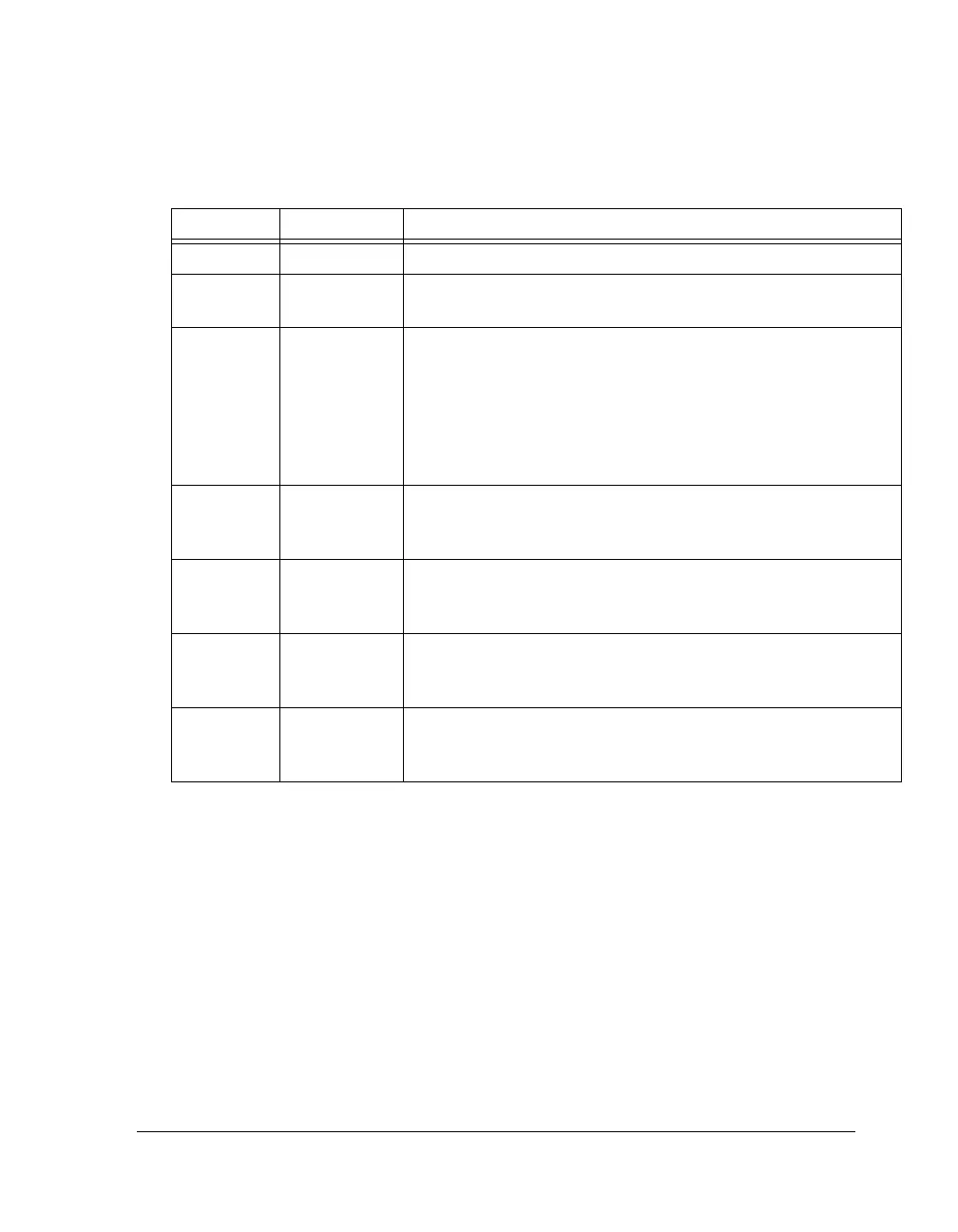

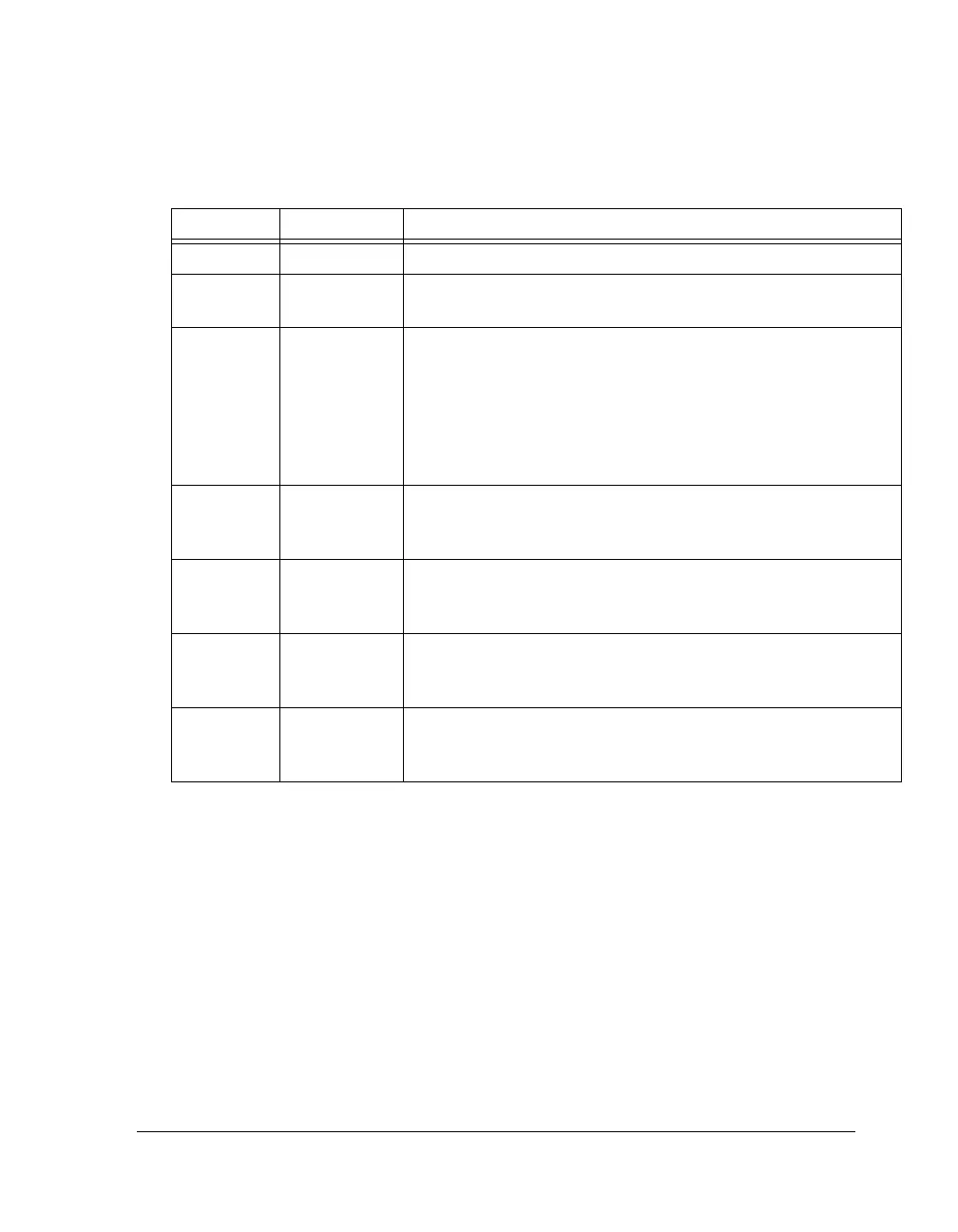

15–13 Reserved

22–16 (RO) CHNL Current Channel Selected. Identify the currently selected transmit

channel slot (0 to 127).

23 MCEB Multichannel B Mode Enable. Packed and multichannel B modes

only. One of two configuration bits that enable and disable multichan-

nel mode on serial port channels. See OPMODE bit (17).

0 = Disable multichannel B operation

1 = Enable multichannel B operation/packed mode

Note if MCEB bit is set, the corresponding SPEN_B bit in the SPCTL

register should be cleared.

25–24 (RO) DMASy DMA y Status. Selects the transfer status.

0 = Inactive

1 = Active

27–26 (RO) DMASx DMA x Status. Selects the transfer status.

0 = Inactive

1 = Active

29–28 (RO) DMACHSy DMA y Chaining Status. Selects the transfer status.

0 = Inactive

1 = Active

31–30 (RO) DMACHSx DMA x Chaining Status. Selects the transfer status.

0 = Inactive

1 = Active

Table A-88. SPMCTLx Register Bit Descriptions (RW) (Cont’d)

Bit Name Description

Loading...

Loading...