ADSP-214xx SHARC Processor Hardware Reference A-209

Registers Reference

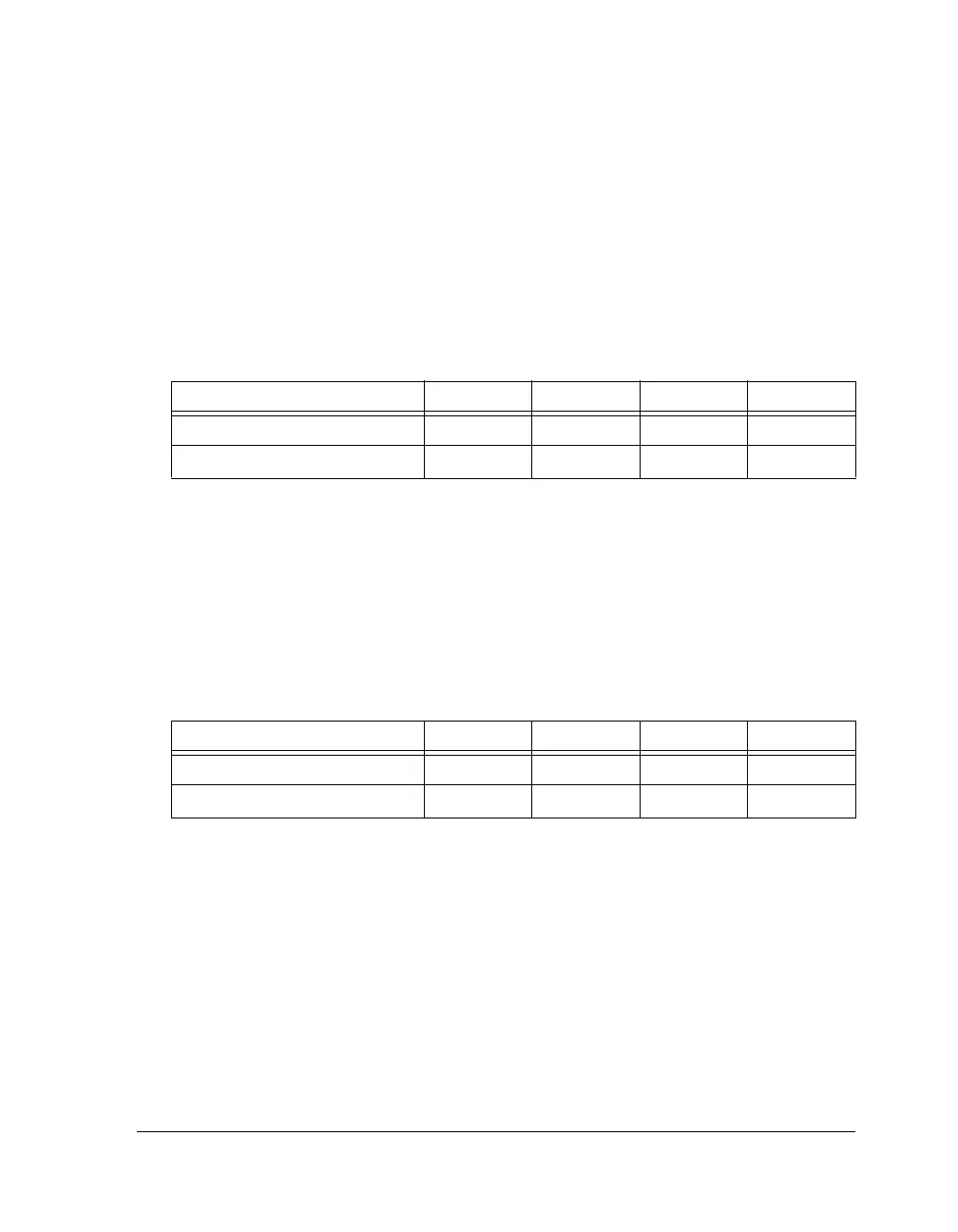

Receive Status Registers for Subframe A

(DIRCHANA)

The S/PDIF receiver stores a maximum of 5 bytes (40-bit) status informa-

tion. Note that status byte 0 is available in the DIRCTL register. This 32-bit

register is described in Table A-111.

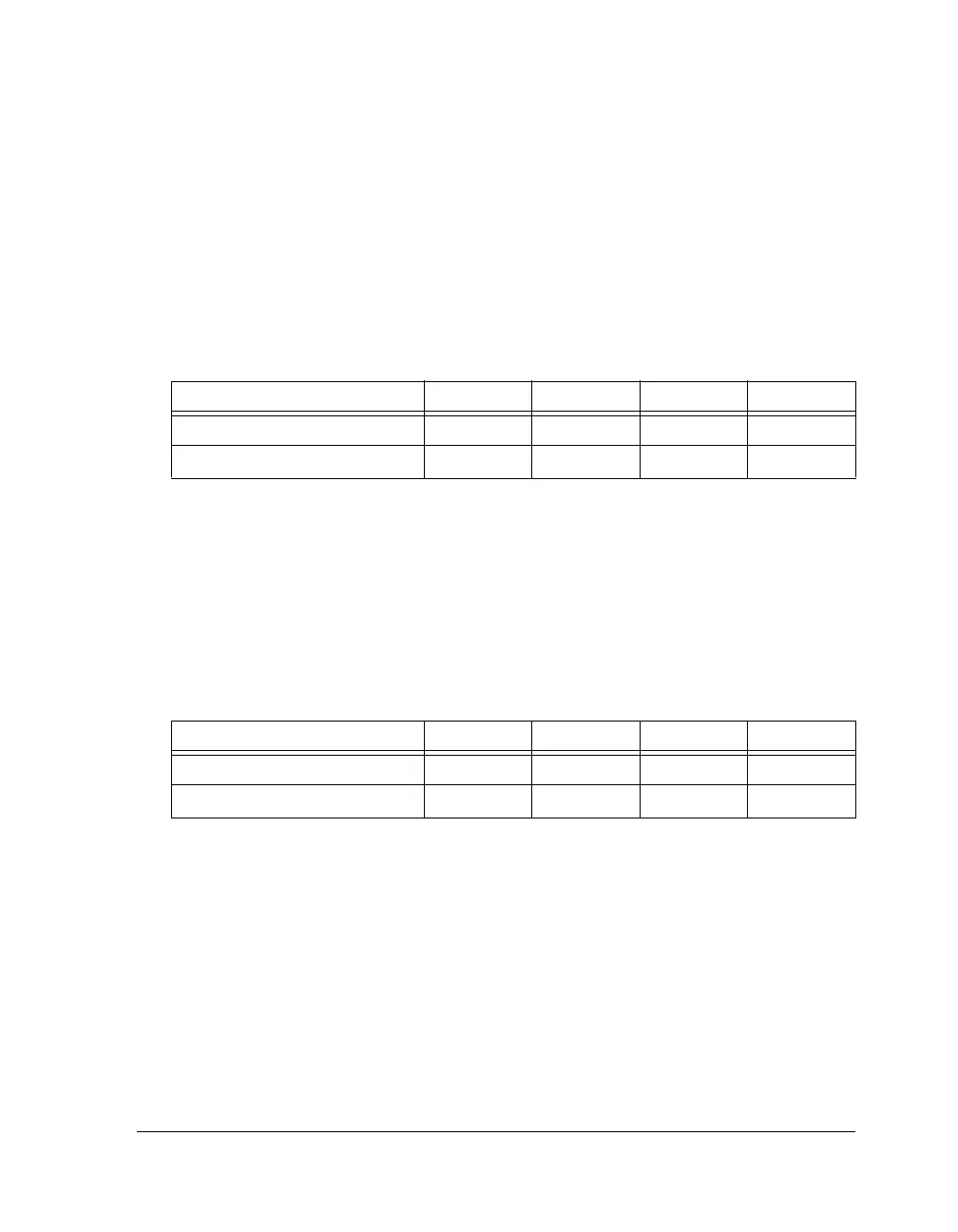

Receive Status Registers for Subframe B

(DIRCHANB)

The S/PDIF receiver stores a maximum of 5 bytes (40-bit) status informa-

tion. Note that status byte 0 is available in the DIRCTL register. This 32-bit

register is described in Table A-112.

Real-Time Clock Registers

The following sections describe the registers associated with the real-time

clock (RTC).

Table A-111. DIRCHANAx Registers (RO)

Register Bits 7–0 Bits 15–8 Bits 23–16 Bits 31–24

DIRSTAT BYTE0

DIRCHANA BYTE1 BYTE2 BYTE3 BYTE4

Table A-112. DIRCHANBx Registers (RO)

Register Bits 7–0 Bits 15–8 Bits 23–16 Bits 31–24

DIRSTAT BYTE0

DIRCHANB BYTE1 BYTE2 BYTE3 BYTE4

Loading...

Loading...